NÚCLEO IP, ARQUITECTURA QUE COMPRENDE UN NÚCLEO IP Y PROCEDIMIENTO DE DISEÑO DE UN NÚCLEO IP.

Un núcleo IP configurable y programable de procesamiento para la computación de una pluralidad de productos matriciales,

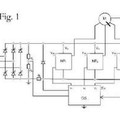

en el que tanto los datos a procesar como los resultados obtenidos se transfieren en serie, que comprende: El núcleo IP comprende:un bloque de entrada de datos para proporcionar un conjunto de vectores que representan una primera y una segunda matriz cuyo producto se quiere computar, donde dicho bloque de entrada de datos comprende: un primer sub-bloque y un segundo sub-bloque; un bloque de memoria que comprende N elementos de memoria asociados a una salida respectiva de dicho segundo sub-bloque del bloque de entrada de datos; un bloque multiplicador matriz-vector en coma fija para implementar una operación de multiplicación-acumulación; un bloque que comprende al menos una función de activación configurada para ser aplicada a la salida de dicho bloque multiplicador matriz-vector en coma fija; un bloque para almacenar las salidas de la al menos una función de activación y para leer las salidas de dichos componentes de almacenamiento; un bloque FIFO y un bloque de salida de datos que comprende un contador de fila y un contador de columna. Sistema en chip que comprende al menos un núcleo IP.FPGA que comprende al menos un núcleo IP. Procedimiento de diseño de un núcleo IP.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/ES2018/070526.

Solicitante: UNIVERSIDAD DEL PAÍS VASCO - EUSKAL HERRIKO UNIBERTSITATEA (UPV/EHU).

Nacionalidad solicitante: España.

Inventor/es: MARTÍNEZ CORRAL,Unai, BASTERRECHEA OYARZABAL,Koldobika.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06N3/063 FISICA. › G06 CALCULO; CONTEO. › G06N SISTEMAS DE COMPUTADORES BASADOS EN MODELOS DE CALCULO ESPECIFICOS. › G06N 3/00 Sistemas de computadores basados en modelos biológicos. › utilizando medios electrónicos.

Patentes similares o relacionadas:

Red y método para sistemas informáticos escalables accionados por eventos, del 8 de Julio de 2020, de UNIVERSITAT ZURICH: Una red que comprende una pluralidad de circuitos de núcleo interconectados , en la que cada circuito de núcleo comprende: - una matriz […]

Sistema de red neuronal artificial de tipo asincrónico, del 10 de Julio de 2019, de THE UNIVERSITY OF BATH: Un sistema de red neuronal artificial asíncrono que comprende una pluralidad de neuronas, cada una de las cuales se utiliza para recibir señales de entrada que representan […]

AMPLIFICADOR PARA VARIADOR DE FRECUENCIA, del 25 de Octubre de 2012, de RUANO MOYANO, José: Variador de frecuencia.

La presente invención propone un variador de frecuencia para motor eléctrico. Este variador se caracteriza por el hecho […]

AMPLIFICADOR PARA VARIADOR DE FRECUENCIA, del 25 de Octubre de 2012, de RUANO MOYANO, José: Variador de frecuencia.

La presente invención propone un variador de frecuencia para motor eléctrico. Este variador se caracteriza por el hecho […]

COMPONENTE DE UNA RED NEURONAL, del 12 de Mayo de 2010, de THE VICTORIA UNIVERSITY OF MANCHESTER: Un componente de una red neuronal, comprendiendo el componente una pluralidad de entradas , al menos un elemento procesador , al menos una salida , y una […]

COMPONENTE DE UNA RED NEURONAL, del 12 de Mayo de 2010, de THE VICTORIA UNIVERSITY OF MANCHESTER: Un componente de una red neuronal, comprendiendo el componente una pluralidad de entradas , al menos un elemento procesador , al menos una salida , y una […]

ELEMENTO DE PROCESAMIENTO NEURONAL PAR AUTILIZAR EN UNA RED NEURONAL., del 16 de Junio de 2006, de AXEON LIMITED: Un elemento de tratamiento neural destinado a ser utilizado en una red neural, cuyo elemento de tratamiento comprende: - medios lógicos […]