Procesador digital de señales y dispositivo de comunicación de banda base.

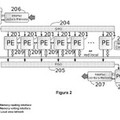

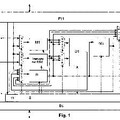

Una unidad de ejecución de vectores (203, 205, 520, 530) para su uso en un procesador digital de señales (200) que tiene un núcleo de procesador,

dicho núcleo comprendiendo una memoria de programa dispuesta para contener instrucciones para una pluralidad de unidades de ejecución, el procesador digital de señales comprendiendo adicionalmente una pluralidad de unidades de memoria de datos dispuestas para contener datos para ser usados por la unidad de ejecución de vectores, el núcleo, la unidad de ejecución de vectores y las unidades de memoria de datos estando interconectadas por una red (244), dicha unidad de ejecución de vectores estando dispuesta para ejecutar instrucciones, incluyendo instrucciones vectoriales que deben realizarse en datos múltiples en forma de un vector, comprendiendo un registro de instrucciones (722) dispuesto para recibir y almacenar instrucciones, un decodificador de instrucciones (723) dispuesto para decodificar instrucciones almacenadas en el registro de instrucciones, y por lo menos una ruta de datos controlada por el decodificador de instrucciones, dicha unidad de ejecución de vectores comprendiendo además un controlador de vectores (720, 720') y un registro de recuento (721), dicho controlador de vectores estando dispuesto para determinar si una instrucción es una instrucción vectorial y , si lo es, informar al registro de recuento (721), que está dispuesto para contener la longitud del vector, dicho controlador de vectores (720, 720') estando además dispuesto para controlar la ejecución de instrucciones, dicha unidad de ejecución de vectores estando además caracterizado porque

- comprende una cola local (730) dispuesta para recibir por lo menos una primera y una segunda instrucciones de la memoria del programa, para proporcionar la primera instrucción al registro de instrucciones (722) y para contener la segunda instrucción en la cola local (730) hasta que se cumple una condición predefinida, y porque

- el controlador de vectores (720, 720') comprende un medio de control de cola (732, 721) dispuesto para controlar la cola local.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/SE2012/050979.

Solicitante: MediaTek Sweden AB.

Nacionalidad solicitante: Suecia.

Dirección: Teknikringen 10 583 30 Linköping SUECIA.

Inventor/es: NILSSON, ANDERS.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F15/80 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 15/00 Computadores digitales en general (detalles G06F 1/00 - G06F 13/00 ); Equipo de procesamiento de datos en general. › que comprenden un conjunto de unidades de procesamiento con control común, p. ej. varios procesadores de datos de instrucción única (G06F 15/82 tiene prioridad).

- G06F9/30 G06F […] › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Disposiciones para ejecutar instrucciones de máquinas, p. ej. decodificación de instrucciones (para ejecutar microinstrucciones G06F 9/22).

- G06F9/38 G06F 9/00 […] › Ejecución simultánea de instrucciones, p. ej. segmentación, anticipación.

PDF original: ES-2688603_T3.pdf

Patentes similares o relacionadas:

Procesador digital de señales y método para direccionar una memoria en un procesador digital de señales, del 18 de Octubre de 2017, de MediaTek Sweden AB: Un procesador digital de señales que comprende al menos una unidad funcional, que puede ser una unidad de ejecución de vectores , o un acelerador, […]

Procesador de señal digital y dispositivo de comunicación de banda base, del 16 de Agosto de 2017, de MediaTek Sweden AB: Un procesador de señal digital que comprende: - un núcleo de procesador que incluye una unidad de ejecución de enteros […]

Arquitectura híbrida SIMD/MIMD dinámicamente reconfigurable de un coprocesador para sistemas de visión, del 4 de Julio de 2013, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), dinámicamente […]

Arquitectura híbrida SIMD/MIMD dinámicamente reconfigurable de un coprocesador para sistemas de visión, del 4 de Julio de 2013, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), dinámicamente […]

ARQUITECTURA HÍBRIDA SIMD/MIMD DINÁMICAMENTE RECONFIGURABLE DE UN COPROCESADOR PARA SISTEMAS DE VISIÓN, del 29 de Noviembre de 2012, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), […]

ARQUITECTURA HÍBRIDA SIMD/MIMD DINÁMICAMENTE RECONFIGURABLE DE UN COPROCESADOR PARA SISTEMAS DE VISIÓN, del 29 de Noviembre de 2012, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), […]

Dispositivo de direccionamiento para procesador paralelo, del 15 de Agosto de 2012, de THALES: Procesador paralelo que comprende procesadores elementales que comprenden cada uno al menos unaunidad de cálculo y al menos una memoria que incluye palabras […]

SISTEMA DE PROCESAMIENTO DE DATOS Y DISPOSITIVO DE COMPUTACIÓN, del 12 de Marzo de 2012, de STARLAB BARCELONA SL: Sistema de procesamiento de datos y dispositivo de computación.

El sistema comprende:

- unos dispositivos de computación que procesan en paralelo […]

SISTEMA DE PROCESAMIENTO DE DATOS Y DISPOSITIVO DE COMPUTACIÓN, del 12 de Marzo de 2012, de STARLAB BARCELONA SL: Sistema de procesamiento de datos y dispositivo de computación.

El sistema comprende:

- unos dispositivos de computación que procesan en paralelo […]

REDES NEURONALES., del 1 de Enero de 2004, de BRITISH AEROSPACE: Dispositivo para tratar datos que representan una pluralidad de ejemplos, con lo que se determina una plantilla genérica que representa dichos ejemplos, donde dicho dispositivo […]

APARATO Y METODO PARA PROCESAR DATOS ENCAUZADOS, del 27 de Mayo de 2010, de XELERATED AB: Método de procesamiento encauzado, que comprende una pluralidad de fases (9a-9e) de procesamiento encauzado, caracterizado por las etapas de:

recibir un […]

APARATO Y METODO PARA PROCESAR DATOS ENCAUZADOS, del 27 de Mayo de 2010, de XELERATED AB: Método de procesamiento encauzado, que comprende una pluralidad de fases (9a-9e) de procesamiento encauzado, caracterizado por las etapas de:

recibir un […]