APARATO Y METODO PARA PROCESAR DATOS ENCAUZADOS.

Método de procesamiento encauzado, que comprende una pluralidad de fases (9a-9e) de procesamiento encauzado,

caracterizado por las etapas de:

recibir un bloque (4) de datos en una primera unidad (11) lógica en un medio (3) de procesamiento;

consultar una primera instrucción (13a) correspondiente a un primer contador (7a) de programa, asociado con el bloque (4) de datos en una primera tabla (12a) de instrucciones que comprende al menos la primera instrucción (13a);

ejecutar al menos una operación asociada con la primera instrucción (13a) en la primera unidad (11) lógica;

crear en la primera unidad (11) lógica un segundo contador (7b) de programa, asociado con el bloque (4) de datos,

recibir el bloque (4) de datos en una segunda unidad (14) lógica en el medio (3) de procesamiento;

consultar una instrucción (13f) adicional correspondiente al segundo contador (7b) de programa en una segunda tabla (12b) de instrucciones que comprende al menos la instrucción (13f) adicional; y

ejecutar al menos una operación asociada con la instrucción (13f) adicional en la segunda unidad (14) lógica

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/SE01/01134.

Solicitante: XELERATED AB.

Nacionalidad solicitante: Suecia.

Dirección: OLOF PALMES GATA 29,111 22 STOCKHOLM.

Inventor/es: SVENSSON,LARS-OLOV, ROOS,JOACHIM, STRIMQVIST,THOMAS, WESTLUND,PAR, HOLM,PETER.

Fecha de Publicación: .

Fecha Concesión Europea: 31 de Marzo de 2010.

Clasificación Internacional de Patentes:

- G06F15/78V

Clasificación PCT:

- G06F15/80 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 15/00 Computadores digitales en general (detalles G06F 1/00 - G06F 13/00 ); Equipo de procesamiento de datos en general. › que comprenden un conjunto de unidades de procesamiento con control común, p. ej. varios procesadores de datos de instrucción única (G06F 15/82 tiene prioridad).

Clasificación antigua:

- G06F15/80 G06F 15/00 […] › que comprenden un conjunto de unidades de procesamiento con control común, p. ej. varios procesadores de datos de instrucción única (G06F 15/82 tiene prioridad).

Fragmento de la descripción:

Aparato y método para procesar datos encauzados.

Campo técnico de la invención

La presente invención se refiere a un método para procesar datos encauzados, a un medio de procesamiento para datos encauzados, a un módulo para procesar datos encauzados, a un circuito integrado y a una unidad de orde- nador.

Descripción de la técnica relacionada

Muchos procesadores usan una técnica denominada encauzamiento o procesamiento encauzado, en la que los procesadores empiezan a ejecutar una segunda instrucción antes de que se haya completado una primera instrucción. Esto es, varias instrucciones están en una "segmentación de cauce" simultáneamente, cada una en una fase de procesamiento diferente. La segmentación de cauce está dividida en fases, es decir, segmentos, y cada fase puede ejecutar sus operaciones, es decir, acciones definidas asociadas con una instrucción, de forma concurrente con las otras fases. Cuando una fase completa una operación, pasa el resultado a la siguiente fase en la segmentación de cauce y obtiene la siguiente operación de la fase anterior. Los resultados finales de cada instrucción emergen al final de la segmentación de cauce en sucesión rápida.

No sólo los microprocesadores de alto rendimiento y basados en RISC (Reduced Instruction Set Computer, ordenador de conjunto de instrucciones reducidas) usan encauzamiento de instrucciones. El RISC proporciona una alta capacidad de programación para las instrucciones realizadas por el microprocesador y mayores demandas respecto al software que para microprocesadores basados en CISC (Complex Instructíon Set computer, ordenador de conjunto de instrucciones complejas). Aunque los microprocesadores basados en RISC tienen una frecuencia de reloj más rápida que los microprocesadores basados en CISC, son más lentos para determinados propósitos especiales, para los que puede configurarse un CISC. Sin embargo, en general para propósitos especiales, tanto los RISC como los CISC son más lentos que un ASIC (Aplication Specific Integrated Circuit, circuito integrado de aplicación especifica), ya que el ASIC está adaptado especialmente para un propósito especifico. Puesto que el ASIC está optimizado para un trabajo predeterminado especifico, tiene la desventaja de no estar adaptado para otros propósitos y de este modo carece de la flexibilidad de los microprocesadores de propósito general.

El documento US-6157955-A da a conocer una plataforma de procesamiento de paquetes programable de propósito general para acelerar aplicaciones de infraestructura de red. La aceleración se consigue, por ejemplo, dividiendo las etapas del procesamiento de paquetes en una multitud de fases de segmentación de cauce y proporcionando motores de clasificación especializados adaptados y un microprocesador de propósito general, denominado un procesador de política, para ejecutar las acciones arbitrarias deseadas por determinadas aplicaciones. Sin embargo, el procesador de política tiene que realizar la acción deseada antes de que pueda empezar una ejecución de una acción solicitada subsiguiente.

Sumario

Es un objeto general de la presente invención proporcionar una arquitectura de ordenador que, para aplicaciones especificas, permita una ejecución de instrucciones más rápida que en general microprocesadores basados en RISC y CISC y que sea más flexible que un ASIC respecto a la capacidad de programación.

La presente invención proporciona por lo tanto un método para procesamiento encauzado según la reivindicación 1.

El primer contador de programa es una variable usada para hacer un seguimiento de la dirección de la siguiente instrucción.

Consultar significa seleccionar dentro de una tabla predefinida de valores (serie, matriz, etc.).

De este modo se consigue que cada fase en el procesamiento encauzado de bloques entrantes se asocie con una tabla de instrucciones, en la que puede editarse una instrucción especificada para una aplicación de modo que se configura de forma adaptada cada fase para una aplicación específica.

De manera adecuada, la al menos una fase de procesamiento encauzado comprende la etapa de:

Preferiblemente, antes de la fase o fases anteriormente mencionadas, el método comprende las etapas de:

De este modo se consigue una fase de clasificación antes de la fase de procesamiento, en la que el al menos un argumento y el primer contador de programa, que pueden ser diferentes para cada tipo de bloque que se envía al medio de clasificación, determinan una posible modificación del bloque en la primera fase en el medio de procesamiento. La memoria asociativa, es decir, una memoria a la que se accede comparando el contenido de los datos almacenados en la misma en lugar de dirigirse a ubicaciones predeterminadas, es programable, lo que hace que el procesamiento de encauzamiento sea incluso más flexible en comparación con el procesamiento en un ASIC.

De manera ventajosa, el método comprende las etapas de:

De este modo se consigue que sean posibles saltos condicionales cuando se ejecuta una posible instrucción de salto condicional correspondiente en la primera o la segunda fase.

La invención se refiere también a un medio de procesamiento para procesar datos encauzados según la reivindicación 5.

De manera adecuada, la al menos una unidad lógica en la al menos una fase de procesamiento encauzado está adaptada para recibir al menos un argumento asociado con el bloque y ejecutar la al menos una operación en el bloque, el al menos un argumento o tanto el bloque como el al menos un argumento.

Preferiblemente, la tabla de instrucciones comprende al menos una segunda instrucción. De este modo se consigue la opción de usar saltos condicionales durante el procesamiento encauzado.

En un primer aspecto del medio de procesamiento según la invención, el bloque es una PDU (Protocol Data unit, unidad de datos de protocolo), por ejemplo una parte de un paquete IP. De este modo se consigue que el medio de procesamiento pueda usarse, por ejemplo, en un aparato en una red de comunicaciones, tal como Internet.

En un segundo aspecto del medio de procesamiento, el bloque comprende una representación digital de una secuencia de señales analógicas. De este modo se consigue que el medio de procesamiento pueda usarse para el procesamiento de señales digitales.

De manera adecuada, la unidad lógica comprende una ALU y medios para extraer una parte o partes del bloque.

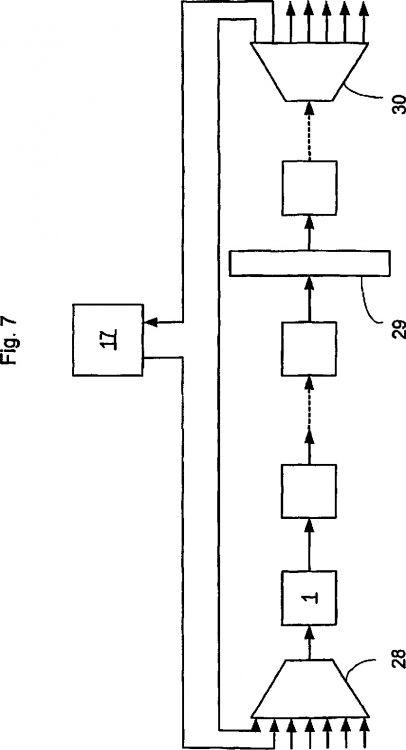

Además, la invención se refiere a un módulo para procesar datos encauzados. El módulo comprende un medio de clasificación para correlacionar o identificar un bloque de datos y un medio de procesamiento para procesar el bloque. El medio de procesamiento comprende medios de almacenamiento y al menos una unidad lógica para ejecutar operaciones en el bloque, que se suministra desde el medio de clasificación al medio de procesamiento. El medio de clasificación está adaptado para enviar un contador de programa asociado con el bloque al medio de procesamiento y el medio de almacenamiento comprende una tabla de instrucciones que comprende...

Reivindicaciones:

1. Método de procesamiento encauzado, que comprende una pluralidad de fases (9a-9e) de procesamiento encauzado, caracterizado por las etapas de:

2. Método según la reivindicación 1, en el que la al menos una fase (9a-9e) de procesamiento encauzado comprende la etapa de:

3. Método según la reivindicación 2, que comprende las etapas de:

4. Método según una cualquiera de las reivindicaciones anteriores, que comprende las etapas de:

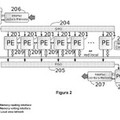

5. Medio (3) de procesamiento para procesar datos encauzados, que comprende medios (12a, 12b) de almacenamiento y una pluralidad de unidades (11, 14) lógicas para ejecutar operaciones en un bloque (4) de datos, caracterizados porque los medios (12a, 12b) de almacenamiento comprenden una pluralidad de tablas (12a, 12b) de instrucciones, comprendiendo cada una al menos una instrucción, porque una primera unidad (11) lógica de la pluralidad de unidades lógicas en una primera fase (9a) de procesamiento encauzado está adaptada para recibir el bloque (4) de datos y una primera instrucción (13a) correspondiente a un primer contador (7a) de programa asociado con el bloque (4) de datos, desde una primera tabla (12a) de instrucciones de la pluralidad de tablas de instrucciones y ejecutar al menos una operación asociada con la primera instrucción (13a), y porque una segunda unidad (14) lógica de la pluralidad de unidades lógicas en una segunda fase (9b) de procesamiento encauzado está adaptada para recibir el bloque (4) y una instrucción (13f) adicional correspondiente a un segundo contador (7b) de programa creado en la primera unidad (11) lógica y asociado con el bloque (4) de datos, desde una segunda tabla (12b) de instrucciones de la pluralidad de tablas de instrucciones y ejecutar al menos una operación asociada con la instrucción (13f) adicional.

6. Medio (3) de procesamiento según la reivindicación 5, en el que la al menos una de las unidades (11) lógicas está adaptada para recibir al menos un argumento (6) asociado con el bloque (4) de datos y ejecutar la respectiva al menos una operación en el bloque (4) de datos, el al menos un argumento (6) o tanto el bloque (4) de datos como el al menos un argumento (6).

7. Medio (3) de procesamiento según la reivindicación 5 ó 6, en el que al menos una de las tablas (12a) de instrucciones comprende también al menos una segunda instrucción (13b).

8. Medio (3) de procesamiento según una cualquiera de las reivindicaciones 5 a 7, en el que el bloque (4) de datos es una PDU, por ejemplo una parte de un paquete IP.

9. Medio (3) de procesamiento según una cualquiera de las reivindicaciones 5 a 7, en el que el bloque (4) de datos comprende una representación digital de una secuencia de señales analógicas.

10. Medio (3) de procesamiento según una cualquiera de las reivindicaciones 5 a 9, en el que al menos una de las unidades (11) lógicas comprende una ALU.

11. Medio (3) de procesamiento según la reivindicación 10, en el que la primera unidad (11) lógica comprende medios para extraer una parte o partes del bloque (4) de datos.

12. Módulo (1) para procesar datos encauzados, que comprende un medio (2) de clasificación para correlacionar o identificar un bloque (4) de datos y un medio (3) de procesamiento según la reivindicación 5 para procesar el bloque (4) de datos, comprendiendo el medio (3) de procesamiento medios (12a, 12b) de almacenamiento y al menos una unidad (11) lógica para ejecutar operaciones en el bloque (4) de datos, que se suministra desde el medio (2) de clasificación a los medios (3) de procesamiento,

caracterizado porque el medio (2) de clasificación está adaptado para enviar un contador (7a) de programa asociado con el bloque (4) de datos al medio (3) de procesamiento.

13. Módulo (1) según la reivindicación 12, en el que el medio (2) de clasificación está adaptado para enviar al menos un argumento (6) asociado con el bloque (4) de datos al medio (3) de procesamiento, y

la al menos una unidad (11) lógica en la al menos una fase de procesamiento encauzado está adaptada para recibir el al menos un argumento (6) y ejecutar la al menos una operación en el bloque (4) de datos, el al menos un argumento (6), o tanto el bloque (4) de datos como el al menos un argumento (6).

14. Circuito (15) integrado, caracterizado por al menos un módulo (1) según la reivindicación 12.

15. Unidad (22) de ordenador, tal como una unidad de ordenador en red o una unidad de ordenador de procesamiento de señales, que comprende al menos un circuito (15) integrado, caracterizada porque el al menos un circuito (15) integrado comprende al menos un módulo (1) según la reivindicación 12.

Patentes similares o relacionadas:

METODOS Y APARATO PARA LA EJECUCION MULTIPROCESO DE INSTRUCCIONES INFORMATICAS, del 9 de Diciembre de 2009, de SONY COMPUTER ENTERTAINMENT INC.: Un sistema informático multiproceso, que comprende: un procesador principal operable para gestionar el procesado de bucles de instrucciones […]

METODOS Y APARATO PARA LA EJECUCION MULTIPROCESO DE INSTRUCCIONES INFORMATICAS, del 9 de Diciembre de 2009, de SONY COMPUTER ENTERTAINMENT INC.: Un sistema informático multiproceso, que comprende: un procesador principal operable para gestionar el procesado de bucles de instrucciones […]

Procesador digital de señales y dispositivo de comunicación de banda base, del 5 de Noviembre de 2018, de MediaTek Sweden AB: Una unidad de ejecución de vectores para su uso en un procesador digital de señales que tiene un núcleo de procesador, […]

Procesador digital de señales y método para direccionar una memoria en un procesador digital de señales, del 18 de Octubre de 2017, de MediaTek Sweden AB: Un procesador digital de señales que comprende al menos una unidad funcional, que puede ser una unidad de ejecución de vectores , o un acelerador, […]

Procesador de señal digital y dispositivo de comunicación de banda base, del 16 de Agosto de 2017, de MediaTek Sweden AB: Un procesador de señal digital que comprende: - un núcleo de procesador que incluye una unidad de ejecución de enteros […]

Arquitectura híbrida SIMD/MIMD dinámicamente reconfigurable de un coprocesador para sistemas de visión, del 4 de Julio de 2013, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), dinámicamente […]

Arquitectura híbrida SIMD/MIMD dinámicamente reconfigurable de un coprocesador para sistemas de visión, del 4 de Julio de 2013, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), dinámicamente […]

ARQUITECTURA HÍBRIDA SIMD/MIMD DINÁMICAMENTE RECONFIGURABLE DE UN COPROCESADOR PARA SISTEMAS DE VISIÓN, del 29 de Noviembre de 2012, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), […]

ARQUITECTURA HÍBRIDA SIMD/MIMD DINÁMICAMENTE RECONFIGURABLE DE UN COPROCESADOR PARA SISTEMAS DE VISIÓN, del 29 de Noviembre de 2012, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), […]

Dispositivo de direccionamiento para procesador paralelo, del 15 de Agosto de 2012, de THALES: Procesador paralelo que comprende procesadores elementales que comprenden cada uno al menos unaunidad de cálculo y al menos una memoria que incluye palabras […]

SISTEMA DE PROCESAMIENTO DE DATOS Y DISPOSITIVO DE COMPUTACIÓN, del 12 de Marzo de 2012, de STARLAB BARCELONA SL: Sistema de procesamiento de datos y dispositivo de computación.

El sistema comprende:

- unos dispositivos de computación que procesan en paralelo […]

SISTEMA DE PROCESAMIENTO DE DATOS Y DISPOSITIVO DE COMPUTACIÓN, del 12 de Marzo de 2012, de STARLAB BARCELONA SL: Sistema de procesamiento de datos y dispositivo de computación.

El sistema comprende:

- unos dispositivos de computación que procesan en paralelo […]