DISPOSITIVO RECONFIGURABLE PARA EL CÁLCULO DE LA ESTIMACIÓN DE MOVIMIENTO.

Dispositivo reconfigurable para el cálculo de la estimación de movimiento que comprende:

(i) unos primeros medios procesadores ME (100) implementados con aritmética on-line y configurados para procesar la estimación de movimiento sobre tamaño de bloque variable, así como variar la precisión en la representación de los píxeles durante su funcionamiento; y

(ii) unos segundos medios gestores de datos (200) configurados para el suministro de datos (Cn,n;Rn,n) a dichos primeros medios (100).

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P201031628.

Solicitante: UNIVERSIDAD DE CORDOBA.

Nacionalidad solicitante: España.

Inventor/es: OLIVARES BUENO,Joaquín.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H04N7/12 ELECTRICIDAD. › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04N TRANSMISION DE IMAGENES, p. ej. TELEVISION. › H04N 7/00 Sistemas de televisión (detalles H04N 3/00, H04N 5/00; métodos y arreglos, para la codificación, decodificación, compresión o descompresión de señales de vídeo digital H04N 19/00; distribución selectiva de contenido H04N 21/00). › Sistemas en los cuales la señal de televisión es transmitida vía uno o varios canales paralelos, siendo el ancho de banda de cada canal inferior al ancho de banda de la señal de televisión (H04N 7/24 tiene prioridad).

Fragmento de la descripción:

Dispositivo reconfigurable para el cálculo de la estimación de movimiento Este dispositivo consiste en un circuito reconfigurable que resuelve la estimación de movimiento. El circuito permite variar la precisión en la representación de los píxeles, realizando todo el procesamiento en una única iteración. Se presenta también el diseño de los circuitos de memoria necesarios para suministrar datos. El circuito admite bloques de tamaño fijo y variable, cumpliendo con el estándar MPEG-4 AVC/H.264

La innovación del dispositivo que aquí se describe radica en que permite reconfigurar el proceso en función de la calidad que se quiere obtener. Además, está realizado mediante aritmética on-line (OLA, on-line arithmetics) , lo que permite acelerar el procesamiento, alcanzando un mejor rendimiento que los sistemas previos. Otra contribución importante es que se proporcionan los circuitos gestores de memoria específicos para el circuito que procesa la estimación del movimiento.

ESTADO DE LA TÉCNICA ANTERIOR

Para comprender el estado de la técnica es necesario realizar una fundamentación teórica que permita comprender el funcionamiento del dispositivo objeto de la presente invención.

I. Algoritmo de búsqueda y métrica La estimación del movimiento (ME) es una técnica utilizada en compresión de video. El objetivo de la ME es buscar para cada bloque de una imagen, otro bloque de igual tamaño y perteneciente a una imagen ya codificada anteriormente, que consiga que el error de predicción resultante se pueda codificar con el menor número de bits posible.

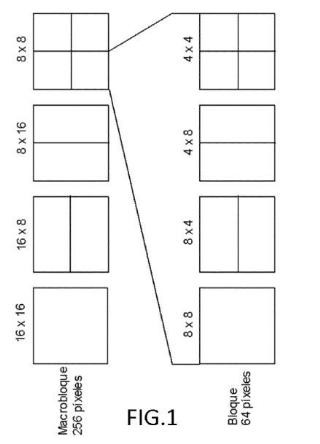

La estimación de movimiento, sobre bloques de tamaño variable, utilizada en el estándar de vídeo MPEG-4 AVC/H.264, se caracteriza por analizar varias posibilidades para un bloque de tamaño 16x16, en particular los subbloques de tamaño 4x4, y todas las combinaciones posibles a partir de ellos entre sub-bloques adyacentes. En la FIG.1 se muestran todos los sub-bloques posibles, en donde será preciso procesar el SAD (Sum of Absolute Diferences, Sumatorio de diferencias absolutas) para cada uno de ellos.

La métrica utilizada para obtener la estimación del movimiento es el SAD:

El cálculo del SAD se puede dividir en tres pasos:

-Cálculo de las diferencias: di, j =ci, j – ri, j

-Determinar el valor absoluto de cada diferencia | di, j|

-Adición de todas las diferencias

Posteriormente, se compara con el SAD de referencia. El SAD de referencia es el que mejor predicción presenta hasta ese momento, así, el bloque que mejor ajuste será aquel que presente un menor SAD.

El algoritmo de búsqueda utilizado se denomina Búsqueda completa (FSBMA, Full Search Block Matching Algorithm) y es ampliamente utilizado en circuitos, pues presenta una respuesta óptima y permite un flujo regular de datos que posibilita el diseño de arquitecturas especializadas de muy alto rendimiento.

El movimiento del bloque en la ventana de búsqueda es de izquierda a derecha. Gracias a este tipo de movimiento, el solapamiento que se produce al procesar dos bloques consecutivos viene dado por el tamaño del lado del bloque. A partir de ahora se notará como N al lado del bloque, siendo la dimensión del mismo N2. De forma específica, el tamaño típico para N en el estándar es N = 16. Una vez procesada toda una línea de bloques de la ventana (slice) se comienza a procesar la línea inmediatamente inferior, también de izquierda a derecha.

II. Representación aritmética: Signed-Digit Radix-2 y Aritmética On-line.

La representación utilizada en el dispositivo objeto de la presente invención no es la tradicional, pues permite trabajar con un grano más fino, trabajando a nivel de bit, en lugar de a nivel de byte. Gracias a ello, el dispositivo puede reconfigurar de forma eficiente la precisión utilizada para representar los píxeles.

La representación Signed Digit (SD) permite realizar los cálculos procesando en primer lugar los dígitos más significativos (MSD) , a diferencia de la lógica convencional, que comienza a procesar los dígitos menos significativos (LSD) . En las operaciones SD utilizadas es posible procesar los diferentes bits de cada píxel de forma independiente. Esta representación se basa en las siguientes características:

- Dígitos utilizados: (-1, 0, 1) en lugar de la base binaria tradicional (0, 1)

- Son necesarios dos bits para representar cada dígito: --1 se representa con la combinación 10 -0 se representa con la combinación 00, 11 -1 se representa con la combinación 01

III. Análisis comparativo entre tecnología basada en SAD y tecnología basada en SD.

En general, en el estado de la técnica se describen distintos circuitos en donde la métrica que se suele utilizar, en la mayoría de las arquitecturas que procesan la estimación del movimiento, es el cálculo de la Sumatoria de Diferencias Absolutas (SAD) , este punto es común a las arquitecturas, y la diferencia entre los distintos diseños se debe principalmente en el cómo se resuelve el cálculo del SAD, el coste y rendimiento de la arquitectura y los gestores de datos diseñados para proporcionar los mismos al núcleo principal del diseño que procesa las diferencias absolutas. Es usual ver autores que no proporcionan los gestores de datos y únicamente especifican el número de datos de entrada.

Se debe considerar una diferencia fundamental entre la arquitectura del dispositivo objeto de la invención (que utiliza tecnología Signed Digit Radix-2, SD) y las recogidas como estado de la técnica más cercano (aritmética convencional, SAD) : el uso de una aritmética diferente implica que todos los circuitos que se utilizan para ese procesamiento concreto son completamente diferentes. Así pues, el cálculo del SAD utiliza sumadores, diferencias absolutas y comparadores en ambas aritméticas, sin embargo, un sumador de aritmética convencional no es utilizable en tecnología SD. En aritmética convencional se procesa a nivel de palabra completa (8 bits) , mientras que en SD se procesa a nivel de dígito (2 bits) .

El diseño de un sumador SD no es el objeto de la patente, sino que es objeto de la invención la arquitectura completa para el procesamiento reconfigurable que admite cualquier número de bits en la precisión de los píxeles, incluyendo el gestor de datos. En la FIG.2 se muestra una comparativa entre la aritmética convencional en el cálculo de la diferencia absoluta en una primera (FIG.2a) y segunda opción (FIG.2b) y la aritmética SD (FIG.2c) .

En la FIG.3 se muestra la comparativa para la arquitectura del sumador, en donde la FIG.3a muestra el sumador con la aritmética convencional, en un ejemplo de 4 bits, en donde para las arquitecturas para el SAD será de 8 o más bits en función de su posición en el árbol de sumadores. En la FIG.3b se muestra el sumador con aritmética SD OLA donde, uno u otro, estará activo en función de la posición en el árbol de sumadores. En la FIG. 4 se muestra el circuito comparador con aritmética convencional de 2 bits (FIG.4a) y de 8 bits (FIG.2b) frente al comparador con aritmética SD (FIG.4c) .

IV. Análisis del estado de la técnica más cercano Han sido localizados una serie de documentos que pueden considerarse los antecedentes más próximos a la presente invención. Entre ellos, cabe destacar los siguientes:

1. A high-performance reconfigurable VLSI architecture for VBSME in H.264, Cao Wei et al. IEEE TRANSACTIONS ON CONSUMER ELECTRONICS, 20080801.

Este documento describe una arquitectura reconfigurable para VBSME en base al estándar MPEG-4 AVC/H.264 que permite utilizar VBSME con FBSMA, y donde se propone una arquitectura reconfigurable de alto rendimiento que gestiona una alta reutilización de los datos del área de búsqueda. La arquitectura soporta tres flujos de datos y se utilizan bloques SAD más pequeños para calcular vectores de movimiento (bloques de 16x16 en paralelo) .

Además de la diferencia fundamental radicada en la aritmética, en este circuito se procesa de forma completamente distinta, requiriendo al principio la precarga de datos y luego procesando los vectores de movimiento posibles en paralelo. El coste hardware de esta arquitectura es considerablemente más alto que el nuestro, puesto que el documento citado expone un coste de 160.000 puertas lógicas (160K) , mientras que el diseño del dispositivo objeto de la invención obtiene un coste de 54K, tres veces menor. El uso de la memoria de Wei es de aproximadamente 3, 25 KB mientras que la del circuito objeto de la presente invención es de apenas 784 bytes siendo cuatro veces inferior la cantidad de memoria utilizada.

Finalmente, debido a la estructura utilizada, la arquitectura...

Reivindicaciones:

1. Dispositivo reconfigurable para el cálculo de la estimación de movimiento que comprende: (i) unos primeros medios procesadores ME (100) implementados con aritmética on-line y configurados para procesar la estimación de movimiento sobre tamaño de bloque variable, así como variar la precisión en la representación de los píxeles durante su funcionamiento; y (ii) unos segundos medios gestores de datos (200) configurados para el suministro de datos (Cn, n;Rn, n) a dichos primeros medios (100) ; en donde dicho dispositivo se caracteriza porque los primeros medios procesadores ME (100) comprenden medios para el cálculo de la diferencia absoluta (110) , al menos uno por cada pareja de bits (Cn, n;Rn, n) a la entrada de unos medios sumadores de estimación de movimiento sobre bloques de tamaño variable VBSME (135) de tal forma que se calcule el sumatorio de diferencias absolutas SAD (140) ; y

donde los segundos medios gestores de datos (200) están configurados para manejar todos los datos de una ventana (slice) y comprenden un primer bloque de referencia, que permanece constante y que comprende una estructura BPS (210) , y un segundo bloque candidato que comprende dos estructuras BPS (210’, 210’’) que varían y son refrescadas por una estructura de memoria tipo P2BP (220) .

2. Dispositivo de acuerdo con la reivindicación 1 que se caracteriza porque las estructuras BPS (210, 210’, 210’’) contienen los N2 píxeles estructurados en 8 planos de bits, siendo 8 el número de bits con que se representa cada píxel; y donde las estructuras BPS se definen como un conjunto de 8 registros capaces de almacenar cada uno N2 bits.

3. Dispositivo de acuerdo con las reivindicaciones 1 y 2 que se caracteriza porque el bloque candidato necesita ser refrescado, dado que entre dos bloques adyacentes en la ventana (slice) se pueden reutilizar N2-N datos, debiéndose refrescar los N restantes mediante la estructura de memoria P2BP (220) la cual prepara en planos de bits los N píxeles del siguiente bloque de la ventana mientras se procesa el bloque actual.

4. Dispositivo de acuerdo con la reivindicación 3 que se caracteriza porque la estructura P2BP (220) es refrescada con al menos un píxel por ciclo de reloj.

5. Dispositivo de acuerdo con las reivindicaciones anteriores, que se caracteriza porque la segunda estructura BPS (210’’) del segundo bloque candidato tiene preparados los datos del primer bloque de la siguiente ventana (slice) , de tal forma que mientras los primeros medios (100) trabajan con los datos suministrados por la primera estructura BPS (210’) , se actualizará la segunda estructura (210’’) y viceversa.

6. Dispositivo de acuerdo con las reivindicaciones anteriores que se caracteriza porque los medios para el cálculo de la diferencia absoluta (110) procesan la diferencia absoluta para SD utilizando OLA y comprenden dos multiplexores 2:1 (111, 111’) de tal forma que se selecciona la salida en función de un comparador (112) que determina que el valor generado esté en valor absoluto; y donde dicho comparador (112) recibe los dígitos de un bit procedentes de los píxeles en modo Most Significant Digit (MSD) y determina el multiplexor activo en cuanto los dígitos comparados son diferentes; y donde si los dígitos son iguales, es irrelevante cual de los dos multiplexores está activo.

7. Dispositivo de acuerdo con las reivindicaciones anteriores que se caracteriza porque los medios sumadores de estimación de movimiento sobre bloques de tamaño variable VBSME (135) comprenden una pluralidad de sumadores básicos OLA (130, 130’) y una pluralidad de comparadores (120) conectados en cascada.

8. Dispositivo de acuerdo con la reivindicación 8 que se caracteriza porque a partir de los sumadores básicos OLA (130, 130’) se desarrolla un árbol de sumadores (133) o Sumador OLA para sub-bloque de tamaño 4x4, capaz de sumar 16 diferencias absolutas, siendo posible procesar en paralelo los N2 píxeles del bloque, siendo N=16, y calculándose en paralelo los vectores de todos los posibles sub-bloques.

9. Dispositivo de acuerdo con la reivindicación 8 dicho primer árbol de sumadores (133) conforman un primer circuito sumador referenciado como Sumador VBSME-N8 (134) que se caracteriza porque procesa el SAD

(140) para un sub-bloque de 8x8 y todos los sub-bloques de menor tamaño, utilizándose 4 árboles de sumadores del tipo Sumador OLA para sub-bloque de tamaño 4x4 (133) ; y donde utilizando el sumador VBSME-N8 (134) como base, se construye el sumador global llamado sumador VBSME-N16 (135) estando construida añadiendo dos sumadores sobre un árbol de sumadores común, al igual que se ha realizado en el sumador VBSME-N8 (134) con objeto de obtener el SAD (140) de los sub-bloques 8x16.

FIG. 11 FIG.12 FIG.13

FIG.15

Patentes similares o relacionadas:

Compresión, descompresión y visualización de video multinivel para aplicaciones 4K y 8K, del 29 de Enero de 2020, de YAMZZ IP BV: Un método implementado por ordenador para procesar un fotograma de vídeo, comprendiendo el método las etapas de: (a) procesar previamente el fotograma de vídeo realizando […]

Capa de sectores en códec de vídeo, del 27 de Noviembre de 2019, de Microsoft Technology Licensing, LLC: Un procedimiento de decodificación de vídeo e imágenes, que comprende: decodificar una imagen de un flujo de bits codificado que tiene una jerarquía […]

Sistemas y métodos para realizar búsqueda visual fluida de medios codificados para difusión en continuo de tasa de bits adaptativa usando flujos de reproducción no estándar, del 27 de Noviembre de 2019, de DIVX, LLC: Un método de realización de búsqueda visual de medios codificados para difusión en continuo de tasa de bits adaptativa usando un flujo de reproducción no estándar […]

Transformación solapada condicional, del 20 de Noviembre de 2019, de Microsoft Technology Licensing, LLC: Un método para codificar un flujo de bits de vídeo utilizando una transformación solapada condicional, en donde el método comprende: la señalización de un modo de filtro […]

Procedimiento y aparato para crear una función EOTF para un mapeo de código universal para una imagen HDR, del 20 de Noviembre de 2019, de KONINKLIJKE PHILIPS N.V: Un procedimiento para codificar una imagen que comprende los pasos de: - recibir una imagen de entrada de alto rango dinámico que comprende píxeles que tienen luminancias […]

Método de extracción de distorsión de codificación, del 23 de Octubre de 2019, de Godo Kaisha IP Bridge 1: Un aparato decodificador de imagen que decodifica una corriente de bits de una imagen codificada, incluyendo el aparato decodificador de imagen: una unidad receptora de […]

Procedimiento y aparato para codificación de Intra modo en HEVC, del 25 de Septiembre de 2019, de HFI Innovation Inc: Un procedimiento realizado por un codificador/decodificador, CODEC, para un procesamiento de modo de Intra predicción basado en múltiples modos más probables, modos MPM, en […]

Procedimiento y aparato para codificación de Intra modo en HEVC, del 25 de Septiembre de 2019, de HFI Innovation Inc: Un procedimiento realizado por un codificador/decodificador, CODEC, para un procesamiento de modo de Intra predicción basado en múltiples modos más probables, modos MPM, en […]

Método y sistema para referenciación geométrica de datos multiespectrales, del 6 de Marzo de 2019, de VITO NV: Un dispositivo de detección para obtener datos geométricos de imagen multiespectral referenciada de una región de interés en movimiento relativo con respecto al dispositivo […]