Convertidor analógico/digital con una topología de SAR así como procedimiento correspondiente.

Convertidor analógico/digital para la determinación del valor de medición absoluto con - un microcontrolador (10),

- una topología de SAR (11) para la generación de un valor digital momentáneo como consecuencia de una señal de tensión de entrada mediante intervalos encajados.

- un convertidor digital/analógico (12) que genera una tensión de referencia correspondiente al valor digital momentáneo,

- un comparador (13) para la comparación de la tensión de referencia con la señal de tensión de entrada del convertidor analógico/digital,

- un multiplexor (14, 18) para el funcionamiento del tipo múltiplex de varias fuentes de señal,

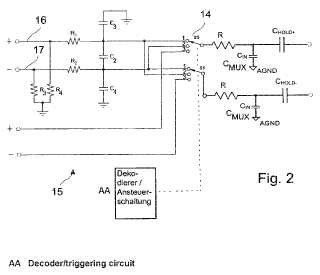

caracterizado por que está previsto un filtro de entrada diferencial (15), suministrándose la señal de tensión de entrada como una señal de tensión de entrada sobre-muestreada y como señal de entrada diferencial para cada fuente de señal mediante una línea de señal (16) y una línea de referencia de señal (17) al multiplexor con canales de entrada diferenciales, por que está previsto un paso de interruptor periódico (19) formado por el multiplexor (14), dispuesto detrás del filtro de entrada diferencial, estando aplicada la señal de tensión de entrada en una primera entrada del multiplexor y de forma invertida en una segunda entrada del multiplexor (14) para la disminución o eliminación de partes de desplazamiento de tensión continua de la señal de tensión de entrada mediante el uso del paso de interruptor periódico (19), y por que está previsto un formador de valor medio digital para la formación de valor medio de la señal de tensión de entrada sobre-muestreada, estando prevista una entrada diferencial (25) adicional, mediante la cual la señal de tensión de entrada para al menos una conversión analógica/digital (26) de un primer valor de muestreo salva el filtro de entrada (15).

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2009/004219.

Solicitante: Rutronik Elektronische Bauelemente GmbH.

Nacionalidad solicitante: Alemania.

Dirección: Industriestrasse 2 75228 Ispringen ALEMANIA.

Inventor/es: MANGLER,Andreas.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03M1/06 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 1/00 Conversión analógica/digital; Conversión digital/analógica (conversión de valores analógicos en, o a partir de una modulación diferencial H03M 3/00). › Compensación o prevención continua de la influencia indeseable de parámetros físicos (periódicamente H03M 1/10).

- H03M1/20 H03M 1/00 […] › Aumento de la resolución por la utilización de un sistema de n bits para obtener n + m bits, p. ej. por adición de una señal aleatoria.

- H03M1/46 H03M 1/00 […] › con convertidor digital/analógico para suministrar los valores de referencia al convertidor.

PDF original: ES-2382168_T3.pdf

Fragmento de la descripción:

Convertidor analógico/digital con una topología de SAR así como procedimiento correspondiente La invención se refiere a un convertidor analógico/digital para la determinación de valor de medición absoluto, con una topología de SAR de acuerdo con el preámbulo de la reivindicación 1, o a un procedimiento para la determinación de valores de acuerdo con el preámbulo de la reivindicación 9. Particularmente, la invención se basa en un proceso CMOS y una tecnología de base de SAR.

Además de la tendencia hacia velocidades crecientes de procesamiento en el procesamiento de señal analógica, en paralelo existen con frecuencia requisitos para una precisión cada vez mayor de las mediciones. Se busca la flexibilidad en aspectos de resolución, velocidad y capacidad de cambio de escala del sistema en convertidores analógicos/digitales integrados monolíticamente.

La aproximación de un valor comparativo al valor de partida analógico es característica de la función básica de la Aproximación Sucesiva de los convertidores analógicos/digitales de SAR. A este respecto, una aproximación sucesiva sencilla transforma por etapa un bit binario. Se puede conseguir una transformación mucho más precisa y rápida realizándose la transformación de forma redundante, es decir, transformándose por etapa solamente una parte de un bit. Un ADU (transformador/convertidor analógico/digital) o ADC (Convertidor Analógico Digital) que trabaja de acuerdo con el procedimiento de la aproximación sucesiva (es decir, aproximación por etapas) limita la señal entrante mediante intervalos encajados. Para esto posee, tal como está representado en la Figura 9, en el caso más sencillo un registro de datos (registro de aproximación sucesiva (successive approximation register) , SAR) 11, en el que se encuentra al final el valor digital establecido, un transformador digital-analógico 12, que genera una tensión de referencia analógica correspondiente al valor digital momentáneo del registro de datos, un comparador 13, que compara la tensión de referencia generada con la señal de tensión de entrada y un mecanismo de control (microcontrolador 10) . Para cada bit de precisión, un ADU sencillo necesita respectivamente una frecuencia de reloj de tiempo de transformación. La Figura 9 muestra un convertidor analógico/digital de SAR de este tipo con multiplexor de entrada de la empresa ZMD de acuerdo con el estado de la técnica. Tales transformadores consiguen resoluciones de aproximadamente 16 bits con una velocidad de transformación de aproximadamente 1 MHz.

El documento US 6.927.717 B1 muestra un convertidor analógico/digital delta-sigma basado en interruptor periódico (chopper) con función integradora y retardo de grupo (tiempo de latencia, elemento de tiempo muerto) mediante los dos decimadores y el filtro FIR digital. La señal pasa generalmente a lo largo de varios pasos 52, 54, 56, 58 a través del filtro FIR y los dos decimadores. El sistema describe un sistema de medición para la técnica de medición de tensión continua (medición de CC) . El sistema no tiene capacidad de trabajo en tiempo real en circuitos de regulación digitales.

McCartney, D et al: A Low-Noise Low-Drift Transducer ADC en: IEEE Journal of Solid State Circuits Vol. 32 Nº 7, julio de 1997, pág. 959 -967 describe una cadena de señales para la conversión analógica/digital lenta sin capacidad de trabajo en tiempo real basada en un principio delta/sigma.

La Solicitud de Patente US 2007/0252747 As describe un sistema con un filtro Sinc de varios pasos con una función de ruido aleatorio (dither) , que en esta configuración descrita no tiene capacidad de trabajo en tiempo real. Está previsto un convertidor A/D de SAR, sin embargo, con el objetivo de evitar durante la conversión códigos faltantes 45 (missing codes) . Debido al filtro digital de cuatro pasos, el sistema no tiene capacidad de trabajo en tiempo real. En la Figura 14a se describe una cadena de señales con cuatro filtros Sinc conectados sucesivamente. De este modo, el procedimiento solamente es adecuado para la técnica de medición de CC. El objetivo es mejorar la falta de linealidad diferencial (desviación del peldaño de escalera ideal del cuantificador) mediante una mayor resolución útil del convertidor A/D mediante varios filtros digitales.

La Patente de Estados Unidos US 7.049.989 B2 describe una función PGA sencilla con topología diferencial mediante conexión en paralelo y en serie de resistores que determinan la amplificación, que se realizó mediante un potenciómetro digital (DAC) y conmutadores analógicos. En ese documento, el objetivo es utilizar de forma óptima el intervalo dinámico (intervalo de modulación) de un convertidor posterior analógico/digital y adaptar mediante el 55 amplificador (programable) ajustable de forma digital. En este caso se trata de una técnica de medición aplicada conocida, que, sin embargo, en la práctica apenas se aplica debido al uso de resistores de alta precisión. El artículo especializado Andreas Mangler, "Temperaturen präzise messen" en Wekaverlag Elektronik Distribution, Sonderheft junio 2009, pág. 16-21 muestra el estado actual de la técnica.

Por YAZICIOGLU R F ET AL: "A 200 μW Eight-Channel Acquisition ASIC for AMBULATORY EEG Systems" 3 de febrero de 2008 () , SOLID-STATE CIRCUITS CONFERENCE, 2008. ISSCC 2008. DIGEST OF TECHNICAL PAPERS. IEEE INTERNATIONAL, IEEE, PISCATAWAY, NJ, USA, PÁGINA (S) 164-603, XP031440499 ISBN: 9781424450100 se conoce un amplificador de instrumentación acoplado a CA, estabilizado con interruptor periódico (ACCIA) combinado con un paso de filtro de paso alto amplio posterior. De esta forma, la solución está 65 ajustada al fin de utilización previsto en ese documento de la detección de los valores de medición de electroencefalogramas, sin embargo, mediante el acoplamiento de CA se eliminan las señales de tensión continua requeridas para una medición de valor absoluto, de tal forma que no es posible un acoplamiento de señal de tensión continua para la medición precisa de CC.

El documento US 6.448.912 B1 desvela en un sensor de píxeles activo una formación de valor medio con ayuda de un sobre-muestreo y una señal de ruido aleatorio. Las señales de modo común o las interferencias de modo común no se suprimen con este método, sino que se añaden al resultado de la conversión. Ya que tales fotosensores se acoplan de forma capacitiva (acoplamiento de CA) al convertidor analógico/digital posterior, no es posible una medición precisa de tensión continua. Falta un procedimiento de medición de correlación para la supresión de señal interferente.

Por Analog Devices: "CMOS, +1, 8 V to +5, 5 V / ±2, 5 V, 2, 5 Ohm Low-voltage, 8-/16-Channel Multiplexers ADG706/ADG707" 31 de mayo de 2002 () , XP002556474 hallado en internet URL: http://www.analog.com/static/imported-files/Data_Sheets/ADG706_7007.pdf [hallado el ] se conoce la estructura generalmente discreta de multiplexores. La ficha de datos describe dos configuraciones diferentes de multiplexores, concretamente un multiplexor 16a1 y un multiplexor 8a1 diferencial.

Los convertidores analógicos/digitales delta-sigma desvelados en estos documentos tienen principalmente una función integradora, por tanto, el comportamiento de un filtro de paso bajo de baja frecuencia con un tiempo de respuesta definido. Todos estos procedimientos en la forma descrita son adecuados para mediciones de CC o de forma limitada en la técnica de medición de CA lenta. El posterior perfilador de ruido (noise-shaper) y el filtro digital generan adicionalmente un denominado tiempo de latencia o retardo de grupo. En la técnica de regulación, la función resultante del convertidor analógico/digital delta-sigma es una combinación de filtro de paso bajo y tiempo muerto. Por tanto no se pueden realizar sistemas de regulación en tiempo real complejos rápidos con convertidores analógicos/digitales delta sigma. Si se tienen distintos circuitos de regulación superpuestos, tal como en controles de motor o en sistemas multieje, habitualmente el sistema de regulación digital se inestabiliza.

Son propiedades de los convertidores analógicos/digitales delta sigma:

• comportamiento de salto limitado, función de filtro de paso bajo

• trabaja de forma eficaz solamente con señales continuas en la entrada

• tiempo de latencia/retardo de grupo del sistema conducen a tiempos muertos en un circuito de regulación cerrado o a reacciones ralentizadas en un control

• la velocidad de ciclo tiene una influencia directa sobre la función de transmisión del filtro digital

Son otras topologías... [Seguir leyendo]

Reivindicaciones:

1. Convertidor analógico/digital para la determinación del valor de medición absoluto con -un microcontrolador (10) , -una topología de SAR (11) para la generación de un valor digital momentáneo como consecuencia de una señal de tensión de entrada mediante intervalos encajados. -un convertidor digital/analógico (12) que genera una tensión de referencia correspondiente al valor digital momentáneo, -un comparador (13) para la comparación de la tensión de referencia con la señal de tensión de entrada del convertidor analógico/digital, -un multiplexor (14, 18) para el funcionamiento del tipo múltiplex de varias fuentes de señal, caracterizado por que está previsto un filtro de entrada diferencial (15) , suministrándose la señal de tensión de entrada como una señal de tensión de entrada sobre-muestreada y como señal de entrada diferencial para cada fuente de señal mediante una línea de señal (16) y una línea de referencia de señal (17) al multiplexor con canales de entrada diferenciales, por que está previsto un paso de interruptor periódico (19) formado por el multiplexor (14) , dispuesto detrás del filtro de entrada diferencial, estando aplicada la señal de tensión de entrada en una primera entrada del multiplexor y de forma invertida en una segunda entrada del multiplexor (14) para la disminución o eliminación de partes de desplazamiento de tensión continua de la señal de tensión de entrada mediante el uso del paso de interruptor periódico (19) , y por que está previsto un formador de valor medio digital para la formación de valor medio de la señal de tensión de entrada sobre-muestreada, estando prevista una entrada diferencial (25) adicional, mediante la cual la señal de tensión de entrada para al menos una conversión analógica/digital (26) de un primer valor de muestreo salva el filtro de entrada (15) .

2. Convertidor analógico/digital de acuerdo con la reivindicación 1, caracterizado por que está previsto un paso de adición (24) para la adición de una señal de ruido aleatorio al valor digital.

3. Convertidor analógico/digital de acuerdo con la reivindicación 1 o 2, caracterizado por que las entradas de diferencia del filtro de entrada diferencial (15) se refieren a la masa (20) , estando previsto preferentemente al menos un resistor (R3, R4) de alta resistencia de al menos una de las dos entradas del filtro de entrada diferencial (15) para la masa (20) , estando seleccionado el tamaño del al menos un resistor de tal manera que la tensión de diferencia es menor que la precisión de medición deseada del sistema.

5. Convertidor analógico/digital de acuerdo con la reivindicación 4, caracterizado por que está previsto al menos un condensador (C2) , que está dispuesto en paralelo con respecto a una fuente de diferencia para la señal de entrada diferencial, siendo el valor del condensador (C2) mucho mayor que el valor de los condensadores (C3, C4) del filtro de HF simétrico y/o siendo el condensador (C2) con una precisión deseada de X bits mayor en un factor 2x que los capacitores de multiplexor CMUX (21) conectados en serie. 7. Convertidor analógico/digital de acuerdo con una de las reivindicaciones precedentes, caracterizado por que está previsto un filtro de característica en peine para el ajuste o la regulación de la frecuencia de muestreo de interruptor periódico que controla o regula para la supresión dirigida de frecuencias interferentes el tiempo de respuesta del multiplexor. 8. Convertidor analógico/digital de acuerdo con una de las reivindicaciones precedentes, caracterizado por que 55 está determinado para un asistente de frenado electrónico con capacidad de trabajo en tiempo real para vehículos motorizados basado en un sistema regulado digitalmente. 9. Procedimiento para la determinación de valores de medición absolutos con un convertidor analógico/digital con un microcontrolador (10) , un multiplexor (14, 18) y una topología de SAR (11) , que genera un valor digital momentáneo debido a una señal de tensión de entrada mediante intervalos encajados, así como con un convertidor digital/analógico (12) que genera una tensión de referencia correspondiente al valor digital momentáneo, que se compara en un comparador (13) con la señal de tensión de entrada del convertidor analógico/digital, caracterizado por que para un filtro de entrada diferencial (15) la señal de tensión de entrada se suministra como señal de tensión de entrada sobre-muestreada y como una señal de entrada diferencial para cada fuente de señal mediante una línea 65 de señal (16) y una línea de referencia de señal (17) al multiplexor con canales de entrada diferenciales, por que la señal de tensión de entrada se aplica en un paso de interruptor periódico (19) formado por el multiplexor (14, 18) , dispuesto detrás del filtro de entrada diferencial, aplicándose la señal de tensión de entrada en una primera entrada del multiplexor y de forma invertida en una segunda entrada del multiplexor para la disminución o eliminación de partes de desplazamiento de tensión continua de la señal de tensión de entrada, por que a partir de la señal de tensión de entrada sobre-muestreada se forma un valor medio digital de la señal de tensión de entrada y por que se salva el filtro de entrada (15) para la señal de tensión de entrada mediante una entrada diferencial (25) adicional para al menos una conversión analógica/digital (26) de un primer valor de muestreo. 10. Procedimiento de acuerdo con la reivindicación 9, caracterizado por que se añade una señal de ruido aleatorio al valor digital. 10 11. Procedimiento de acuerdo con la reivindicación 9 o 11, caracterizado por que las entradas de diferencia del filtro de entrada diferencial (15) se refieren a la masa (20) . 12. Procedimiento de acuerdo con una de las reivindicaciones precedentes 9 a 11, caracterizado por que está dispuesto al menos un resistor (R3, R4) de alta resistencia de al menos una de las dos entradas del filtro de entrada diferencial (15) con respecto a la masa (20) , seleccionándose el tamaño del al menos un resistor de tal manera que la tensión de diferencia es menor que la precisión de medición deseada del sistema. 13. Procedimiento de acuerdo con una de las reivindicaciones precedentes 9 a 12, caracterizado por que el tiempo entre el momento de la conmutación del multiplexor y el momento del muestreo del convertidor analógico/digital se retrasa mediante un elemento de retraso. 14. Procedimiento de acuerdo con una de las reivindicaciones precedentes 9 a 13, caracterizado por que un filtro de característica en peine para influir en la frecuencia de muestreo del interruptor periódico controla o regula el 25 tiempo de respuesta del multiplexor. 15. Procedimiento de acuerdo con una de las reivindicaciones precedentes 9 a 14, caracterizado por que se usa en un asistente de frenado electrónico con capacidad de trabajo en tiempo real para vehículos motorizados basado en un sistema regulado digitalmente. 35 4. Convertidor analógico/digital de acuerdo con una de las reivindicaciones precedentes, caracterizado por que al filtro de entrada diferencial (15) está asignado un filtro de HF simétrico que comprende al menos dos condensadores (C3, C4) preferentemente con respecto a masa (20) .

45 6. Convertidor analógico/digital de acuerdo con una de las reivindicaciones precedentes, caracterizado por que está previsto un elemento de retraso para el retraso en el tiempo entre el momento de la conmutación del multiplexor y el momento del muestreo del convertidor analógico/digital.

Patentes similares o relacionadas:

Dispositivo de captura de imagen de semiconductores, instrumento electrónico y dispositivo de conversión analógico a digital, del 29 de Abril de 2020, de SONY CORPORATION: Un dispositivo de captura de imagen de semiconductores que comprende: una sección de píxel que tiene una pluralidad de píxels ; un comparador […]

Dispositivo de resincronización de señales analógicas obtenidas por conversión, con unos convertidores digital-analógico DDR, de señales digitales sincronizadas, del 28 de Febrero de 2018, de THALES: Dispositivo de resincronización de una pluralidad de señales analógicas (DAC_OUTPUTA, DAC_OUTPUTB) obtenidas por conversión, con unos convertidores digital-analógico […]

Sistema de control de cargas eléctricas que recibe al menos dos fases de una red de distribución eléctrica, del 16 de Noviembre de 2016, de Groupe Brandt: Sistema de control de cargas eléctricas que recibe al menos dos fases (PH1, PH2) de una red de distribución eléctrica, constituyendo cada […]

Métodos y aparatos para la estimación y la compensación de los errores de no linealidad, del 29 de Diciembre de 2015, de Signal Processing Devices Sweden AB: Una unidad de estimación (30, 30a-c) para estimar un error de no linealidad de un circuito de conversión , en la que el circuito de conversión […]

Métodos y aparatos para la estimación y la compensación de los errores de no linealidad, del 29 de Diciembre de 2015, de Signal Processing Devices Sweden AB: Una unidad de estimación (30, 30a-c) para estimar un error de no linealidad de un circuito de conversión , en la que el circuito de conversión […]

Método para convertir datos analógicos en datos digitales para un módulo de entrada analógica, del 28 de Mayo de 2013, de LS INDUSTRIAL SYSTEMS CO., LTD: Un método para convertir una señal de entrada analógica recibida por un módulo de entrada analógica en un conjunto de datos digitales, comprendiendo el método:

recibir, […]

Método para convertir datos analógicos en datos digitales para un módulo de entrada analógica, del 28 de Mayo de 2013, de LS INDUSTRIAL SYSTEMS CO., LTD: Un método para convertir una señal de entrada analógica recibida por un módulo de entrada analógica en un conjunto de datos digitales, comprendiendo el método:

recibir, […]

METODO Y APARATO PARA LA CORRECCION DE ERRORES DE DESVIACION DE C.C. EN CONVERTIDORES DIGITALES A ANALOGICOS., del 16 de Agosto de 2006, de QUALCOMM INCORPORATED: Un circuito de corrección de desviación c.c. para eliminar errores de desviación c.c. de señales de transmisión en banda base en un dispositivo […]

METODO Y DISPOSITIVO PARA MUESTREAR SEÑALES ANALOGICAS., del 1 de Noviembre de 2002, de TELEFONAKTIEBOLAGET LM ERICSSON: PROCEDIMIENTO Y DISPOSITIVO PARA LE MUESTREO DE UNA SEÑAL ANALOGICA (U(T)) OBTENIENDO PRIMERAS SECUENCIA DE VALORES DE MUESTRA DIFERENCIADOS (S 1 A I (T), (S 1 A Q […]

CIRCUITO DE MEDICION DE CORRIENTE QUE COMPRENDE UN TRANSFORMADOR MUTUAMENTE ACOPLADO Y UN CIRCUITO DE INTEGRACION., del 16 de Diciembre de 2001, de SCHLUMBERGER INDUSTRIES S.A.: UN CIRCUITO MEDIDOR DE CORRIENTE QUE CONSTA DE UN TRANSFORMADOR DE INDUCTANCIA MUTUA , UN CIRCUITO DE INTEGRACION Y UN CIRCUITO DE […]