Métodos y aparatos para la estimación y la compensación de los errores de no linealidad.

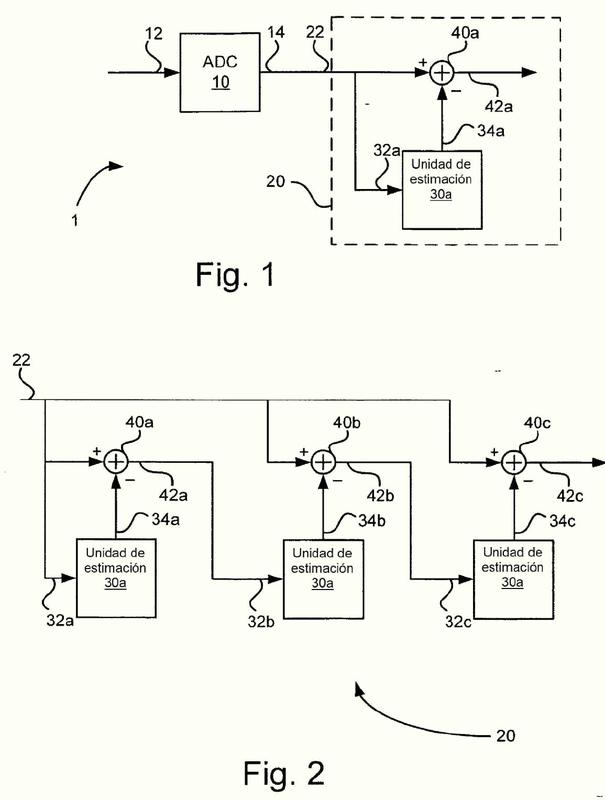

Una unidad de estimación (30, 30a-c) para estimar un error de no linealidad de un circuito de conversión (10),

en la que el circuito de conversión está adaptado para recibir una señal de entrada en tiempo continuo y emitir una señal de salida digital, en donde la señal de entrada en tiempo continuo está limitada en banda esencialmente a una banda de frecuencia angular que tiene un límite inferior (w1) y un límite superior (w2), en la que w1 > (L-1)p/T, w2 < Lp/T, L es un número entero positivo y T es un periodo de muestreo del circuito de conversión, comprendiendo la unidad de estimación (30, 30a-c):

un puerto de entrada (32, 32a-c) para recibir una señal de entrada digital que tiene una primera tasa de muestreo 1/T, en el que la señal de entrada digital es la señal de salida digital del circuito de conversión (10); y

un puerto de salida (34, 34a-c) para emitir una señal de error estimada digital que tiene la primera tasa de muestreo, en el que la señal de error estimada digital es una estimación del error de no linealidad del circuito de conversión (10),

en donde la unidad de estimación comprende una rama para cada P_k, en donde P_k es un número entero en un conjunto de números enteros, k es un número entero en un intervalo de 1 ≤ k ≤ N y P_k es mayor que o igual a 2, comprendiendo cada rama:

- una primera unidad de filtro lineal (100-k) para generar una primera señal (s1(n)) como una función lineal de la señal de entrada digital;

- una unidad de interpolación (105-k) para interpolar la primera señal (s1(n)) para generar una segunda señal (s2(m)) que tiene una segunda tasa de muestreo que es un factor L·R_k más alta que la primera tasa de muestreo, en donde R_k es un valor seleccionado de manera que L·R_k ≥ T·w2·P_k/p;

- una unidad de no linealidad (110-k) para generar una tercera señal (s3(m)) como dicha segunda señal (s2(m)) a la potencia P_k; y

- una segunda unidad de filtro lineal (115-k) para generar un componente de la señal de error estimada digital basándose en la tercera señal (s3(m)), en la que dicho componente tiene la primera tasa de muestreo, en donde los coeficientes de filtro de las unidades de filtro lineal primera y segunda se establecen de tal manera que la unidad de estimación es un modelo de tiempo discreto del circuito de conversión e imita el comportamiento del circuito de conversión con una precisión deseada; y

un circuito sumador (117) para generar la señal de error estimada digital como la suma de todos los componentes mencionados de dichas ramas.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2008/067663.

Solicitante: Signal Processing Devices Sweden AB.

Nacionalidad solicitante: Suecia.

Dirección: Teknikringen 6 583 30 Linköping SUECIA.

Inventor/es: JOHANSSON,HÅKAN.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03H21/00 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03H REDES DE IMPEDANCIA, p. ej. CIRCUITOS RESONANTES; RESONADORES (medidas, ensayos G01R; disposiciones para producir una reverberación sonora o un eco G10K 15/08; redes de impedancia o resonadores que se componen de impedancias distribuidas, p. ej. del tipo guía de ondas, H01P; control de la amplificación, p. ej. control del ancho de banda de los amplificadores, H03G; sintonización de circuitos resonantes, p. ej. sintonización de circuitos resonantes acoplados, H03J; redes para modificar las características de frecuencia de sistemas de comunicación H04B). › Redes adaptativas.

- H03M1/06 H03 […] › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 1/00 Conversión analógica/digital; Conversión digital/analógica (conversión de valores analógicos en, o a partir de una modulación diferencial H03M 3/00). › Compensación o prevención continua de la influencia indeseable de parámetros físicos (periódicamente H03M 1/10).

PDF original: ES-2555210_T3.pdf

Patentes similares o relacionadas:

Dispositivo de captura de imagen de semiconductores, instrumento electrónico y dispositivo de conversión analógico a digital, del 29 de Abril de 2020, de SONY CORPORATION: Un dispositivo de captura de imagen de semiconductores que comprende: una sección de píxel que tiene una pluralidad de píxels ; un comparador […]

Dispositivo de resincronización de señales analógicas obtenidas por conversión, con unos convertidores digital-analógico DDR, de señales digitales sincronizadas, del 28 de Febrero de 2018, de THALES: Dispositivo de resincronización de una pluralidad de señales analógicas (DAC_OUTPUTA, DAC_OUTPUTB) obtenidas por conversión, con unos convertidores digital-analógico […]

Sistema de control de cargas eléctricas que recibe al menos dos fases de una red de distribución eléctrica, del 16 de Noviembre de 2016, de Groupe Brandt: Sistema de control de cargas eléctricas que recibe al menos dos fases (PH1, PH2) de una red de distribución eléctrica, constituyendo cada […]

Método para convertir datos analógicos en datos digitales para un módulo de entrada analógica, del 28 de Mayo de 2013, de LS INDUSTRIAL SYSTEMS CO., LTD: Un método para convertir una señal de entrada analógica recibida por un módulo de entrada analógica en un conjunto de datos digitales, comprendiendo el método:

recibir, […]

Método para convertir datos analógicos en datos digitales para un módulo de entrada analógica, del 28 de Mayo de 2013, de LS INDUSTRIAL SYSTEMS CO., LTD: Un método para convertir una señal de entrada analógica recibida por un módulo de entrada analógica en un conjunto de datos digitales, comprendiendo el método:

recibir, […]

Convertidor analógico/digital con una topología de SAR así como procedimiento correspondiente, del 6 de Junio de 2012, de Rutronik Elektronische Bauelemente GmbH: Convertidor analógico/digital para la determinación del valor de medición absoluto con - un microcontrolador ,

- una topología de SAR […]

Convertidor analógico/digital con una topología de SAR así como procedimiento correspondiente, del 6 de Junio de 2012, de Rutronik Elektronische Bauelemente GmbH: Convertidor analógico/digital para la determinación del valor de medición absoluto con - un microcontrolador ,

- una topología de SAR […]

METODO Y APARATO PARA LA CORRECCION DE ERRORES DE DESVIACION DE C.C. EN CONVERTIDORES DIGITALES A ANALOGICOS., del 16 de Agosto de 2006, de QUALCOMM INCORPORATED: Un circuito de corrección de desviación c.c. para eliminar errores de desviación c.c. de señales de transmisión en banda base en un dispositivo […]

METODO Y DISPOSITIVO PARA MUESTREAR SEÑALES ANALOGICAS., del 1 de Noviembre de 2002, de TELEFONAKTIEBOLAGET LM ERICSSON: PROCEDIMIENTO Y DISPOSITIVO PARA LE MUESTREO DE UNA SEÑAL ANALOGICA (U(T)) OBTENIENDO PRIMERAS SECUENCIA DE VALORES DE MUESTRA DIFERENCIADOS (S 1 A I (T), (S 1 A Q […]

Dispositivo de filtro adaptativo en el dominio de la frecuencia de bloques con partición que comprende módulos de adaptación y módulos de corrección, del 22 de Mayo de 2019, de FRAUNHOFER-GESELLSCHAFT ZUR FORDERUNG DER ANGEWANDTEN FORSCHUNG E.V.: Dispositivo de filtro adaptativo en el dominio de la frecuencia de bloques con partición que comprende: un filtro adaptativo en el dominio de la frecuencia configurado […]