GENERADOR DE CÓDIGO Y DISPOSITIVO PARA LA IDENTIFICACIÓN SÍNCRONA O ASÍNCRONA Y PERMANENTE O EL ENCRIPTADO Y DESENCRIPTADO DE DATOS DE CUALQUIER LONGITUD.

Generador de código con una pluralidad de elementos de memoria (FF1,

2, ...n) conectados para formar una serie (R) que genera código, por ejemplo, flip-flops, estando conectada la salida del último elemento de memoria (FF5) en la serie (R) con la entrada del primer elemento de memoria (FF1) de la serie (R) para formar un circuito, estando prevista por lo menos una puerta lógica EXOR (EXORp1), cuya primera entrada (1) está conectada con la salida de un elemento de memoria (FF1) que se encuentra en la serie (R) generadora de código, cuya segunda entrada (2) lo está con la salida de otro elemento de memoria (FF3) que se encuentra en la serie (R) generadora de código y cuya salida (3) está conectada con la entrada del elemento de memoria (FF2) posterior al elemento de memoria (FF1) conectado con la primera entrada (1) de la puerta lógica EXOR (EXORp1) en la serie (R) generadora de código, caracterizado porque las salidas y por lo menos una entrada de los elementos de memoria están conectadas de manera recursiva con interconexión de por lo menos una puerta lógica EXOR (EXORp1), en la línea que conecta la segunda entrada (2) de dicha por lo menos una puerta lógica EXOR (EXORp1) y la salida del otro elemento de memoria (FF3) que se encuentra en la serie (R) generadora de código está conectada de tal manera una puerta lógica Y (Yp1), que la salida (4) de la puerta lógica Y (Y01) está conectada con la segunda entrada (2) de la puerta lógica EXOR (EXORp1), la primera entrada (6) de la puerta lógica Y (Yp1) lo está con la salida del otro elemento de memoria (FF3) que se encuentra en la serie (R) generadora de código y la segunda entrada (5) de la puerta lógica Y (Yp1) lo está con la salida de un elemento de memoria (FFp1) programado mediante código y porque la salida de un elemento de memoria (FF5) que se encuentra en la serie (R) generadora de código está conectada con la entrada de un inversor (INV) y la salida del inversor (INV) lo está con la entrada de otro elemento de memoria (FF1) dispuesto en la serie (R) generadora de código

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/AT2003/000063.

Solicitante: Cordes, René

Schobesberger, Ernst

M&C Consult Invest & Trade GmbH.

Nacionalidad solicitante: Austria.

Dirección: Raiffeisengasse 3 2323 Mannswörth AUSTRIA.

Inventor/es: Cordes,René.

Fecha de Publicación: .

Fecha Solicitud PCT: 5 de Marzo de 2003.

Clasificación Internacional de Patentes:

- H04L9/26 ELECTRICIDAD. › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › H04L 9/00 Disposiciones para las comunicaciones secretas o protegidas. › produciendo una secuencia pseudoaleatoria no lineal.

Clasificación PCT:

- H04L9/26 H04L 9/00 […] › produciendo una secuencia pseudoaleatoria no lineal.

Clasificación antigua:

- H04L9/26 H04L 9/00 […] › produciendo una secuencia pseudoaleatoria no lineal.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

PDF original: ES-2364456_T3.pdf

Fragmento de la descripción:

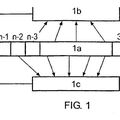

La presente invención se refiere a un generador de código con una pluralidad de elementos de memoria conectados para formar una serie que genera código, por ejemplo flip-flops (biestables), estando conectada la salida del último elemento de memoria en la serie con la entrada del primer elemento de memoria de la serie para formar un circuito, estando prevista por lo menos una puerta lógica EXOR, cuya primera entrada está conectada con la salida de un elemento de memoria que se encuentra en la serie generadora de código, cuya segunda entrada lo está con la salida de otro elemento de memoria que se encuentra en la serie generadora de código y cuya salida está conectada con la entrada del elemento de memoria posterior al elemento de memoria conectado con la primera entrada de la puerta lógica EXOR en la serie generadora de código. Un generador de código de este tipo se describe en el artículo “PSEUDORANDOM BIT GENERATORS IN STREAM-CIPHER CRYPTOGRAPHY” de Kencheng Zeng, publicado en COMPUTER, IEEE COMPUTER SOCIETY, LONG BEACH., CA, US, US, Vol. 24, Nº 2, 1 de Febrero de 1991 (1991-02-01), páginas 8-17, XP000219462 USSN: 0018-9162. Los generadores de código se utilización para el encriptado y la transmisión de informaciones a través de redes de comunicación. En principio, todos los métodos de encriptado utilizan un código, aunque la propia información que haya que encriptar se utilice como código. Cuanto mejor esté escondido el código utilizado para la encriptación tanto más efectiva será la encriptación. Cuanto más largo sea el código más difícil será de descifrar. Por ejemplo, un código infinito no necesitaría ser escondido dado que no se conoce nunca completamente. Funcionalmente, debe considerarse como infinito cualquier código que no se repite antes del final de la información que hay que encriptar. Un código funcionalmente infinito tiene la ventaja de que el propio proceso de encriptado y desencriptado se puede realizar de manera sencilla mediante una única conexión EXOR ó EXNOR. Un código funcionalmente infinito tiene la desventaja de que no puede ser transmitido; debe ser generado.

Existe una posibilidad sencilla de generar un código funcionalmente infinito, gracias a conectar las dos entradas de una puerta lógica EXOR con dos salidas de elementos de memoria conectados para forma una serie, es decir por ejemplo un registro de desplazamiento, y conectando la salida de la puerta lógica EXOR de manera recursiva con la entrada de registro de desplazamiento.

El resultado es una secuencia de código cuya longitud máxima tiene

**(Ver fórmula)**

(Lc = longitud de la secuencia de código; n = número de los elementos de memoria generadores de código conectados en serie)

bits.

En este generador de código, es desventajoso el hecho de que a partir de la secuencia de código se puede deducir con facilidad la estructura del generador, de manera que puede ser regenerada con un generador construido de igual manera. Las patentes que se mencionan a continuación representan intentos de continuar encriptando estas secuencias de código mediante otros procesos, de manera que ya no se puedan reconstruir: US 2001033663, WO 01/05090, WO 99/22484, WO 99/16208, JP10320181, WO 98/02990 y EP 0782069. Los generadores de código que se han dado a conocer a partir de estas publicaciones tienen en común que la longitud del código producido es acortada mediante efectos de resonancia. Además, un número de generadores suedoaleatorios, como se describen por ejemplo en los documentos JP 2000-101567, JP 2001-016197, EP 0913964 ó EP 0782069. Estos generadores de código trabajan con variables, calculándose con la ayuda de un algoritmo de conversión matemático no lineal una secuencia de código a partir de estas variables. Esto sucede para la reducción de la posibilidad del cálculo de vuelta con la ayuda de funciones matemáticas superiores y muy superiores. Estos sistemas tienen en común que se sirven de una unidad funcional matemática, la cual tiene una entrada multi-Bit, en la cual está la variable de salida que se encuentra la memoria de código, así como una salida de un-Bit, en la cual se lee una secuencia de código serie, lo cual tiene un efecto desventajoso sobre la velocidad de generación de código máxima que se puede alcanzar. La matemática superior y muy superior tiene como función también encontrar soluciones sencillas para fórmulas compleja, motivo por el cual el riesgo del descubrimiento de una solución sencilla para una función matemático por muy compleja que sea no se puede excluir por completo y no se puede, naturalmente, dejar de evaluar.

La presente invención se refiere a crear un dispositivo para la generación de muchas secuencias de código diferentes, lo más largas posibles, debiendo encontrarse lo suficiente con una complejidad de elementos de conmutación pequeña. El generador de código debe ser adecuado, mediante la utilización de operaciones con bits, para el encriptado simultáneo de flujos de datos binarios de alta frecuencia durante intervalos de tiempo largos, debiendo permanecer secreto incluso el código de salida.

Para la solución de este problema la invención prevé un generador de código según la reivindicación 1. Al mismo tiempo, son conocidos tanto la estructura del generador de código como también el algoritmo que se hace correr en el mismo. La estructura es de todos modos de tal tipo que está en disposición de generar un número tan grande de códigos diferentes con una longitud de tal manera grande que el descubrimiento del código que se utiliza en ese instante así como la posición generadas actualmente en la secuencia de código es posible únicamente con una probabilidad extremadamente pequeña. El código no se puede regenerar, cuando el generador puede generar tantos códigos diferentes, que a partir de una sección del código individual no se puede concluir acerca de su continuación. El generador genera la secuencia de código al nivel más bajo posible de operaciones-Bit. No se utilizan valores de variable como base para el cálculo de las secuencias de código sino únicamente estados de elementos de memoria individuales, como o por ejemplo flip-flops o registros de desplazamiento conectados para forma una serie. De ello resulta la mayor eficiencia posible en relación con el número de elementos de conmutación utilizados, por un lado, y con respecto a la longitud total de las secuencias de código generadas así como al número de los diferentes códigos que se pueden generar, por la otra. Además, se asegura con ello que el generador de código puede producir la velocidad de producción más alta posible.

Según la invención la secuencia de código generada por el generador de código es modificada gracias a que entre dos elementos de memoria que se encuentran en la serie generadora de código está introducida otra puerta lógica EXOR a cuya primera entrada se conecta la salida de un primer elemento de memoria y que permite alimentar la entrada por la salida de otro elemento de memoria cualquiera que se encuentra en la serie y que, finalmente, alimenta con la salida de la puerta lógica EXOR la entrada del elemento de memoria conectado al primer elemento de memoria en la dirección del flujo de la serie.

Para que partiendo de una serie de elementos de memoria vacíos se genere un código, el cual presente una longitud máxima en relación con el número de elementos de memoria utilizados, debe haber en la totalidad de la serie cerrada de elementos de memoria un único inversor. Naturalmente la función del inversor puede estar reunida con la función de la puerta lógica EXOR en un elemento de conmutación, por ejemplo con la ayuda de una puerta lógica EXNOR.

Para programar códigos diferentes se hacen conectables y desconectables preferentemente la o las puertas lógicas EXOR, en cuanto a su función recursiva, dependientes de un contenido de memoria de código interno. Con este propósito, se ha perfeccionado la invención de tal manera que la línea que conecta la segunda entrada de la por lo menos una puerta lógica EXOR y la salida del otro elemento de memoria que se encuentra en la serie generadora de código está conectada de tal manera una puerta lógica Y, que la salida de la puerta lógica Y está conectada con la segunda entrada de la puerta lógica EXOR, la primera entrada de la puerta lógica Y lo está con la salida del otro elemento de memoria que se encuentra en la serie generadora de código y la segunda entrada de la puerta lógica Y lo está con la salida de un elemento de memoria que sirve para la programación. El estado del elemento de memoria correspondiente que sirve... [Seguir leyendo]

Reivindicaciones:

1. Generador de código con una pluralidad de elementos de memoria (FF1, 2, ...n) conectados para formar una serie

(R) que genera código, por ejemplo, flip-flops, estando conectada la salida del último elemento de memoria (FF5) en la serie (R) con la entrada del primer elemento de memoria (FF1) de la serie (R) para formar un circuito, estando prevista por lo menos una puerta lógica EXOR (EXORp1), cuya primera entrada (1) está conectada con la salida de un elemento de memoria (FF1) que se encuentra en la serie (R) generadora de código, cuya segunda entrada (2) lo está con la salida de otro elemento de memoria (FF3) que se encuentra en la serie (R) generadora de código y cuya salida (3) está conectada con la entrada del elemento de memoria (FF2) posterior al elemento de memoria (FF1) conectado con la primera entrada (1) de la puerta lógica EXOR (EXORp1) en la serie (R) generadora de código, caracterizado porque las salidas y por lo menos una entrada de los elementos de memoria están conectadas de manera recursiva con interconexión de por lo menos una puerta lógica EXOR (EXORp1), en la línea que conecta la segunda entrada (2) de dicha por lo menos una puerta lógica EXOR (EXORp1) y la salida del otro elemento de memoria (FF3) que se encuentra en la serie (R) generadora de código está conectada de tal manera una puerta lógica Y (Yp1), que la salida (4) de la puerta lógica Y (Y01) está conectada con la segunda entrada (2) de la puerta lógica EXOR (EXORp1), la primera entrada (6) de la puerta lógica Y (Yp1) lo está con la salida del otro elemento de memoria (FF3) que se encuentra en la serie (R) generadora de código y la segunda entrada (5) de la puerta lógica Y (Yp1) lo está con la salida de un elemento de memoria (FFp1) programado mediante código y porque la salida de un elemento de memoria (FF5) que se encuentra en la serie (R) generadora de código está conectada con la entrada de un inversor (INV) y la salida del inversor (INV) lo está con la entrada de otro elemento de memoria (FF1) dispuesto en la serie (R) generadora de código.

2. Generador de código según la reivindicación 1, caracterizado porque está prevista una pluralidad de puertas lógicas EXOR (EXORp1, p2, p3, p4), cuya primera entrada es alimentada en cada caso por un elemento de memoria (FF1, 2, 3, 4) que se encuentra en la salida de una serie (R) generadora de código y cuya segunda entrada es alimentada, en cada caso, por la salida de otro elemento de memoria (FF8, 15, 20, 23) que se encuentra en la serie (R) generadora de código, el cual está alejado, en cada caso, en un número de elementos de memoria en la dirección de circulación de la serie (R) de elemento de memoria (FF1, 2, 3, 4) conectado, en cada caso, con la primera entrada, el cual corresponde, en cada caso, a un número primo diferente, que es mayor que 1 y no es una suma parcial del número total de elementos de memoria (FF1, 2, ...n) conectados en la serie (R).

3. Generador de código según la reivindicación 1 ó 2, caracterizado porque está previsto una pluralidad de elementos de memoria (FFp1, p2, p3, p4, ...pn) programadores de código, asignados en cada caso a una puerta lógica Y (Yp1, p2, p3, p4) y a una puerta lógica EXOR (EXORp1, p2, p3, p4) y que están conectados en una serie (RR) cerrada formando un circuito y estando asociada por lo menos una puerta lógica EXOR (EXORpp1), cuya primera entrada está conectada con la salida de un elemento de memoria (FFp6) que se encuentra en la serie (RR) programadora de código, cuya segunda entrada lo está con la salida de otro elemento de memoria (FFp5) que se encuentra en la serie (RR) programadora de código y cuya salida lo está con la entrada del elemento de memoria (FFp1) que, en la serie (RR) programadora de código, viene a continuación del elemento de memoria (FFp6) conectado con la primera entrada de la puesta lógica EXOR (EXORpp1).

4. Generador de código según la reivindicación 3, caracterizado porque en la línea que conecta la segunda entrada de dicha por lo menos una puerta lógica EXOR (EXORpp1) y la salida del otro elemento de memoria (FFp3) que se encuentra en la serie (RR) programadora de código está conectada de tal manera una puerta lógica Y (Ypp1) que la salida de la puerta lógica Y (Ypp1) está conectada con la segunda entrada de la puerta lógica EXOR (EXORpp1), la primera entrada de la puerta lógica Y (Ypp1) lo está con la salida del otro elemento de memoria (FFp3) que se encuentra en la serie (RR) programadora de código y la segunda entrada de la puerta lógica Y (Ypp1) lo está con la salida de un elemento de memoria (FFpp5) que sirve para la programación de la serie (RR) programadora de código.

5. Generador de código según la reivindicación 4, caracterizado porque está prevista una pluralidad de elementos de memoria (FFpp1, pp2, pp3, pp4, ...ppn) que sirven para la programación de la serie (RR) programadora de código, asociados, en cada caso, a una puerta lógica Y (Ypp1) y a una puerta lógica EXOR (EXORpp1) y que están conectados en una serie (RRR) que forma un circuito y que está prevista por lo menos una puerta lógica EXOR (EXORppp1), cuya primera entrada está conectada con la salida de un elemento de memoria (FFpp1) que se encuentra en la serie (RRR), cuya segunda entrada está conectada con la salida de otro elemento de memoria (FFpp3) que se encuentra en la serie (RRR) y cuya salida está conectada con la entrada del elemento de memoria (FFpp2) que viene a continuación del elemento de memoria (FFpp1) conectada, en la serie (RRR), con la primera entrada de la puerta lógica EXOR (EXORppp1).

6. Generador de código según una de las reivindicaciones 1 a 5, caracterizado porque presenta por lo menos una conexión para por lo menos un segundo generador de código, estructurado idéntico, de manera que ambos generadores de código puedan ser alimentados al mismo tiempo con la misma cadencia de programa.

7. Dispositivo para la emisión y recepción de informaciones encriptadas con por lo menos dos generadores de código según una de las reivindicaciones 1 a 6, caracterizado porque los generadores de código presentan, en cada caso, por lo menos una conexión para la alimentación simultánea de los elementos de memoria (FFp1, p2, p3, p4)

programadores de código de todos los generadores de código conectados con la misma cadencia de programa, de manera que los elementos de memoria (FFp1, p2, p3, ...pn) programadores de código de todos los generadores de código conectados recorran al mismo tiempo todas las posibles combinaciones de estado y que en caso de separación simultánea de los generadores de código de la cadencia de programa estén provistos de la misma

5 programación.

8. Dispositivo según la reivindicación 7, caracterizado porque los generadores de código presentan, en cada caso, dos conexiones para la alimentación simultánea de los elementos de memoria (FFp1, p2, p3, ...pn) programadores de código y de los elementos de memoria (FFpp1, pp2, pp3, ...ppn) que sirven para la programación de los elementos de 10 memoria (FFp1, p2, p3, ...pn) programadores de código de todos los generadores de código conectados con dos cadencias de programa que corren de manera independiente, recorriendo los elementos de memoria (FFpp1, pp2, pp3, ...ppn) que sirven para la programación de los elementos de memoria (FFp1, p1, p3, p4) programadores de código todas las posibles combinaciones de estado por lo menos una vez y los elementos de memoria (FFp1, p2, p3, ...pn) programadores de código de todos los programadores conectados recorren simultáneamente un número determinado de todas las posibles combinaciones de estado y, tras la separación simultánea de los generadores de código de las cadencias de programa, todos los generadores de código están provistos de la misma programación.

Patentes similares o relacionadas:

Generación de número aleatorio, del 6 de Enero de 2016, de Airbus Defence and Space Limited: Método de generación de un número aleatorio en un vehículo espacial que incluye las etapas de:

- proporcionar una RAM que tiene una salida que puede […]

Generación de número aleatorio, del 6 de Enero de 2016, de Airbus Defence and Space Limited: Método de generación de un número aleatorio en un vehículo espacial que incluye las etapas de:

- proporcionar una RAM que tiene una salida que puede […]

Método y aparato para la configuración IV no lineal en generadores de secuencia de clave, del 7 de Enero de 2015, de GEMALTO SA: Metodo para realizar una "etapa de configuracion de desafio lector en una fase de autenticación", de acuerdo con un protocolo de autenticación y cifrado MIFAREO utilizando cifrado […]

METODO Y APARATO PARA GENERAR UNA CORRIENTE DE CIFRA., del 16 de Abril de 2007, de INTERDIGITAL TECHNOLOGY CORPORATION: Un generador de corriente de cifra que incluye un primer (L1) y un segundo (L2) registros de desplazamiento con realimentación lineal, cada uno con una entrada […]

PROCEDIMIENTO DE PROTECCION MEJORADA DE UN SISTEMA DE CIFRADO DE CODIGO DE REDUNDANCIA CICLICA., del 1 de Octubre de 2000, de LEAR AUTOMOTIVE DEARBORN, INC.: LA INFORMACION DIGITAL ES ENCRIPTADA REALIZANDO PRIMERO UN NUMERO PRESELECCIONADO DE ITERACIONES CRC O DE CIRCUMBALACIONES PARCIALES MEDIANTE MULTIPLICACION […]

METODO PARA PROTEGER UNA TARJETA PORTATIL, del 16 de Diciembre de 2007, de KONINKLIJKE KPN N.V.: Método para proteger una tarjeta portátil provista de por lo menos un algoritmo criptográfico para cifrar datos y/o autenticar la tarjeta, contra la obtención […]

METODO PARA PROTEGER UNA TARJETA PORTATIL, del 16 de Diciembre de 2007, de KONINKLIJKE KPN N.V.: Método para proteger una tarjeta portátil provista de por lo menos un algoritmo criptográfico para cifrar datos y/o autenticar la tarjeta, contra la obtención […]