METODO Y DISPOSITIVO PARA ACCEDER A LOS DATOS DE UNA MEMORIA DE MENSAJES DE UN MODULO DE COMUNICACION.

Método para el acceso de datos de una memoria de mensajes (300),

para lo cual se prevee una primera memoria búfer (201, 202), caracterizado porque, la primera memoria búfer se encuentra dividida en una sub memoria búfer (400, 701) y una memoria espejo (401, 700) para la sub memoria búfer, por lo cual durante un acceso a los datos se ejecutan los siguientes pasos:

- entrada de datos en la sub memoria búfer e

- intercambio del acceso de la sub memoria búfer y de la memoria espejo, de manera que

- los siguientes datos puedan ser ingresados en la memoria espejo, mientras que los datos ingresados puedan al mismo tiempo ser extraídos de la sub memoria búfer

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2005/053077.

Solicitante: ROBERT BOSCH GMBH.

Nacionalidad solicitante: Alemania.

Dirección: POSTFACH 30 02 20,70442 STUTTGART.

Inventor/es: HARTWICH, FLORIAN, HORST,CHRISTIAN, BAILER,FRANZ.

Fecha de Publicación: .

Fecha Concesión Europea: 16 de Diciembre de 2009.

Clasificación Internacional de Patentes:

- H04L12/56Q1

Clasificación PCT:

- H04L12/56

Fragmento de la descripción:

Método y dispositivo para acceder a los datos de una memoria de mensajes de un módulo de comunicación.

Estado actual de la técnica

La presente invención hace referencia a un método y un dispositivo para acceder a los datos de una memoria de mensajes de un módulo de comunicación a través de la entrada y la salida de datos a o desde la memoria de mensajes de un módulo de comunicación conforme a la reivindicación independiente.

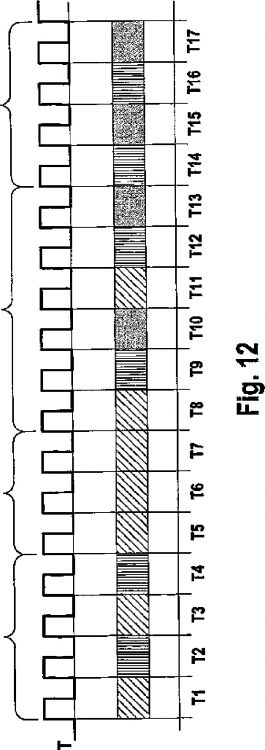

La conexión en red de dispositivos de control, sensores y actuadores con ayuda de un sistema de comunicación y de un sistema ómnibus, por consiguiente, de un enlace de comunicación, ha aumentado en forma drástica en los últimos años, tanto en la construcción de vehículos modernos como también en la construcción de máquinas, especialmente en el sector de las máquinas-herramienta, y en la automatización. A través de la distribución de funciones en varios dispositivos de control pueden obtenerse efectos sinérgicos. Se habla así de sistemas distribuidos. La comunicación entre diferentes estaciones tiene lugar cada vez más frecuentemente mediante un sistema ómnibus, o mediante un enlace de comunicación. La circulación de la información en el sistema ómnibus, los mecanismos de entrada y salida, así como también el control de errores están regidos por un protocolo. Dentro de este área es conocido el protocolo CAN, así como también los protocolos TTCAN y FlexRay que sirven de base actualmente a la especificación del protocolo FlexRay. Flexray es un sistema ómnibus rápido, determinista y tolerante a fallos, en especial para la utilización en un vehículo. El protocolo FlexRay trabaja conforme al acceso múltiple por división de tiempo (TDMA), en el cual los componentes -las partes- de los mensajes a transmitir son adjudicados en ranuras de tiempo, donde éstas tienen una entrada exclusiva al enlace de comunicación. Un translado similar tiene lugar en TTCAN. Las ranuras de tiempo se repiten en un ciclo determinado, de manera que el instante en el que se transmite el mensaje mediante el bus, puede predecirse con exactitud, y el acceso al bus se produce determinísticamente. Para aprovechar óptimamente el ancho de banda para la transmisión del mensaje en el sistema ómnibus, FlexRay subdivide el ciclo en una parte dinámica y una parte estática. Las ranuras de tiempo determinadas se encuentran así en la parte estática al comienzo de un ciclo de bus. En la parte dinámica las ranuras de tiempo se adjudican dinámicamente. De esta forma se posibilita entonces el exclusivo acceso al bus cada vez sólo por un corto tiempo, conocido como minislots (miniranuras de tiempo). Sólo cuando un acceso al bus tiene lugar dentro de una miniranura, se alarga el intervalo durante el tiempo necesario. De esta manera, el ancho de banda se utiliza sólo cuando efectivamente se le necesita. De este modo FlexRay comunica mediante dos líneas separadas con una velocidad máxima de 10 MB. Ambos canales corresponden a la capa física, en especial al modelo de capas del OSI (Open System Architecture). Estos canales sirven efectivamente para lograr una transmisión de mensajes redundante y tolerante a fallos, por lo cual se duplicaría entonces la velocidad. FlexRay puede, sin embargo, ser activado también con velocidades más bajas. Para realizar funciones sincrónicas y optimizar el ancho de banda mediante pequeñas distancias entre los mensajes, los componentes distribuidos en la red de comunicación FlexRay, los participantes, requieren de una base de tiempo común, conocida como tiempo global.

Para lograr la sincronización de tiempos se transmiten colas de mensajes a la parte estática del ciclo, de manera tal que con la ayuda de un algoritmo especial correspondiente a la especificación FlexRay, el tiempo local de un componente es corregido, logrando así que todos los relojes marchen sincrónicamente en una secuencia de tiempo global. Esta sincronización es similar en la red de comunicación TTCAN.

Un nodo de red FlexRay o un participante FlexRay o procesador central contiene un procesador participante o procesador central, un controlador FlexRay o controlador de comunicación así como una control del bus contiene un controlador del bus. Con ello el procesador central o procesador participante envía y procesa los datos transmitidos por el controlador de comunicación FlexRay. Para la comunicación en una red FlexRay pueden configurarse mensajes u objetos de mensajes, con por ejemplo, hasta 254 bytes de datos. Para transmitir estos mensajes u objetos de mensajes entre la capa física, por tanto entre el enlace de comunicación y el procesador central, se emplea un módulo de comunicación, en particular un controlador de comunicación.

Los accesos a la memoria de mensajes de un módulo de comunicación, en especial de un controlador de comunicación FlexRay se producen tanto a través de la unidad del procesador central, por tanto del procesador CPU, como también mediante módulos de interfaces en la capa física. El acceso al procesador CPU comprende así la escritura y la lectura de datos de configuración, de datos de estado y de datos que propiamente se transmiten. El acceso del procesador CPU a la capa física comprende la lectura de mensajes enviados, el almacenamiento de mensajes recibidos, asegurando en ambos casos la integridad de los mensajes mediante medidas adecuadas.

La US 2003/0174708 A1 presenta una memoria de alta velocidad con una estructura modular. En ella se prevee un almacenamiento temporal en particular de mensajes, para garantizar por completo su recepción. En condiciones atípicas es posible además que el espacio previsto no sea suficiente.

Es objeto de la presente invención el optimizar la transmisión de datos entre el procesador CPU o procesador participante y la memoria de mensajes con respecto a la velocidad de transmisión y a la integridad de los datos.

Ventajas de la invención

Para alcanzar este objeto la invención se basa en un método y en un dispositivo para acceder a datos de una memoria de mensajes, mediante la entrada y la salida de datos en o de la memoria de mensajes, con lo cual la memoria se conecta a una disposición de búfers (espacios de memoria).

La disposición de búfers comprende un primer búfer, el cual en forma conveniente se encuentra dividido en una sub memoria búfer y una memoria espejo para la sub memoria búfer, con lo cual se ejecutan los siguientes pasos: Entrada de datos en la memoria del búfer correspondiente e intercambio del acceso en la sub memoria búfer y la memoria espejo, de manera que los siguientes datos puedan ser ingresados en la memoria espejo, mientras que los datos ingresados ya son devueltos de la sub memoria búfer en la dirección de transmisión prevista.

Esto significa que, de manera ventajosa, se prevee un búfer para el acceso a datos de una memoria de mensajes, el cual contiene una sub memoria búfer y una memoria espejo, así como también los medios a través de los cuales se intercambia el acceso a la sub memoria búfer y a la memoria espejo. La invención presentada es ventajosa, ya que mediante este intercambio, la velocidad de transmisión puede aumentar de forma evidente y mediante la bipartición del búfer es posible una mutua lectura y escritura, de manera que durante la transferencia de datos se suprime un acceso simultáneo a celdas de memoria iguales, asegurándo así la integridad de los datos.

En una presentación ventajosa de la invención se instala, para acceder a los datos de una memoria de mensajes de un módulo de comunicación, un búfer con una memoria de entrada y una memoria de salida, con lo cual la memoria de entrada contiene una primera sub memoria búfer y una primera memoria espejo y la memoria de salida contiene una segunda sub memoria búfer y una segunda memoria espejo. A su vez se prevee un primer medio para intercambiar el acceso de la primera sub memoria búfer y la primera memoria espejo, y un segundo medio para para intercambiar el acceso de la segunda sub memoria búfer y la segunda memoria espejo.

Esto significa que la invención describe un dispositivo para la transferencia de datos entre un procesador CPU y una memoria de mensajes a través del intercalado de un búfer, en particular de una memoria de entrada para la escritura y una memoria de salida para la lectura para desacoplar los accesos de las unidades de transmisión y de recepción. De esta forma el administrador o gestor del mensaje dirige y controla todos los accesos relativos al mensaje, asegurando así la integridad de los mensajes almacenados.

De manera aún más ventajosa se indica el intercambio de la sub memoria búfer y la memoria espejo...

Reivindicaciones:

1. Método para el acceso de datos de una memoria de mensajes (300), para lo cual se prevee una primera memoria búfer (201, 202), caracterizado porque, la primera memoria búfer se encuentra dividida en una sub memoria búfer (400, 701) y una memoria espejo (401, 700) para la sub memoria búfer, por lo cual durante un acceso a los datos se ejecutan los siguientes pasos:

2. Método conforme a la reivindicación 1, caracterizado porque, la memoria de mensajes es parte de un módulo de comunicación (100), por lo cual se pueden ingresar o devolver datos hacia o desde la memoria de mensajes (300), por lo que la memoria de mensajes (300) se encuentra conectada a una disposición de memoria búfer (201 y 202) y los datos se pueden transmitir en una primera dirección de transmisión hacia la memoria de mensajes y en una segunda dirección de transmisión desde la memoria de mensajes, por lo cual se preveen una primera y una segunda memoria búfer, por lo cual la disposición de memoria búfer presenta una primera memoria búfer como una memoria de acceso (201), en la primera dirección de transmisión, y en la segunda dirección de transmisión, la segunda memoria búfer se presenta como un búfer de memoria de salida (202) y la memoria de acceso y el búfer de memoria de salida se dividen respectivamente en una sub memoria búfer (400, 701) y una memoria espejo (401, 700) para la sub memoria búfer, por lo que en cada transmisión se ejecutan los siguientes pasos:

3. Método conforme a la reivindicación 2, caracterizado porque se marca el intercambio de acceso de la sub memoria búfer y la memoria espejo mediante un indicador.

4. Método conforme a la reivindicación 2, caracterizado porque, el intercambio de acceso de la sub memoria búfer y la memoria espejo se produce mediante un indicador.

5. Método conforme a la reivindicación 2, caracterizado porque se transmiten los datos en mensajes y los mensajes son provistos de un identificador de mensajes (IBRH, IBRS, OBRH, OBRS), por lo cual se produce el intercambio de acceso de la sub memoria búfer y la memoria espejo, cuando el indicador de mensaje se inscribe en un registro predeterminado (403, 404, 703, 704).

6. Método conforme a la reivindicación 2, caracterizado porque se transmiten los datos en mensajes y los datos se dividen en un mensaje, por lo menos en datos primarios (KD) y datos secundarios (D), por lo que, dependiendo de al menos un identificador de datos (LHSH, LDSH, LDSS, LHSS, RHSS, RDSS, RDSH, RHSH), sólo se transmiten los datos primarios (KD) o los datos secundarios (D).

7. Método conforme a la reivindicación 2, caracterizado porque, el acceso a los datos, se marca mediante un indicador (IBSYS, IBSYH, OBSYS), el cual se inscribe en un registro.

8. Método conforme a la reivindicación 5, caracterizado porque, una información puede ser transmitida desde el indicador mismo (IBSYS, IBSYH, OBSYS) o desde su posición en el registro y puede acceder a la sub memoria búfer o a la memoria espejo.

9. Método conforme a las reivindicaciones 5 ó 6, caracterizado porque, durante el intercambio de accesos, por lo menos una parte de las inscripciones de los registros, en especial los indicadores, se intercambian en el registro.

10. Método conforme a la reivindicación 2, caracterizado porque, el intercambio de accesos de la sub memoria búfer y de la memoria espejo se inician mediante un identificador conmutable (VIEW).

11. Método conforme a la reivindicación 2, caracterizado porque, un indicador de inicio (STXRH, REQ) se inscribe en un registro, para al menos una dirección de transmisión, cuando los datos deban escribirse en una memoria.

12. Disposición de búfer de memoria para el acceso a datos de una memoria de mensajes (300) de un módulo de comunicación (100) caracterizado porque, la primera memoria búfer (201, 202) contiene una sub memoria búfer (400, 701) y una memoria espejo (401, 700) de la sub memoria búfer, por lo que se preveen los medios, a través de los cuales se intercambia el acceso de la sub memoria búfer (400, 701) y de la memoria espejo (401, 700).

13. Disposición de búfer de memoria conforme a la reivindicación 12, caracterizado porque, la disposición de búfer de memoria presenta una primera memoria búfer y una segunda memoria búfer y la disposición de búfer de memoria se divide en un búfer de memoria de entrada (201) y un búfer de memoria de salida (202) y el búfer de memoria de entrada (201) contiene una primera sub memoria búfer (400) y una primera memoria espejo (401) de la sub memoria búfer y el búfer de memoria de salida (202) contiene una segunda sub memoria búfer (701) y una segunda memoria espejo (700), por lo que se preveen los medios primarios, a través de los cuales se intercambia el acceso a la primera sub memoria búfer (400) y la primera memoria espejo (401) y se preveen los medios secundarios, a través de los cuales se intercambia el acceso a la segunda sub memoria búfer (701) y la segunda memoria espejo (700).

14. Módulo de comunicación con una disposición de memoria búfer conforme a la reivindicación 12.

15. Módulo de comunicación con una disposición de memoria búfer conforme a la reivindicación 13.

Patentes similares o relacionadas:

PARTICIPANTE Y CONTROLADOR DE COMUNICACIONES DE UN SISTEMA DE COMUNICACIONES Y MÉTODO PARA LA IMPLEMENTACIÓN DE UNA FUNCIONALIDAD DE LA PUERTA DE ENLACE EN UN PARTICIPANTE DE UN SISTEMA DE COMUNICACIONES, del 12 de Mayo de 2011, de ROBERT BOSCH GMBH: Participante de un sistema de comunicaciones, donde el participante presenta un microprocesador , al menos dos controladores de comunicaciones (750a, 750b, […]

PARTICIPANTE Y CONTROLADOR DE COMUNICACIONES DE UN SISTEMA DE COMUNICACIONES Y MÉTODO PARA LA IMPLEMENTACIÓN DE UNA FUNCIONALIDAD DE LA PUERTA DE ENLACE EN UN PARTICIPANTE DE UN SISTEMA DE COMUNICACIONES, del 12 de Mayo de 2011, de ROBERT BOSCH GMBH: Participante de un sistema de comunicaciones, donde el participante presenta un microprocesador , al menos dos controladores de comunicaciones (750a, 750b, […]

SEÑALIZACION DE INTERVALO DE TIEMPO POR DIFUSION DIGITAL DE BANDA ANCHA, del 10 de Mayo de 2010, de NOKIA CORPORATION: Un sistema transmisor de difusión digital por intervalo de tiempo, que comprende:

un almacén temporal para recibir y almacenar temporalmente información de un proveedor […]

SEÑALIZACION DE INTERVALO DE TIEMPO POR DIFUSION DIGITAL DE BANDA ANCHA, del 10 de Mayo de 2010, de NOKIA CORPORATION: Un sistema transmisor de difusión digital por intervalo de tiempo, que comprende:

un almacén temporal para recibir y almacenar temporalmente información de un proveedor […]

ADAPTACION DE MEMORIA TEMPORAL DE REPRODUCCION BASADA EN LA LONGITUD DE RAFAGA DE AUDIO, del 6 de Mayo de 2010, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Equipo de usuario en un sistema de comunicaciones , comprendiendo el citado equipo de usuario un medio para recibir paquetes […]

ADAPTACION DE MEMORIA TEMPORAL DE REPRODUCCION BASADA EN LA LONGITUD DE RAFAGA DE AUDIO, del 6 de Mayo de 2010, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Equipo de usuario en un sistema de comunicaciones , comprendiendo el citado equipo de usuario un medio para recibir paquetes […]

Dispositivo inalámbrico y procedimiento para visualizar un mensaje, del 25 de Marzo de 2020, de QUALCOMM INCORPORATED: Un dispositivo inalámbrico para visualizar un mensaje, comprendiendo el dispositivo inalámbrico: un visualizador gráfico ; una unidad de comunicaciones inalámbricas […]

Método de indicación de disponibilidad de servicio para terminales de radiofrecuencia de corto alcance, con visualización de icono de servicio, del 26 de Febrero de 2020, de Nokia Technologies OY: Un método que comprende: recibir, en un dispositivo , información de icono de un dispositivo de origen en conexión con descubrimiento de dispositivo […]

Procedimiento y aparato para la transmisión de entramado con integridad en un sistema de comunicación inalámbrica, del 6 de Noviembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para el entramado de paquetes en un sistema de transmisión inalámbrico que admite transmisiones de radiodifusión, el procedimiento que comprende: […]

Aparato y procedimiento para usar en la realización de peticiones de repetición automática en sistemas de comunicaciones de acceso múltiple inalámbricas, del 6 de Noviembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para usar en un sistema de comunicaciones inalámbricas que comprende al menos una estación base y al menos dos terminales inalámbricos […]

Procedimiento y aparato para sistemas inalámbricos de activación, del 31 de Octubre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para controlar de forma inalámbrica una tarjeta de interfaz de red NIC (108 A-N) usando una red inalámbrica , con la NIC (108 A-N) […]

Procedimiento y aparato para sistemas inalámbricos de activación, del 31 de Octubre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para controlar de forma inalámbrica una tarjeta de interfaz de red NIC (108 A-N) usando una red inalámbrica , con la NIC (108 A-N) […]