PARTICIPANTE Y CONTROLADOR DE COMUNICACIONES DE UN SISTEMA DE COMUNICACIONES Y MÉTODO PARA LA IMPLEMENTACIÓN DE UNA FUNCIONALIDAD DE LA PUERTA DE ENLACE EN UN PARTICIPANTE DE UN SISTEMA DE COMUNICACIONES.

Participante (900) de un sistema de comunicaciones, donde el participante (900) presenta un microprocesador (102),

al menos dos controladores de comunicaciones (750a, 750b, 750c) y un bus periférico (820), y donde el microprocesador (102), mediante el bus periférico (820), se encuentra en contacto con los controladores de comunicaciones (750a, 750b, 750c) y, mediante los controladores de comunicaciones (750a, 750b, 750c) se encuentra conectado, respectivamente, a un enlace de comunicaciones (101a, 101b, 101c) del sistema de comunicaciones, mediante el cual son transmitidos mensajes, caracterizado p orque al menos uno de los controladores de comunicaciones (750a, 750c) presenta una interfaz activa (834), mediante la cual el controlador de comunicaciones (750a, 750c) se encuentra en contacto con el bus periférico (820) y mediante la cual el controlador de comunicaciones (750a, 750c) puede enviar datos e instrucciones a otro participante del bus periférico (820), y una unidad lógica para la implementación autónoma de una funcionalidad de una puerta de enlace, y porque los controladores de comunicaciones (750a, 750b, 750c) presentan respectivamente una memoria de mensajes (300a, 300b, 300c) para el almacenamiento temporal de mensajes desde el enlace de comunicaciones (101a, 101b, 101c) asociado al controlador de comunicaciones (750a, 750b, 750c), o para el enlace de comunicaciones (101a, 101b, 101c), donde la unidad lógica coordina y controla un enrutamiento autónomo de datos entre la memoria de mensajes (300a, 300b, 300c) de un controlador de comunicaciones (750a, 750b, 750c) y el microprocesador (102) o entre las memorias de mensajes (300a, 300b, 300c) del controlador de comunicaciones (750a, 750b, 750c)

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2006/067029.

Solicitante: ROBERT BOSCH GMBH.

Nacionalidad solicitante: Alemania.

Dirección: POSTFACH 30 02 20 70442 STUTTGART ALEMANIA.

Inventor/es: IHLE,MARKUS, TAUBE,JAN, LORENZ,TOBIAS.

Fecha de Publicación: .

Fecha Solicitud PCT: 4 de Octubre de 2006.

Clasificación Internacional de Patentes:

- G06F13/28 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 13/00 Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16). › utilizando la transferencia por ráfaga, p. ej. acceso directo a la memoria, robo de ciclo (G06F 13/32 tiene prioridad).

- H04L12/56Q1

Clasificación PCT:

- G06F13/28 G06F 13/00 […] › utilizando la transferencia por ráfaga, p. ej. acceso directo a la memoria, robo de ciclo (G06F 13/32 tiene prioridad).

- H04L12/56

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia.

PDF original: ES-2358609_T3.pdf

Fragmento de la descripción:

Participante y controlador de comunicaciones de un sistema de comunicaciones y método para la implementación de una funcionalidad de la puerta de enlace en un participante de un sistema de comunicaciones.

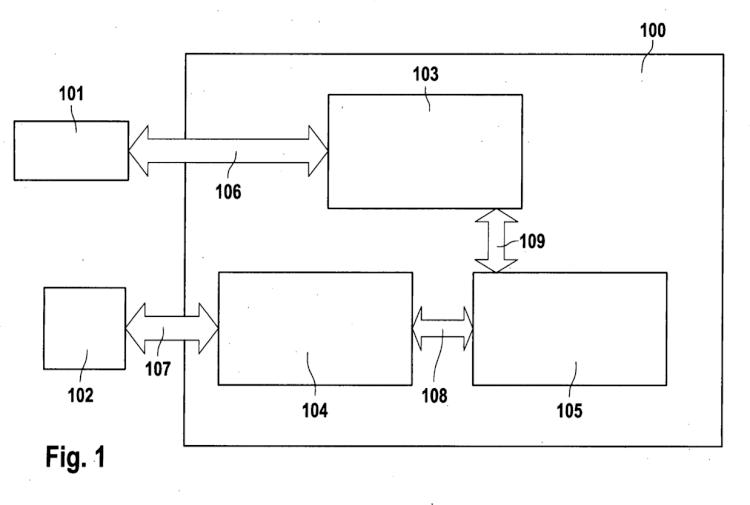

La presente invención hace referencia a un participante (el así llamado procesador central) de un sistema de comunicaciones. El participante presenta un microprocesador, al menos dos controladores de comunicaciones y un bus periférico. Mediante el bus periférico, el microprocesador se encuentra en contacto con los controladores de comunicaciones y, mediante los controladores de comunicaciones, respectivamente, se encuentra conectado a un enlace de comunicaciones del sistema de comunicaciones, mediante el cual son transmitidos mensajes.

Asimismo, la presente invención hace referencia también a un controlador de comunicaciones (el así llamado Communication Controller; CC) de un participante (el así llamado procesador central) de un sistema de comunicaciones. El participante presenta un microprocesador, los controladores de comunicaciones, de forma opcional otros controladores de comunicaciones y un bus periférico. Por un lado, el controlador de comunicaciones se encuentra en contacto con el microprocesador mediante el bus periférico y, por otro lado, se encuentra conectado a un enlace de comunicaciones del sistema de comunicaciones, mediante el cual son transmitidos mensajes.

Por último, la presente invención hace referencia también a un método para la implementación de una funcionalidad de una puerta de enlace dentro de un participante (llamado procesador central) de un sistema de comunicaciones. El participante presenta un microprocesador, al menos dos controladores de comunicaciones y un bus periférico. Mediante el bus periférico, los controladores de comunicaciones, por un lado, se encuentran en contacto con el microprocesador y, por otro lado, respectivamente, se encuentran conectados a un enlace de comunicaciones del sistema de comunicaciones, mediante el cual son transmitidos mensajes.

Estado del arte

La conexión en red de dispositivos de control, sensores y actuadores con ayuda de un sistema de comunicaciones y de un enlace de comunicaciones conformado como un sistema ómnibus ha aumentado en forma drástica en los últimos años, tanto en la construcción de vehículos modernos como también en la construcción de máquinas, especialmente en el sector de las máquinas-herramienta, y en la automatización. A través de la distribución de funciones en varios dispositivos de control pueden obtenerse efectos sinérgicos. Se habla así de sistemas distribuidos. La comunicación entre diferentes estaciones tiene lugar, frecuentemente, cada vez más a través de un enlace de comunicaciones conformado como un sistema ómnibus, o mediante un enlace de comunicaciones. La circulación de la información en el sistema ómnibus, los mecanismos de entrada y de salida, así como también el control de errores, están regidos por un protocolo.

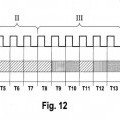

Dentro de esta área es conocido el protocolo FlexRay, donde la especificación v2.0 del protocolo FlexRay se constituye actualmente como una base. El protocolo Flexray es un sistema ómnibus rápido, determinista y tolerante a fallos, en especial para la utilización en un vehículo. La transmisión de datos, conforme al protocolo FlexRay, tiene lugar de acuerdo al método de acceso múltiple por división de tiempo (TDMA, por sus siglas en inglés), en el cual los componentes - las partes- de los mensajes a transmitir son adjudicados a ranuras de tiempo, donde éstas tienen una entrada exclusiva al enlace de comunicación.

La transmisión de datos mediante el enlace de comunicaciones tiene lugar en ciclos de transmisión que se repiten de forma regular, los cuales, respectivamente, se encuentran subdivididos en varias tramas de datos, conocidas también como ranuras de tiempo. Los participantes, así como los mensajes a ser transmitidos, son adjudicados a ranuras de tiempo determinadas, donde éstas tienen un acceso exclusivo al enlace de comunicaciones. Las ranuras de tiempo se repiten en los ciclos de transmisión determinados, de manera que puede predecirse con exactitud el instante en el que se transmite el mensaje mediante el bus, y el acceso al bus se produce determinísticamente.

Para aprovechar óptimamente el ancho de la banda para la transmisión del mensaje en el sistema ómnibus, FlexRay subdivide el ciclo de transmisión, también llamado ciclo del bus, en una parte dinámica y una parte estática. Las ranuras de tiempo determinadas se encuentran así en la parte estática al comienzo de un ciclo de bus. En la parte dinámica, las ranuras de tiempo se adjudican dinámicamente. De esta forma se posibilita entonces el exclusivo acceso al bus cada vez sólo por un corto tiempo, conocido como minislots (miniranuras de tiempo). Sólo cuando un acceso al bus tiene lugar dentro de una miniranura, se alarga la ranura durante el tiempo necesario. De esta manera, sólo se utiliza el ancho de banda cuando efectivamente se le necesita.

FlexRay comunica mediante dos líneas separadas físicamente del enlace de comunicaciones, con una velocidad máxima de 10 megabits (10 MBaud). De este modo, a los 5 ms, en algunos sistemas de comunicaciones incluso a 1 m o a 2,5 ms, es cerrado un ciclo del bus. Ambos canales corresponden a la capa física, en especial al modelo de capas del OSI (Open System Architecture). Estos canales sirven efectivamente para lograr una transmisión de mensajes redundante y tolerante a fallos, por lo cual se duplicaría entonces la velocidad. FlexRay puede, sin embargo, ser activado también con velocidades más bajas.

Para realizar funciones sincrónicas y optimizar el ancho de banda mediante pequeñas distancias entre los mensajes, los participantes, así como los componentes distribuidos en la red de comunicaciones, requieren de una base de tiempo común, conocida como tiempo global. Para lograr la sincronización de tiempos se transmiten mensajes de sincronización a la parte estática del ciclo, de manera tal que con la ayuda de un algoritmo especial correspondiente a la especificación FlexRay, el tiempo local de un participante es corregido, logrando así que todos los relojes marchen sincrónicamente en una secuencia de tiempo global.

Un participante FlexRay, el cual puede ser denominado también como nodo de red FlexRay o como procesador central, contiene un procesador del participante o un procesador central, un controlador FlexRay o controlador de comunicaciones, así como un control del bus contiene un controlador del bus. Con ello, el procesador del participante o el procesador central envía y procesa los datos transmitidos por el controlador de comunicaciones FlexRay. Para la comunicación en una red FlexRay pueden configurarse mensajes u objetos de mensaje, con por ejemplo, hasta 254 bytes de datos.

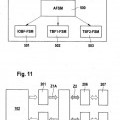

Para el acoplamiento de un enlace de comunicaciones FlexRay, mediante el cual son transmitidos mensajes a un participante FlexRay, de acuerdo a la solicitud DE 10 2005 034 744, la cual aún no había sido publicada el día de la solicitud de la presente invención, se emplea un módulo de comunicaciones FlexRay que mediante una interfaz del participante se encuentra conectado al participante y, mediante otra conexión, al enlace de comunicaciones. De este modo, para la transmisión de los mensajes entre el participante y el enlace de comunicaciones, se proporciona en el módulo de comunicaciones una disposición para el almacenamiento de los mensajes. La transmisión es controlada a través de una máquina de estado. El módulo de comunicaciones FlexRay puede estar conformado como un componente integral del controlador de comunicaciones FlexRay o como un componente separado.

En el módulo de comunicaciones se proporciona un módulo de la interfaz que se encuentra compuesto por dos partes, donde una de las partes del módulo es independiente del participante y la otra parte del módulo es específica del participante. La parte del módulo específica del participante o parte del módulo específica del cliente, denominada también como Customer CPU Interface (CIF), conecta un participante específico del cliente, en forma de un procesador CPU específico del participante, con el módulo de comunicaciones FlexRay. La parte del módulo independiente del participante, la cual es denominada también como Generis CPU Interface (GIF), representa una interfaz del CPU genérica, es decir común, mediante la cual, a través de las partes del módulo de comunicaciones específicas del cliente correspondientes, o sea Customer CPU Interfaces (CIFs), pueden ser conectados diferentes procesadores... [Seguir leyendo]

Reivindicaciones:

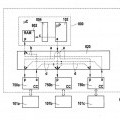

1. Participante (900) de un sistema de comunicaciones, donde el participante (900) presenta un microprocesador (102), al menos dos controladores de comunicaciones (750a, 750b, 750c) y un bus periférico (820), y donde el microprocesador (102), mediante el bus periférico (820), se encuentra en contacto con los controladores de comunicaciones (750a, 750b, 750c) y, mediante los controladores de comunicaciones (750a, 750b, 750c) se encuentra conectado, respectivamente, a un enlace de comunicaciones (101a, 101b, 101c) del sistema de comunicaciones, mediante el cual son transmitidos mensajes, caracterizado p orque al menos uno de los controladores de comunicaciones (750a, 750c) presenta una interfaz activa (834), mediante la cual el controlador de comunicaciones (750a, 750c) se encuentra en contacto con el bus periférico (820) y mediante la cual el controlador de comunicaciones (750a, 750c) puede enviar datos e instrucciones a otro participante del bus periférico (820), y una unidad lógica para la implementación autónoma de una funcionalidad de una puerta de enlace, y porque los controladores de comunicaciones (750a, 750b, 750c) presentan respectivamente una memoria de mensajes (300a, 300b, 300c) para el almacenamiento temporal de mensajes desde el enlace de comunicaciones (101a, 101b, 101c) asociado al controlador de comunicaciones (750a, 750b, 750c), o para el enlace de comunicaciones (101a, 101b, 101c), donde la unidad lógica coordina y controla un enrutamiento autónomo de datos entre la memoria de mensajes (300a, 300b, 300c) de un controlador de comunicaciones (750a, 750b, 750c) y el microprocesador (102) o entre las memorias de mensajes (300a, 300b, 300c) del controlador de comunicaciones (750a, 750b, 750c).

2. Participante (900) conforme a la reivindicación 1, caracterizado porque al menos unos de los controladores de comunicaciones (750a, 750b, 750c) presenta un módulo de comunicaciones (100a, 100b, 100c), el cual comprende una memoria de mensajes (300a, 300b, 300c) para el almacenamiento temporal de mensajes desde el enlace de comunicaciones (101a, 101b, 101c) asociado al controlador de comunicaciones (750a, 750b, 750c) o para el enlace de comunicaciones (101a, 101b, 101c), donde la unidad lógica coordina y controla un enrutamiento autónomo de datos entre la memoria de mensajes de un controlador de comunicaciones o entre la memoria de mensajes (300a, 300b, 300c) de al menos un módulo de comunicaciones (100a, 100b, 100c) y el microprocesador (102) o entre las memorias de mensajes (300a, 300b, 300c) de los controladores de comunicaciones (750a, 750b, 750c) y/o la memoria de mensajes (300a, 300b, 300c) de al menos un módulo de comunicaciones (100a, 100b, 100c).

3. Participante (900) conforme a la reivindicación 2, caracterizado porque cada módulo de comunicaciones (100a, 100b, 100c) presenta al menos una memoria búfer dispuesta entre la memoria de mensajes (300a, 300b, 300c) y el bus periférico (820), preferentemente al menos una memoria búfer de entrada (201a, 201b, 201c) y al menos una memoria búfer de salida (202a, 202b, 202c), donde la unidad lógica coordina y controla un enrutamiento autónomo de datos entre la memoria de mensajes (300a, 300b, 300c) de un controlador de comunicaciones (750a, 750b, 750c)

o entre al menos una memoria búfer (201a, 201b, 201c; 202a, 202b, 202c) de la memoria de mensajes (300a, 300b, 300c) de al menos un módulo de comunicaciones (100a, 100b, 100c) y el microprocesador (102), o entre las memorias de mensajes (300a, 300b, 300c) de los controladores de comunicaciones (750a, 750b, 750c) y/o al menos una memoria búfer (201a, 201b, 201c; 202a, 202b, 202c) de la memoria de mensajes (300a, 300b, 300c) de al menos un módulo de comunicaciones (100a, 100b, 100c).

4. Participante (900) conforme a una de las reivindicaciones 1 a 3, caracterizado porque la unidad lógica en el controlador de comunicaciones (750a, 750c) comprende una máquina de estado.

5. Participante (900) conforme a la reivindicación 4, caracterizado po rque la máquina de estado se encuentra estructurada de forma fija.

6. Participante (900) conforme a la reivindicación 4 ó 5, caracterizada porque cada controlador de comunicaciones (750a, 750c), el cual presenta una interfaz activa (834) y una unidad lógica, presenta un árbitro (836), el cual arbitra las operaciones de acceso concurrentes del microprocesador (102) y del motor de enrutamiento (830) en una memoria de mensajes (300a, 300c) del controlador de comunicaciones (750a, 750c) o en una memoria de mensajes (300a, 300c) de un módulo de comunicaciones (100a, 100c) o en al menos una memoria búfer (201a, 201c; 202a, 202c) de una memoria de mensajes (300a, 300c) de un módulo de comunicaciones (100a, 100c).

7. Participante (900) conforme a una de las reivindicaciones 1 a 6, caracterizado porque cada controlador de comunicaciones (750a, 750c), el cual posee una interfaz activa (834) y una unidad lógica, presenta un registro de control y/o de estado (838), al cual tiene acceso el microprocesador (102) para la configuración, la dirección y/o el monitoreo de la funcionalidad de la puerta de enlace.

8. Participante (900) conforme a una de las reivindicaciones 1 a 7, caracterizado porque cada controlador de comunicaciones (750a, 750c), el cual posee una interfaz activa (834) y una unidad lógica, presenta una memoria de enrutamiento (844), a la cual tiene acceso el microprocesador (102) para la configuración, la activación y/o el monitoreo de la funcionalidad de la puerta de enlace.

9. Participante (900) conforme a una de las reivindicaciones 1 a 8, caracterizado porque el participante (900) forma parte de un sistema de comunicaciones FlexRay, en el cual tiene lugar una transmisión de datos entre el participante

(900) y otros participantes FlexRay que se encuentran conectados al enlace de comunicaciones FlexRay (101), en base al protocolo FlexRay.

10. Método para la implementación de una funcionalidad de la puerta de enlace dentro de un participante (900) de un sistema de comunicaciones, donde el participante (900) presenta un microprocesador (102), al menos dos controladores de comunicaciones (750a, 750b, 750c) y un bus periférico (820), y donde los controladores de comunicaciones (750a, 750b, 750c), por un lado, se encuentran en contacto con el microprocesador (102) mediante el bus periférico (820) y, por otro lado, se encuentran conectados respectivamente a un enlace de comunicaciones (101a, 101b, 101c) del sistema de comunicaciones, mediante el cual son transmitidos mensajes, caracterizado porque al menos uno de los controladores de comunicaciones (750a, 750c) presenta una interfaz activa (834), mediante la cual el controlador de comunicaciones (750a, 750c) se encuentra en contacto con el bus periférico (820) y mediante la cual el controlador de comunicaciones (750a, 750c) puede enviar datos e instrucciones a otro participante del bus periférico (820) y porque la funcionalidad de la puerta de enlace es implementada a través de una unidad lógica en al menos un controlador de comunicaciones (750a, 750c), donde la unidad lógica coordina y controla un enrutamiento autónomo de datos entre una memoria de mensajes (300a, 300b, 300c) del controlador de comunicaciones (750a, 750b, 750c) y el microprocesador (102) o entre memorias de mensajes (300a, 300b, 300c) del controlador de comunicaciones (750a, 750b, 750c).

11. Método conforme a la reivindicación 10, caracterizado porque en el marco de la funcionalidad de la puerta de enlace son iniciadas y procesadas interrupciones, son fragmentados y defragmentados mensajes y son intercambiados mensajes entre controladores de comunicaciones (750a, 750b, 750c) del participante (900) y/o son intercambiados mensajes entre uno de los controladores de comunicaciones (750a, 750b, 750c) y el microprocesador (102).

12. Método conforme a la reivindicación 10 u 11, caracterizado porque el microprocesador (102) almacena información de control y de estado en un registro de control y/o de estado (838) de al menos un controlador de comunicaciones (750a, 750c) y, de este modo, la funcionalidad de la puerta de enlace es configurada, controlada y/o monitoreada.

13. Método conforme a una de las reivindicaciones 10 a 12, caracterizado porq ue el microprocesador (102) almacena información de enrutamiento en una memoria de enrutamiento (842) de al menos un controlador de comunicaciones (750a, 750c) y, de este modo, la funcionalidad de la puerta de enlace es controlada y/o monitoreada.

14. Método conforme a una de las reivindicaciones 10 a 13, caracterizado porque la unidad lógica, en al menos un controlador de comunicaciones (750a, 750c), comprende un motor de enrutamiento (830), donde son arbitradas las operaciones de acceso concurrentes del microprocesador (102) y del motor de enrutamiento (830) en la memoria de mensajes (300a, 300c) del controlador de comunicaciones (750a, 750c) o en una memoria de mensajes (300a, 300c) de un módulo de comunicaciones (100a, 100c) o en al menos una memoria búfer (201a, 201c; 202a, 202c) de la memoria de mensajes (300a, 300c) del módulo de comunicaciones (100a, 100c).

15. Método conforme a una de las reivindicaciones 10 a 14, caracterizado porque para el copiado activo de datos en una memoria de mensajes (300b, 300c) de otro controlador de comunicaciones (750b, 750c), los siguientes pasos son ordenados y controlados de forma autónoma por la unidad lógica de al menos un controlador de comunicaciones (750a): - representación de forma visible de los datos recibidos en una memoria búfer (202a) de al menos un controlador de comunicaciones (750a); - creación de una copia de los datos recibidos en un rango de direcciones que puede ser configurado, de un elemento de memoria (802) asociado al microprocesador (102) o en una memoria búfer (201b, 201c) de otro controlador de comunicaciones (750b, 750c), a través de operaciones de acceso de escritura mediante la interfaz activa (834); y – cuando una copia de datos es creada en la memoria búfer (201b, 201c) del otro controlador de comunicaciones (750b, 750c), inicio de una transferencia de los datos almacenados desde la memoria búfer (201b, 201c) hacia una memoria de mensajes (300b, 300c) del otro controlador de comunicaciones (750b, 750c).

16. Método conforme a una de las reivindicaciones 10 a 15, caracterizado porque para el copiado activo de datos desde una memoria de mensajes (300b, 300c) de otro controlador de comunicaciones (750b, 750c), los siguientes pasos son ordenados y controlados de forma autónoma por la unidad lógica de al menos un controlador de comunicaciones (750a): - representación de forma visible de los datos en una memoria búfer (202b, 202c) del otro controlador de comunicaciones (750b, 750c); creación de una copia del contenido de un elemento de memoria (802) asociado al microprocesador (102) o de la memoria búfer (202b, 202c) del otro controlador de comunicaciones (750b, 750c) en un rango de direcciones que puede ser configurado, de al menos una memoria búfer (201a) del controlador de comunicaciones (750a), a través de operaciones de acceso de lectura mediante la interfaz activa

(834); e -inicio de una transferencia de los datos almacenados desde al menos una memoria búfer (201a) hacia una memoria de mensajes (300a) del módulo de comunicaciones (100a) del controlador de comunicaciones (750a).

17. Método conforme a la reivindicación 15 ó 16, caracterizado porque el método es iniciado y controlado mediante tiempo, a través de la recepción de datos, en particular de un mensaje, mediante una activación a través de un controlador de comunicaciones (750a, 750c) con una interfaz activa (834), o mediante una activación a través del microprocesador (102).

Patentes similares o relacionadas:

Sistema de procesamiento de datos y método de procesamiento de datos, del 1 de Enero de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un sistema de procesamiento de datos , que comprende una unidad central de procesamiento, CPU , una memoria , un controlador […]

Solución Ethernet universal, del 2 de Octubre de 2019, de SCHNEIDER ELECTRIC INDUSTRIES SAS: Un circuito integrado monolítico , que comprende: al menos un núcleo de procesador de aplicaciones utilizable para ejecutar una aplicación industrial y código de […]

Comunicación de audio multicanal en un sistema de bus multimedia inter-chip serie de baja potencia (SLIMbus), del 28 de Marzo de 2019, de QUALCOMM INCORPORATED: Una fuente de audio que comprende: un puerto de salida multicanal (302(X)) configurado para ser acoplado a un bus de multiplexado por división de tiempo, TDM, que comprende […]

Método de migración en directo de máquina virtual, método de procesamiento de datos de memoria de máquina virtual, servidor y sistema de máquina virtual, del 27 de Marzo de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de procesamiento de datos de memoria de máquina virtual, aplicado a un sistema de máquina virtual, en donde el sistema de máquina virtual comprende una […]

Sistema informático, método para acceder a un terminal de interconexión de componentes periféricos exprés y equipo, del 26 de Octubre de 2018, de HUAWEI TECHNOLOGIES CO., LTD.: Un proxy de acceso, en donde el proxy de acceso se aplica a un sistema informático, el sistema informático comprende un procesador y un bus de interconexión […]

Método de lectura/escritura de fichero y terminal móvil, del 14 de Diciembre de 2015, de HUAWEI DEVICE CO., LTD: Un método de lectura/escritura de fichero utilizado en un terminal móvil, que comprende:

determinar si un fichero objeto de lectura […]

Método de lectura/escritura de fichero y terminal móvil, del 14 de Diciembre de 2015, de HUAWEI DEVICE CO., LTD: Un método de lectura/escritura de fichero utilizado en un terminal móvil, que comprende:

determinar si un fichero objeto de lectura […]

Sistema y método para permitir la extracción rápida de datos de imagen entrelazados, del 3 de Diciembre de 2014, de Core Wireless Licensing S.a.r.l: Método de procesado de una unidad de datos entrelazados que incluye una pluralidad de fragmentos de datos de un primer tipo y una pluralidad de […]

Adaptadores de habilitación/deshabilitación de un entorno de ordenadores, del 12 de Febrero de 2014, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para habilitar adaptadores en un entorno de ordenadores, que comprende las etapas de: responder para ejecutar una instrucción de Procesador Lógico de […]