COMPARACION CRUZADA BASADA EN MEMORIA PARA SISTEMAS SOMETIDOS A VERIFICACION CRUZADA.

Un ordenador multiprocesador (10) que tiene al menos un primero y un segundo procesador (20,

21, 22) y un sistema de comparación cruzada, comprendiendo dicho sistema de comparación cruzada: una primera capa de búferes (40, 41, 42) que comprende una primera área de almacenaje para almacenar información proveniente del primer procesador (20) y una segunda área de almacenaje para almacenar información proveniente del segundo procesador (21); una segunda capa de búferes (50, 51, 52) que comprende una tercera área de almacenaje para almacenar la información proveniente de dicha primera área de almacenaje y la información proveniente de dicha segunda área de almacenaje, y una cuarta área de almacenaje para almacenar la información proveniente de dicha primera área de almacenaje y la información proveniente de dicha segunda área de almacenaje, en donde cada una de dichas áreas de almacenaje primera, segunda, tercera y cuarta se implementa dentro de una RAM multipuerto (30) y comprende al menos un búfer asignado solamente a su área de almacenaje dentro de dicha RAM multipuerto (30), comprendiendo además dicho sistema de comparación cruzada una lógica interna (60, 61, 62) dispuesta dentro de dicha RAM multipuerto (30), estando configurada dicha lógica interna (60, 61, 62) para transferir de forma síncrona la información de dicha primera área de almacenaje y dicha segunda área de almacenaje a dicha tercera área de almacenaje y a dicha cuarta área de almacenaje, en el que dicho primer procesador (20) está configurado para leer la información de dicha tercera área de almacenaje y para comparar datos almacenados en la tercera área de almacenaje provenientes de la primera área de almacenaje con datos almacenados en la tercera área de almacenaje provenientes de la segunda área de almacenaje a fin de determinar si la información almacenada en dicha tercera área de almacenaje proveniente de la primera área de almacenaje es idéntica a la información almacenada en la tercera área de almacenaje proveniente de la segunda área de almacenaje; y en el que dicho segundo procesador (21) está configurado para leer la información de dicha cuarta área de almacenaje y para comparar datos almacenados en la cuarta área de almacenaje provenientes de la primera área de almacenaje con datos almacenados en la cuarta área de almacenaje provenientes de la segunda área de almacenaje a fin de determinar si la información almacenada en dicha cuarta área de almacenaje proveniente de la primera área de almacenaje es idéntica a la información almacenada en la cuarta área de almacenaje proveniente de la segunda área de almacenaje

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E05024885.

Solicitante: ALCATEL.

Nacionalidad solicitante: Francia.

Dirección: 54, RUE LA BOETIE,75008 PARIS.

Inventor/es: POPESCU,MARIO, BARR,STEPHEN, TRICA,ALEXANDER.

Fecha de Publicación: .

Fecha Solicitud PCT: 15 de Noviembre de 2005.

Fecha Concesión Europea: 5 de Agosto de 2009.

Clasificación Internacional de Patentes:

- G06F11/16C2

- G06F11/16T4

- G06F11/18N2R

Clasificación PCT:

- G06F11/16 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › Detección o corrección de errores en un dato por redundancia en el hardware.

- G06F11/18 G06F 11/00 […] › utilizando un enmascaramiento pasivo del defecto de los circuitos redundantes, p. ej. por lógica combinatoria de los circuitos redundantes, por circuitos de decisión mayoritaria.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Fragmento de la descripción:

Comparación cruzada basada en memoria para sistemas sometidos a verificación cruzada.

1. Campo de la invención

Comparación cruzada para sistemas que operan en una configuración multiprocesador, tales como configuraciones duales 2 de 2 y configuraciones triplicadas 2 de 3 o alguna otra configuración multiprocesador.

2. Descripción de la técnica relacionada

Como quiera que han aumentado las velocidades de reloj de las unidades CPU y se han hecho más comunes las arquitecturas multiprocesador, las capacidades de las prestaciones de procesamiento han superado las de la memoria RAM tradicional. Una solución de este problema ha sido la adopción de una RAM multipuerto.

Una RAM multipuerto se presenta en muchas configuraciones que proporcionan acceso a un espacio de memoria compartida a través de varios puertos de entrada y de salida. Cada vez es más común la capacidad de escribir varios datos simultáneamente en el dispositivo a través de puertos separados, Cuando se escriben simultáneamente datos en el mismo lugar desde dos o más puertos, no queda garantizada la integridad de los datos. El lugar de memoria direccionado podría contener datos nuevos, datos viejos o algún valor transicional. Para mitigar este problema se requiere una lógica adicional destinada a implementar un arbitraje. El arbitraje consiste en coordinar lugares de acceso a memoria por parte de los procesadores.

Algunas aplicaciones de sistemas de computación digital, por ejemplo, sistemas vitales y sistemas críticos para una misión, requieren un alto grado de seguridad. Por ejemplo, para un funcionamiento seguro, un ordenador de control del vuelo de una aeronave depende de una operación de computación continua exenta de errores durante todo el período de vuelo. Deberá reconocerse que una operación exenta de errores requiere la eliminación de defectos o el confinamiento de éstos dentro del sistema de computación digital. Además de demandas de fiabilidad cada vez mayores, es necesario un sistema de computación rápida con un rendimiento total incrementado para sistemas de control de vuelo y otros sistemas vitales.

Para proporcionar integridad de los datos, más de un procesador determina si existe discrepancia en la información que se está transfiriendo simultáneamente por un bus. La comparación de datos para obtener resultados altamente precisos se denomina frecuentemente "comparación cruzada". Por ejemplo, efectuando una comparación cruzada de resultados computacionales producidos por diferentes procesadores se proporciona una alta integridad de los datos.

Los actuales sistemas de comparación cruzada que operan en una configuración multiprocesador son lentos, requieren mucho software y son complicados en su instalación. Hay varias soluciones actualmente disponibles. Una solución utilizada para sistemas duales requiere una conexión de puertos paralelo o serie. Ambas soluciones de puertos paralelo y de puertos serie soportan solamente una cantidad limitada de datos que pueden transferirse de una vez. La solución basada en puertos serie es lenta y requiere mucho software. La solución de puertos paralelo se vuelve lenta siempre que grandes cantidades de datos necesiten someterse a comparación cruzada.

Otra solución está destinada a sistemas triplicados que utilizan una instalación de hardware complicada o una conexión de señal de alta velocidad que requiere mucho software y utiliza cableado externo. Cuando se implementaron utilizando hardware externo basado en bastidores, la instalación era complicada y requería mucho software. Cuando se implementaron con una comunicación serie de alta velocidad (Ethernet), la disposición requería mucho software y estaba limitada en velocidad por el cableado externo.

Como ejemplo de un sistema de la técnica relacionada, la patente norteamericana No. 6,182,196 describe un método y un aparato para arbitrar peticiones de acceso a una memoria. La memoria comprende un módulo de verificación cruzada (502) que compara las peticiones de operación de los clientes. Cuando el módulo de verificación cruzada (502) determina que las peticiones están intentando contemporáneamente acceder a un bloque idéntico de la memoria, la comparación cruzada (502) arbitra entre las peticiones de operación de los clientes. El arbitraje se basa en una regla de arbitraje y produce una primera petición de acceso a memoria y una segunda petición de acceso a memoria.

Como otro ejemplo más de un sistema anterior, la publicación de la solicitud de patente US 2002/0010902 describe agrupaciones de puertas programables en el campo (FPGAs) que comprenden un bloque RAM embebido (EBR). En una realización, los EBRs son bloques RAM multipuerto embebidos en un núcleo FPGA. El EBR se utiliza para aumentar la cantidad de memoria y complementar la memoria distribuida de la unidad funcional programable. Se proporciona arbitraje entre puertos de escritura, y una unidad de arbitraje recibe señales de petición de memoria y selecciona una ganadora de entre las peticiones.

El documento DE 198 09 089 A1 describe un método de comparación cruzada de datos entre una pluralidad de canales de procesamiento, en donde se utilizan una pluralidad de placas de acoplamiento que están conectadas una con otra a través de un sistema de bus separado para implementar un mecanismo de replicación.

Sumario de la invención

La presente invención se refiere a un ordenador multiprocesador según la reivindicación 1 y a un método según la reivindicación 9.

Las reivindicaciones adjuntas deberán consultarse para averiguar el alcance verdadero de la invención.

La presente invención es una solución de comparación cruzada que se desarrolla en una configuración multiprocesador. Un aspecto de la presente invención consiste en proporcionar un medio de comparación cruzada rápida y sencilla de datos utilizando una RAM multipuerto con una lógica incorporada. La RAM multipuerto puede enchufarse en la placa posterior de la unidad multiprocesadora que se conecta a cualquier bus estándar o incluso no estándar. Por tanto, no se requieren hardware ni cableado externos.

El sistema de comparación cruzada según la presente invención emplea un método de almacenamiento transitorio de datos que opera a una rápida velocidad limitada solamente por el tiempo de acceso a la memoria. El sistema es simple de implementar y no requiere un protocolo de comunicación.

En un ejemplo de realización el sistema se ajusta sobre una sola placa y no requiere hilos conductores externos. El concepto no está ligado a ningún hardware específico y es válido en términos de arquitectura e implementación de hardware para cualquier tamaño de datos de comparación cruzada y cualquier velocidad de comunicación requerida. Por tanto, si cambian los requisitos de tamaño y/o velocidad, el sistema dado a título de ejemplo puede mejorarse fácilmente sustituyendo la unidad.

La solución de comparación cruzada basada en memoria según la presente invención se basa en una RAM multipuerto con su lógica requerida, implementada, por ejemplo, utilizando una agrupación de puertas programables en el campo (FPGA) o un circuito integrado para aplicaciones específicas (ASIC).

La RAM multipuerto según la presente invención ofrece acceso de escritura y lectura controlado para cada unidad procesadora del sistema, proporcionando un medio de comparación cruzada rápida y sencilla de datos. Se proporciona plena separación entre todas las unidades procesadoras del sistema. Dado que no es posible un acceso simultáneo a ningún lugar de la memoria, no es necesario un arbitraje. El sistema de la invención es idealmente adecuado para, entre otras cosas, sistemas de seguridad, sistemas críticos para una misión o sistemas de alta disponibilidad que están todos ellos sometidos a una verificación cruzada y que se basan en ordenador.

Según una realización de la presente invención, se proporciona un sistema de comparación cruzada para un ordenador multiprocesador que tiene al menos un primero y un segundo procesador. El sistema incluye una primera capa de búferes que comprende una primera área de almacenaje para almacenar información proveniente del primer procesador y una segunda área de almacenaje para almacenar información proveniente del segundo procesador. Se proporciona también una segunda capa de búferes. La segunda capa de búferes comprende una tercera área de almacenaje para almacenar la información proveniente de la primera área de almacenaje y la información proveniente de la segunda área de...

Reivindicaciones:

1. Un ordenador multiprocesador (10) que tiene al menos un primero y un segundo procesador (20, 21, 22) y un sistema de comparación cruzada, comprendiendo dicho sistema de comparación cruzada: una primera capa de búferes (40, 41, 42) que comprende una primera área de almacenaje para almacenar información proveniente del primer procesador (20) y una segunda área de almacenaje para almacenar información proveniente del segundo procesador (21); una segunda capa de búferes (50, 51, 52) que comprende una tercera área de almacenaje para almacenar la información proveniente de dicha primera área de almacenaje y la información proveniente de dicha segunda área de almacenaje, y una cuarta área de almacenaje para almacenar la información proveniente de dicha primera área de almacenaje y la información proveniente de dicha segunda área de almacenaje, en donde cada una de dichas áreas de almacenaje primera, segunda, tercera y cuarta se implementa dentro de una RAM multipuerto (30) y comprende al menos un búfer asignado solamente a su área de almacenaje dentro de dicha RAM multipuerto (30), comprendiendo además dicho sistema de comparación cruzada una lógica interna (60, 61, 62) dispuesta dentro de dicha RAM multipuerto (30), estando configurada dicha lógica interna (60, 61, 62) para transferir de forma síncrona la información de dicha primera área de almacenaje y dicha segunda área de almacenaje a dicha tercera área de almacenaje y a dicha cuarta área de almacenaje, en el que dicho primer procesador (20) está configurado para leer la información de dicha tercera área de almacenaje y para comparar datos almacenados en la tercera área de almacenaje provenientes de la primera área de almacenaje con datos almacenados en la tercera área de almacenaje provenientes de la segunda área de almacenaje a fin de determinar si la información almacenada en dicha tercera área de almacenaje proveniente de la primera área de almacenaje es idéntica a la información almacenada en la tercera área de almacenaje proveniente de la segunda área de almacenaje; y en el que dicho segundo procesador (21) está configurado para leer la información de dicha cuarta área de almacenaje y para comparar datos almacenados en la cuarta área de almacenaje provenientes de la primera área de almacenaje con datos almacenados en la cuarta área de almacenaje provenientes de la segunda área de almacenaje a fin de determinar si la información almacenada en dicha cuarta área de almacenaje proveniente de la primera área de almacenaje es idéntica a la información almacenada en la cuarta área de almacenaje proveniente de la segunda área de almacenaje.

2. El ordenador multiprocesador según la reivindicación 1, en el que la primera capa de búferes (40, 41, 42) son búferes de solo escritura y en el que la segunda capa de búferes (50, 51, 52) son búferes de sólo lectura.

3. El ordenador multiprocesador según la reivindicación 2, en el que el primero y el segundo procesadores (20, 21) escriben datos de forma asíncrona en los búferes (40, 41, 42) de la primera capa y en el que los datos de los búferes (40, 41, 42) de la primera capa son transferidos de forma síncrona a los búferes (50, 51, 52) de la segunda capa.

4. El ordenador multiprocesador según la reivindicación 1, caracterizado porque dicha lógica interna (60, 61, 62) comprende FPGAs y/o ASICs.

5. El ordenador multiprocesador según la reivindicación 1, caracterizado porque dicha lógica interna (60, 61, 62) comprende un FPGA y/o ASIC individual propio para cada uno de dichos procesadores (20, 21, 22).

6. El ordenador multiprocesador según la reivindicación 5, caracterizado porque cada FPGA y/o ASIC individual (60, 61, 62) es alimentado por una fuente de alimentación individual (70, 71, 72).

7. El ordenador multiprocesador (10) según la reivindicación 1, en el que dicho ordenador multiprocesador (10) está configurado para aislar dicho primer procesador (20) cuando no casan los datos que se están comparando en dicho primer procesador (20), y en el que dicho ordenador multiprocesador (10) está configurado para aislar dicho segundo procesador (21) cuando no casan los datos que se están comparado en dicho segundo procesador (21).

8. El ordenador multiprocesador (10) según la reivindicación 1, en el que cada una de dichas áreas de almacenaje tercera y cuarta comprende un primer registro para los datos provenientes de la segunda área de almacenaje y un segundo registro para los datos provenientes de la segunda área de almacenaje, y cada uno de dichos procesadores primero y segundo (20, 21) está configurado para comparar datos del primer registro con datos del segundo registro y para declarar una comparación cruzada satisfactoria cuando los datos en el primer registro son idénticos a los datos en el segundo registro, estando ambos registros primero y segundo en un área de almacenaje asignada exclusivamente a un procesador de comparación.

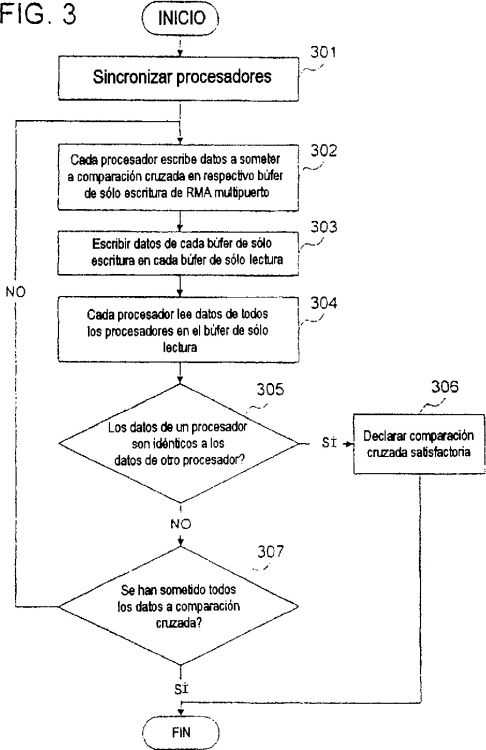

9. Un método de realizar una comparación cruzada para un ordenador multiprocesador (10) que tiene al menos tres procesadores (20, 21, 22), en donde cada uno de dichos al menos tres procesadores (20, 21, 22) utiliza un lugar de memoria separado de una RAM multipuerto (30) y en donde cada uno de dichos al menos tres procesadores (20, 21, 22) está provisto de un puerto individual de dicha RAM multipuerto (30) y cada uno de los puertos individuales está provisto de un respectivo búfer de una pluralidad de búferes (40, 41, 42) de una primera capa, comprendiendo el método los pasos ordenados de: (a) hacer que cada procesador (20, 21, 22) escriba información a someter a comparación cruzada en el búfer de dicha pluralidad de búferes (40, 41, 42) de la primera capa correspondiente al puerto del respectivo procesador; (b) transferir de forma síncrona información escrita en todos los búferes de la pluralidad de búferes (40, 41, 42) de la primera capa a una pluralidad de búferes (50, 51, 52) de una segunda capa por medio de una lógica interna (60, 61, 62) dispuesta dentro de dicha RAM multipuerto (30), proporcionando cada búfer de la pluralidad de búferes (50, 51, 52) de la segunda capa un área de almacenaje para cada búfer de la primera pluralidad de búferes, y estando previsto un búfer respectivo de la pluralidad de búferes (50, 51, 52) de la segunda capa para cada uno de la pluralidad de procesadores (20, 21, 22), en donde la pluralidad de búferes (40, 41, 42) de la primera capa y la pluralidad de búferes (50, 51, 52) de la segunda capa se implementan dentro de dicha RAM multipuerto (30); (c) hacer que cada procesador (20, 21, 22) lea la información de un búfer respectivo de la pluralidad de búferes (50, 51, 52) de la segunda capa; y (d) hacer que cada procesador (20, 21, 22) compare la información leída en su búfer de la pluralidad de búferes (50, 51, 52) de la segunda capa y declare una comparación cruzada satisfactoria si la información de otro procesador casa con información del procesador de comparación, en donde dichos al menos tres procesadores (20, 21, 22) se sincronizan antes de ejecutar la transferencia de información en el paso ordenado (b).

10. Un método de realizar una comparación cruzada según la reivindicación 9, que comprende además un paso ordenado de: (e) determinar si hay información adicional a someter a comparación cruzada, y si es así, repetir los pasos con la información adicional, empezando en el paso (a).

11. Un método de realizar una comparación cruzada según la reivindicación 9, que comprende, además, detectar una sincronización satisfactoria por cada uno de dicha pluralidad de procesadores (20, 21, 22) a través de un escrutinio de su búfer correspondiente de la pluralidad de segundos búferes (50, 51, 52), y en el que cuando, después de un período de tiempo predeterminado, no se detecta por un procesador de la pluralidad de procesadores (20, 21, 22) la sincronización satisfactoria entre todos los procesadores de dicha pluralidad de procesadores (20, 21, 22), ejecutar una operación de retardo de tiempo y realizar la comparación de la información por el procesador.

Patentes similares o relacionadas:

Transmisión de datos entre unidades computacionales mediante tecnología de señales seguras, del 27 de Mayo de 2020, de Siemens Mobility GmbH: Módulo de entrada y salida para enviar y recibir datos a través de una línea de datos , caracterizado por las siguientes características:

- una máquina […]

Transmisión de datos entre unidades computacionales mediante tecnología de señales seguras, del 27 de Mayo de 2020, de Siemens Mobility GmbH: Módulo de entrada y salida para enviar y recibir datos a través de una línea de datos , caracterizado por las siguientes características:

- una máquina […]

Procedimiento de parada de emergencia y sistema de seguridad asociado, del 20 de Mayo de 2020, de CLEARSY: Procedimiento de parada de emergencia de un elemento de seguridad de un conjunto de seguridad , comprendiendo el conjunto de seguridad […]

Actualización de software de componentes no críticos en sistemas distribuidos críticos para la seguridad dual, del 13 de Mayo de 2020, de Siemens Mobility GmbH: Procedimiento para el funcionamiento de un sistema crítico para la seguridad con al menos un primer dispositivo de datos con un software aprobado y relevante […]

Sistemas críticos de seguridad ferroviaria con redundancia de tareas y capacidad de comunicaciones asimétricas, del 22 de Enero de 2020, de Siemens Mobility, Inc: Sistema de control para un sistema de aplicación crítico de seguridad ferroviaria, que comprende: al menos un controlador, que comprende un procesador […]

Circuito integrado digital protegido contra errores transitorios, del 9 de Octubre de 2019, de THALES: Circuito integrado digital que comprende un conjunto lógico que comprende un bloque lógico funcional, una unidad lógica de detección […]

Circuito de generación de reloj y procedimiento de generación de la señal de reloj, del 12 de Junio de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un circuito de generación de reloj , que comprende una primera fuente de reloj , una segunda fuente de reloj y un circuito de puerta lógica , […]

Sistema informático de seguridad de tipo relevante, del 7 de Mayo de 2019, de Siemens Mobility GmbH: Sistema informático de seguridad de tipo relevante, particularmente un sistema de seguridad ferroviario, con al menos dos canales hardware (A; B), en donde los […]

Método, ordenador y aparato para migrar datos de memoria, del 6 de Marzo de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un ordenador, que comprende: un procesador ; un sistema básico de entrada/salida ; una memoria principal , configurada para cargar […]