MUESTREADOR-BLOQUEADOR.

Muestreador-bloqueador que comprende un transistor de muestreo (Q ech) y una capacidad de muestreo (C ech),

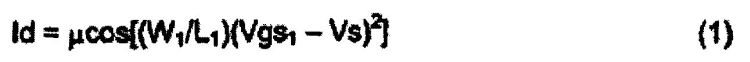

el transistor de muestreo está bloqueado en modo de bloqueo para impedir la descarga de la capacidad de muestreo y conductor en modo de muestreo para aplicar a la capacidad una tensión casi igual a la tensión en su base, caracterizado porque, con vistas a aplicar en dicha base en modo bloqueado una tensión de bloqueo igual a la tensión (Vech) presente en la capacidad de muestreo, está provisto un circuito que comprende en serie, entre dos bornes de alimentación, dos transistores de tipo MOS (MP1, MP2) que tienen dos canales drenado-fuente que tienen casi la misma relación ancho por largo, un transistor bipolar (Qcl) que tiene su base unida al punto de unión de los dos transistores MOS y su emisor unido a la base del transistor de muestreo (Qech), y un diodo (D1) polarizado por una corriente (Ip), conectado entre la fuente y la celda de uno de los dos transistores MOS (MP1), la celda del otro transistor MOS (MP2) está unida a la capacidad de muestreo.

Tipo: Resumen de patente/invención.

Solicitante: ATMEL GRENOBLE S.A.

Nacionalidad solicitante: Francia.

Dirección: AVENUE DE ROCHEPLEINE,38120 SAINT EGREVE.

Inventor/es: GAILLARD,CHRISTOPHE, LE TUAL,STEPHANE.

Fecha de Publicación: .

Fecha Solicitud PCT: 4 de Agosto de 2000.

Fecha Concesión Europea: 16 de Abril de 2008.

Clasificación PCT:

- G11C27/02 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 27/00 Memorias analógicas eléctricas, p. ej. para almacenar valores instantáneos. › Medios de muestreo y de memorización (G11C 27/04 tiene prioridad).

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Patentes similares o relacionadas:

Método y sistema para la adquisición de datos digitales con reducción de potencia, del 24 de Febrero de 2016, de METRO DE MADRID, S.A.: Método y sistema para la adquisición de datos digitales con reducción de potencia. La presente invención se refiere a un método y un […]

Método y aparato para la comprensión y transmisión de datos de alta velocidad, del 25 de Diciembre de 2013, de INTERDIGITAL TECHNOLOGY CORPORATION: Unidad de comunicaci6n inalambrica que oamprende: medios para generar datos para la transmision a una segunda unidad de comunicación; medios para codificar los […]

INTERRUPTOR ANALOGICO GAAS-FET, del 16 de Noviembre de 1996, de FRAUNHOFER-GESELLSCHAFT ZUR FORDERUNG DER ANGEWANDTEN FORSCHUNG E.V.: UN INTERRUPTOR ANALOGICO FET TIENE UN NUDO DE ENTRADA (S), UN NUDO DE SALIDA (D) Y UN ELEMENTO DE TERMINACION (CL), EL CUAL ESTA CONECTADO EN EL NUDO DE SALIDA (D). […]

CIRCUITO INTEGRADO PARA UN SISTEMA ANALOGO., del 16 de Noviembre de 1996, de PILKINGTON MICRO-ELECTRONICS LIMITED: ESTA INVENCION SE REFIERE A CIRCUITOS INTEGRADOS DE SEMICONDUCTORES QUE ENCUENTRAN UTILIDAD EN SISTEMAS ANALOGOS. UN CIRCUITO INTEGRADO […]

UN CIRCUITO PARA AMPLIFICAR, ALMACENAR Y CODIFICAR SEÑALES ELECTRICAS., del 1 de Agosto de 1976, de STANDARD ELECTRIC, S. A.: AMPLIFICADOR CONMUTADO PARA CIRCUITOS DE CODIFICACION POR IMPULSOS. ESTA CONSTITUIDO POR UN AMPLIFICADOR DIFERENCIAL (AMP1) REALIZADO CON […]