DISPOSITIVO PARA COMPARAR DOS VOCABLOS DE N BITS CADA UNO.

Dispositivo de comparación de dos palabras N y P de n bits cada una,

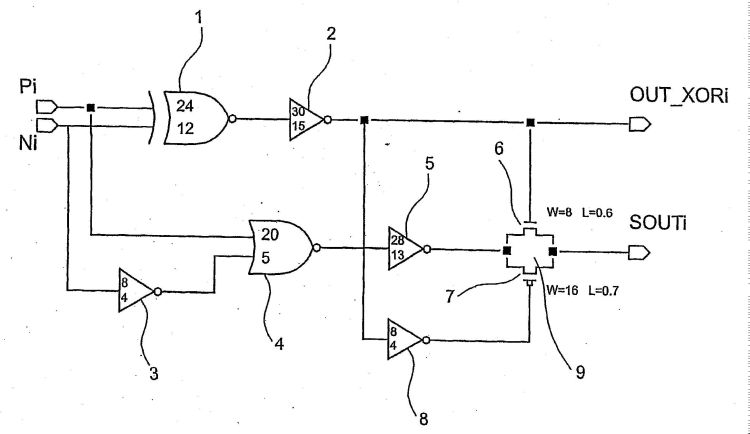

caracterizado porque comprende, por lo menos, un bloque comparador de nivel 1 que comprende, a su vez: - n bloques comparadores básicos que permiten, cada uno, comparar los bits Ni y Pi de orden i de las palabras N y P, con i comprendido entre 0 y n-1, y comprendiendo, cada uno: * un primer sub-bloque que permite generar sobre su salida, formando una primera salida (OUT_XORi) del bloque comparador básico, una primera señal que indica si los bits Ni y Pi son iguales o no; * un segundo sub-bloque que permite generar sobre su salida, una segunda señal que indica cuál de los bits Ni y Pi es el mayor; * un tercer sub-bloque que permite dejar pasar la segunda señal por una segunda salida (SOUTi) del bloque comparador básico, si la primera señal no indica una igualdad de los bits Ni y Pi, y bloquear la segunda señal en caso contrario; - medios de generación de una tercera señal sobre una primera salida (OUT_XOR4_b) del bloque comparador de nivel 1, que indica que los números N y P son iguales si las n primeras señales indican que los n bits Ni y los n bits Pi son iguales, e indican que los números N y P no son iguales, en caso contrario; - primeros medios de paso selectivo que permiten conectar selectivamente a una segunda salida (OUT_COMP4) del bloque comparador de nivel 1, la segunda salida (SOUTi) de un bloque comparador básico que, entre los bloques comparadores básicos que tienen una segunda señal sobre su segunda salida, procesa los bits de orden superior; indicando la señal presente sobre la segunda salida del bloque comparador de nivel 1 cuál de los números N y P es el mayor.

Tipo: Resumen de patente/invención.

Solicitante: ATMEL NANTES SA.

Nacionalidad solicitante: Francia.

Dirección: LA CHANTRERIE, BP 70602,44306 NANTES CEDEX 3.

Inventor/es: COLOMA,BERNARD.

Fecha de Publicación: .

Fecha Concesión Europea: 13 de Diciembre de 2006.

Clasificación PCT:

- G06F7/02 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 7/00 Métodos o disposiciones para el procesamiento de datos actuando sobre el orden o el contenido de los datos tratados (circuitos lógicos H03K 19/00). › Comparación de valores digitales (G06F 7/06, G06F 7/38 tienen prioridad).

- H03K19/21 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 19/00 Circuitos lógicos, es decir, teniendo al menos dos entradas que actúan sobre una salida (circuitos para sistemas de computadores que utilizan la lógica difusa G06N 7/02 ); Circuitos de inversión. › Circuitos O EXCLUSIVO, es decir, que dan una señal de salida si existe una sola señal de entrada; Circuitos de COINCIDENCIA, es decir, dan una señal de salida si todas las señales de entrada son idénticas.

Patentes similares o relacionadas:

SISTEMA DE MEJORA DE MODO DE CONDUCCIÓN CRUCERO CON INCLUSIÓN DE RUTAS CON TRAYECTOS CURVOS BASADO EN AJUSTES DE VELOCIDAD AUTOMÁTICOS, del 27 de Junio de 2019, de KITAZAWA MOLINA, Elvia Isabel: La presente invención describe un sistema de integración en vehiculos y un método de operación de los mismos que permite cambios de comportamiento en éste para posibilitar […]

Reconocedor reconfigurable de patrones de bits basado en jerarquía de memoria, del 6 de Mayo de 2016, de UNIVERSIDAD DE SEVILLA: Reconocedor reconfigurable de patrones de bits basado en jerarquía de memoria que comprende una pluralidad de circuitos digitales organizados en dos […]

AGENTE ANTI-VIRUS DESTINADO PARA SER UTILIZADO CON BASES DE DATOS Y SERVIDORES DE CORREO ELECTRONICO., del 16 de Febrero de 2004, de CHEYENNE SOFTWARE INTERNATIONAL SALES CORP.: Un método basado en servidor para detectar y eliminar virus informáticos situados en anexos a mensajes de correo electrónico en una red de ordenadores que tiene […]

COMPARACION DEL VALOR HAMMING PARA AGRUPACIONES DE VITS NO PONDERADAS., del 1 de Diciembre de 2003, de BRITISH AEROSPACE PUBLIC LIMITED COMPANY: Un comparador de valor de Hamming para proporcionar una salida indicativa de la relación de valor de Hamming de una primera matriz sin peso monodimensional o de mayor […]

JERARQUIAS DE UMBRALES MULTIPLES DE N ELEMENTOS BINARIOS., del 1 de Abril de 2003, de BRITISH AEROSPACE PUBLIC LIMITED COMPANY: Comparador binario no ponderado, para comparar el valor de Hamming de N entradas no ponderadas con un valor de umbral T y para indicar si dicho valor de […]

APARATO DE COMPRESION DE DATOS., del , de INTERNATIONAL BUSINESS MACHINES CORPORATION: SE PRESENTA UN METODO Y UN APARATO PARA EJECUTAR UN ALGORITMO DE COMPRESION DE DATOS SECUENCIAL QUE ES ESPECIALMENTE ADECUADO PARA SU USO CUANDO SE REQUIERA […]

UN COMPARADOR DE UMBRAL DIGITAL MULTIBIT., del 1 de Enero de 1996, de RCA THOMSON LICENSING CORPORATION: SE DESCRIBE UN COMPARADOR DE UMBRAL DIGITAL MULTIBIT QUE CONSTA DE UNA FUENTE (X) DE UNA SEÑAL DE ENTRADA DIGITAL MULTIBIT QUE REPRESENTA UN VALOR […]

METODO PARA PROCESAR DATOS COMPRIMIDOS., del 16 de Febrero de 1994, de FMC CORPORATION: METODO PARA PROCESAR DATOS COMPRIMIDOS SIN CONVERTIR LOS DATOS A UNA FORMA SIN COMPRIMIR. UN PRIMER CONJUNTO DE DATOS DIGITALES SE CONVIERTE […]