METODO DE UTILIZACION PERMANENTE DE UN MATERIAL SEGUN UN EJE Z.

LA PRESENTE INVENCION ESTA RELACIONADA CON UN SISTEMA Y UN METODO PARA REALIZAR EL EXAMEN DE FIABILIDAD DE LOS DISCOS DE SEMICONDUCTORES,

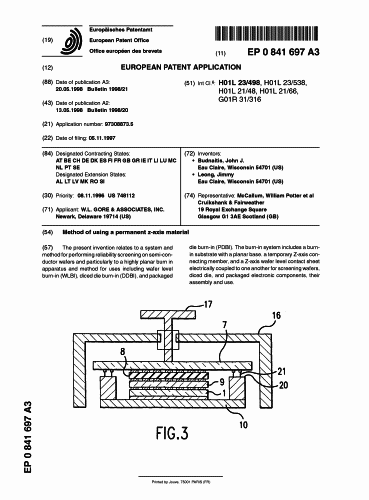

Y PARTICULARMENTE, UN APARATO DE FRITADO MUY PLANO Y UN METODO PARA USARLO EN EL FRITADO NIVELADO DE DISCOS (WLBI), EL FRITADO DE MATRICES CUADRICULADAS (DDBI) Y EL FRITADO DE MATRICES EMPAQUETADAS (PDBI). EL SISTEMA DE FRITADO SE COMPONE DE UN SUSTRATO DE FRITADO DE BASE PLANA, UN MIEMBRO CONECTOR EN EL EJE Z TEMPORAL Y UNA HOJA DE CONTACTO NIVELADO DE DISCOS EN EL EJE Z CONECTADA ELECTRICAMENTE A OTRA PARA EXAMINAR DISCOS, MATRICES CUADRICULADAS, Y COMPONENTES ELECTRONICOS EMPAQUETADOS, SU MONTAJE Y USO.

Tipo: Resumen de patente/invención.

Solicitante: W.L. GORE & ASSOCIATES, INC..

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 555 PAPER MILL ROAD, P.O. BOX 9329,NEWARK, DELAWARE 19714.

Inventor/es: BUDNAITIS, JOHN J., LEONG, JIMMY.

Fecha de Publicación: .

Fecha Concesión Europea: 22 de Octubre de 2003.

Clasificación Internacional de Patentes:

- G01R1/073 FISICA. › G01 METROLOGIA; ENSAYOS. › G01R MEDIDA DE VARIABLES ELECTRICAS; MEDIDA DE VARIABLES MAGNETICAS (indicación de la sintonización de circuitos resonantes H03J 3/12). › G01R 1/00 Detalles o disposiciones de aparatos de los tipos incluidos en los grupos G01R 5/00 - G01R 13/00 y G01R 31/00 (detalles estructurales particulares a disposiciones electromecánicas para medir el consumo eléctrico G01R 11/02). › Sondas múltiples.

- G01R31/316 G01R […] › G01R 31/00 Dispositivos para ensayo de propiedades eléctricas; Dispositivos para la localización de fallos eléctricos; Disposiciones para el ensayo eléctrico caracterizadas por lo que se está ensayando, no previstos en otro lugar (ensayo o medida de dispositivos semiconductores o de estado sólido, durante la fabricación H01L 21/66; ensayo de los sistemas de transmisión por líneas H04B 3/46). › Ensayos de circuitos analógicos.

- H01L21/48 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 21/00 Procedimientos o aparatos especialmente adaptados para la fabricación o el tratamiento de dispositivos semiconductores o de dispositivos de estado sólido, o bien de sus partes constitutivas. › Fabricación o tratamiento de partes, p. ej. de contenedores, antes del ensamblado de los dispositivos, utilizando procedimientos no cubiertos por un único grupo de H01L 21/06 - H01L 21/326.

- H01L21/66 H01L 21/00 […] › Ensayos o medidas durante la fabricación o tratamiento.

- H01L23/498 H01L […] › H01L 23/00 Detalles de dispositivos semiconductores o de otros dispositivos de estado sólido (H01L 25/00 tiene prioridad). › Conexiones eléctricas sobre sustratos aislantes.

- H01L23/538 H01L 23/00 […] › estando la estructura de interconexión entre una pluralidad de chips semiconductores situada en el interior o encima de sustratos aislantes.

Patentes similares o relacionadas:

Sustrato de pastilla embebida con taladro posterior, del 1 de Julio de 2020, de QUALCOMM INCORPORATED: Un dispositivo, que comprende: un sustrato que tiene un primer lado y un segundo lado opuesto, en el que el sustrato es un sustrato central que […]

Procedimiento de fabricación de puentes dieléctricos de identificación sin contacto, del 13 de Mayo de 2020, de Foucault, Jean Pierre: Procedimiento de fabricación de puentes dieléctricos de identificación sin contacto de un paso estandarizado y de una tolerancia ampliada, o de etiquetas […]

Dispositivo de interconexión eléctrica de al menos un componente electrónico con una alimentación eléctrica que comprende medios para reducir una inductancia de circuito cerrado entre un primer y un segundo terminal, del 11 de Marzo de 2020, de ALSTOM Transport Technologies: Dispositivo para la interconexión eléctrica de al menos un componente electrónico con una fuente de alimentación eléctrica, del tipo que comprende, durante […]

Condensador de sustrato de encapsulado incrustado, del 19 de Febrero de 2020, de QUALCOMM INCORPORATED: Un sustrato de encapsulado , que comprende: un sustrato que comprende un primer lado; un condensador incrustado en […]

Estructura de protección para el aislamiento de señal y procedimiento para su fabricación, del 1 de Mayo de 2019, de Thales Solutions Asia Pte Ltd: Un procedimiento de fabricación de una estructura de protección eléctrica para proporcionar el aislamiento de señal que comprende las etapas de: proporcionar […]

Procedimiento de conexión de un chip a una antena de un dispositivo de identificación por radiofrecuencia del tipo de tarjeta con chip sin contacto, del 5 de Marzo de 2019, de ASK S.A.: Procedimiento de conexión de un chip sobre una antena de un dispositivo de identificación por radiofrecuencia del tipo tarjeta con chip sin contacto que […]

Dispositivo de potencia semiconductor y método para ensamblar un dispositivo de potencia semiconductor, del 14 de Febrero de 2019, de Agile POWER SWITCH 3D - INTEGRATION aPSI3D: Un dispositivo de potencia semiconductor que comprende: - un primer sustrato que comprende un elemento […]

Vías concéntricas en sustrato electrónico, del 9 de Enero de 2019, de QUALCOMM INCORPORATED: Una estructura de vías de múltiples paredes en un sustrato para llevar una señal que tiene múltiples capas conductoras, que comprende: una […]