SOPORTE PARA ALMACENAMIENTO DE DATOS CON INTERFAZ DOBLE.

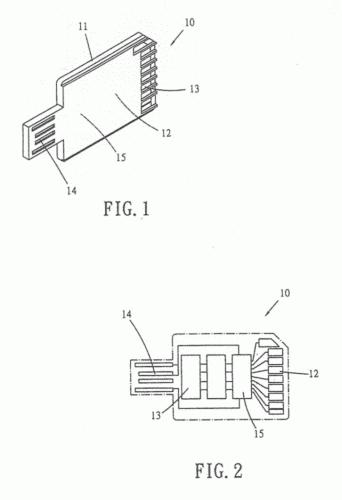

1. Soporte de almacenamiento de datos de interfaz doble que comprende una unidad de memoria y un interfaz principal construido en un cuerpo envolvente,

de manera que un interfaz de conexión y un chip de control que tiene una función de transmisión de interfaz doble están situados adicionalmente en el cuerpo envolvente, estando conectado el chip de control a la unidad de memoria, al interfaz principal y al interfaz de conexión.

2. Soporte de almacenamiento de datos de interfaz doble, según la reivindicación 1, en el que la unidad de memoria está compuesta como mínimo por una memoria flash.

3. Soporte de almacenamiento de datos de interfaz doble, según la reivindicación 1, en el que el chip de control comprende como mínimo un controlador de la tarjeta de memoria, una unidad controladora del flash, un interfaz de función de transmisión de señal diferencial de bajo voltaje, un interfaz lógico/físico de transmisión de señal diferencial de bajo voltaje, y un controlador de señal diferencial de bajo voltaje.

4. Soporte de almacenamiento de datos de interfaz doble, según la reivindicación 1, en el que el interfaz de conexión está situado en el cuerpo envolvente en un extremo opuesto al interfaz principal.

5. Soporte de almacenamiento de datos de interfaz doble, según la reivindicación 1 ó 4, en el que un mecanismo móvil está situado entre el interfaz de conexión y el cuerpo envolvente para posibilitar un cambio correspondiente de posición entre el interfaz de conexión y el cuerpo envolvente.

6. Soporte de almacenamiento de datos de interfaz doble, según la reivindicación 5, en el que el mecanismo móvil consiste en patillas conectadas entre sí que están situadas en el cuerpo envolvente y en el interfaz de conexión respectivamente, con un elemento móvil que pasa entre ellas, y una parte cóncava queda situada en el cuerpo envolvente para retener el interfaz de conexión.

7. Soporte de almacenamiento de datos de interfaz doble, según la reivindicación 5, en el que el mecanismo móvil consiste en ranuras y guías conectadas entre sí que están situadas en un lugar de unión entre el cuerpo envolvente y el interfaz de conexión respectivamente, y una parte cóncava queda situada en el cuerpo envolvente para retener el interfaz de conexión.

8. Soporte de almacenamiento de datos de interfaz doble, según la reivindicación 1, en el que el cuerpo envolvente puede tener la forma de una tarjeta de memoria o bien una microunidad de disco.

9. Soporte de almacenamiento de datos de interfaz doble, según la reivindicación 1, en el que el interfaz principal puede ser un interfaz de transmisión de una tarjeta de memoria o una microunidad de disco.

Tipo: Resumen de patente/invención.

Solicitante: POWER DIGITAL CARD CO. LTD.

CHEN,CHIEN-YUAN.

Nacionalidad solicitante: Taiwan, Provincia de China.

Dirección: 5F-1 N.8 SEC.3 SHUANGSH RD. BANCHIAU CITY,TAPEI 220.

Inventor/es: CHEN,CHIEN YUAN.

Fecha de Solicitud: 6 de Octubre de 2005.

Fecha de Publicación: .

Fecha de Concesión: 20 de Septiembre de 2006.

Clasificación PCT:

- G11C7/10 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 7/00 Disposiciones para escribir una información o para leer una información en una memoria digital (G11C 5/00 tiene prioridad; circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Disposiciones de interfaz para entrada/salida [I/O] de datos, p. ej. circuitos de control de entrada/salida [I/O] de datos, memorias intermedias de entrada/salida [I/O] de datos.

Patentes similares o relacionadas:

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Método de procesado de datos, aparato de almacenamiento, disco de estado sólido y sistema de almacenamiento, del 28 de Agosto de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de procesado de datos, aplicado a un sistema de almacenamiento, en donde el sistema de almacenamiento comprende un anfitrión, un controlador y un […]

Potencia programable para una interfaz de memoria, del 21 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para el control de retardo en una interfaz de memoria, que comprende: proporcionar una polarización de voltaje a un circuito […]

Circuitos de líneas de bits globales de Memoria Estática de Acceso Aleatorio (SRAM) para reducir los fallos de energía durante los accesos de lectura de memoria, y procedimientos y sistemas relacionados, del 17 de Abril de 2019, de QUALCOMM INCORPORATED: Un circuito de línea de bits global de memoria estática de acceso aleatorio, SRAM, para una pluralidad de células de bits de SRAM, que […]

Dispositivo de memoria híbrida con una única interfaz, del 23 de Enero de 2019, de Microsoft Technology Licensing, LLC: Un procedimiento que comprende: recibir, en un controlador , órdenes, direcciones y datos en un dispositivo de memoria mediante una interfaz definida asociada […]

Dispositivo y procedimiento para el procesamiento de cuadros de datos en serie, del 11 de Octubre de 2018, de DR. JOHANNES HEIDENHAIN GMBH: Dispositivo para el procesamiento de cuadros de datos en serie, que comprende una unidad de convertidor en serie-paralelo , una unidad de evaluación […]

Arquitectura central en serie de memoria no volátil, del 3 de Septiembre de 2014, de Conversant Intellectual Property Management Inc: Sistema de memoria que comprende: banco de memoria para suministrar datos de lectura de flujo de bits en serie en respuesta a una operación […]

Arquitectura de DRAM de alta velocidad con una latencia de acceso uniforme, del 16 de Julio de 2014, de Conversant Intellectual Property Management Inc: Memoria Dinámica de Acceso Aleatorio (DRAM) que comprende:

una celda de memoria acoplada a un par de líneas de bit y a una línea de palabra;

un dispositivo […]

Arquitectura de DRAM de alta velocidad con una latencia de acceso uniforme, del 16 de Julio de 2014, de Conversant Intellectual Property Management Inc: Memoria Dinámica de Acceso Aleatorio (DRAM) que comprende:

una celda de memoria acoplada a un par de líneas de bit y a una línea de palabra;

un dispositivo […]