Control de voltaje de línea de palabras en STT-MRAM.

Una memoria de acceso aleatorio magneto-resistente, de fuerza de torsión de transferencia de giro,

en adelante denominada STT-MRAM, que comprende:

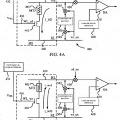

una célula (401) de bits con un empalme de túnel magnético (MTJ) (405) y un transistor (410) de línea de palabras, en en la que la célula (401) de bits está acoplada con una línea (420) de bits y una línea (440) de origen; y

un controlador (432) de línea de palabras acoplado con una compuerta del transistor (410) de línea de palabras, en en la que el controlador (432) de línea de palabras está configurado para proporcionar un voltaje de línea de palabras (VWL) mayor que un voltaje de suministro por debajo de un voltaje de transición (Vtrans) del voltaje de suministro (Vdd), caracterizada porque el controlador (432) de línea de palabras está adicionalmente configurado para proporcionar un voltaje menor que el voltaje de suministro (Vdd) para voltajes de suministro por encima del voltaje de transición (Vtrans),

y en la cual

el voltaje de línea de palabras (VWL) está fijado en, o por debajo de, un voltaje límite (WL_lim) después de alcanzar el voltaje de transición (Vtrans); y

el voltaje (VWL) de la línea de palabras es reducido después de alcanzar el voltaje de transición (Vtrans).

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2009/063245.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: Attn: International IP Administration 5775 Morehouse Drive San Diego, CA 92121 ESTADOS UNIDOS DE AMERICA.

Inventor/es: SANI,Mehdi,Hamidi, KANG,Seung H, YOON,Sei Seung.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G11C11/16 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 11/00 Memorias digitales caracterizadas por la utilización de elementos de almacenamiento eléctricos o magnéticos particulares; Elementos de almacenamiento correspondientes (G11C 14/00 - G11C 21/00 tienen prioridad). › que utilizan elementos en los que el efecto de almacenamiento está basado en el efecto de spin magnético.

PDF original: ES-2532396_T3.pdf

Fragmento de la descripción:

Control de voltaje de línea de palabras en STT-MRAM Campo de la Divulgación

Las realizaciones de la invención se refieren a la memoria de acceso aleatorio. Más específicamente, las realizaciones de la Invención se refieren al control de voltaje de línea de palabras en la Memoria de Acceso Aleatorio Magneto- resistente de Fuerza de Torsión de Transferencia de Giro (STT-MRAM).

Antecedentes

La memoria de acceso aleatorio (RAM) es un componente ubicuo de las modernas arquitecturas digitales. La RAM puede estar en dispositivos autónomos o puede estar integrada o empotrada dentro de dispositivos que usan la RAM, tales como micro-procesadores, micro-controladores, circuitos integrados específicos de la aplicación (ASIC), sistemas- en-un-chip (SoC) y otros dispositivos similares, como apreciarán los expertos en la técnica. La RAM puede ser volátil o no volátil. La RAM volátil pierde su información almacenada toda vez que se quita la energía. La RAM no volátil puede mantener sus contenidos de memoria incluso cuando se quita la energía de la memoria. Aunque la RAM no volátil tiene ventajas en la capacidad de mantener sus contenidos sin tener que aplicar energía, la RAM no volátil convencional tiene tiempos más lentos de lectura / escritura que la RAM volátil.

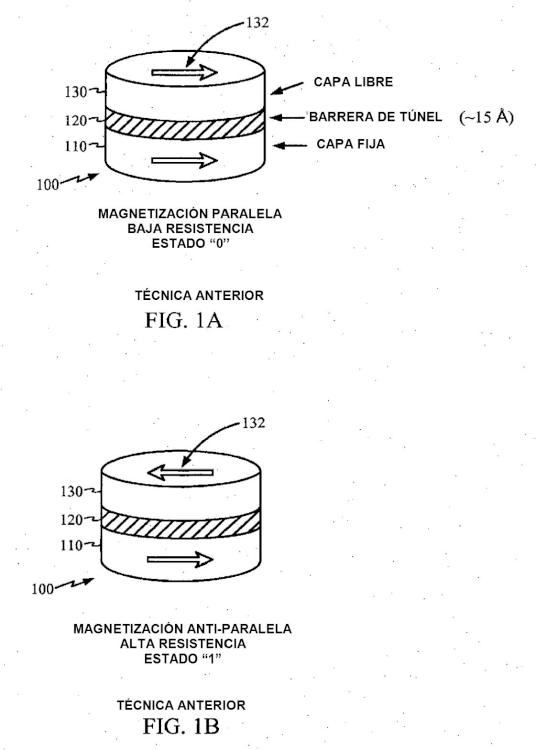

La Memoria de Acceso Aleatoria Magneto-resistente (MRAM) es una tecnología de memoria no volátil que tiene tiempos de respuesta (lectura / escritura) comparables a la memoria volátil. A diferencia de las tecnologías convencionales de RAM que almacenan datos como cargas eléctricas o flujos de corriente, la MRAM usa elementos magnéticos. Según se ilustra en las Figs. 1A y 1B, un elemento 1 de almacenamiento de empalme de túnel magnético (MTJ) puede ser formado a partir de dos capas magnéticas 11 y 13, cada una de las cuales puede mantener un campo magnético, separadas por una capa 12 aislante (barrera de túnel). Una de las dos capas (p. ej., la capa fija 11) se fija en una polaridad específica. La polaridad 132 de la otra capa (p. ej., la capa libre 13) tiene libertad de cambiar, para coincidir con la de un campo externo que pueda ser aplicado. Un cambio en la polaridad 132 de la capa libre 13 cambiará la resistencia del elemento 1 de almacenamiento de MTJ. Por ejemplo, cuando las polaridades están alineadas, Fig. 1A, existe un estado de baja resistencia. Cuando las polaridades no están alineadas, Fig. 1B, entonces existe un estado de alta resistencia. La ilustración del MTJ 1 ha sido simplificada y los expertos en la técnica apreciarán que cada capa ¡lustrada puede comprender una o más capas de materiales, como se conoce en la técnica.

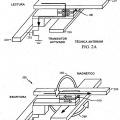

Con referencia a la Fig. 2A, se ilustra una célula 2 de memoria de una MRAM convencional para una operación de lectura. La célula 2 incluye un transistor 21, una línea 22 de bits, una línea 23 de dígitos y una línea 24 de palabras. La célula 2 puede ser leída midiendo la resistencia eléctrica del MTJ 1. Por ejemplo, un MTJ 1 específico puede ser seleccionado activando un transistor asociado 21, que puede conmutar la corriente desde una línea 22 de bits, a través del MTJ 1. Debido al efecto magneto-resistente del túnel, la resistencia eléctrica del MTJ 1 cambia en base a la orientación de las polaridades en las dos capas magnéticas (p. ej., 11, 13), según lo expuesto anteriormente. La resistencia dentro de cualquier MTJ 1 específico puede ser determinada a partir de la corriente resultante de la polaridad de la capa libre. Convencionalmente, si la capa fija 11 y la capa libre 13 tienen la misma polaridad, la resistencia es baja y se lee un "". Si la capa fija 11 y la capa libre 13 tienen polaridades opuestas, la resistencia es mayor y se lee un "1".

Con referencia a la Fig. 2B, se ilustra la célula 2 de memoria de una MRAM convencional para una operación de escritura. La operación de escritura de la MRAM es una operación magnética. En consecuencia, el transistor 21 está apagado durante la operación de escritura. La corriente es propagada a través de la línea 22 de bits y la línea 23 de dígitos, para establecer los campos magnéticos 25 y 26 que pueden afectar la polaridad de la capa libre del MTJ 1 y, por consiguiente, el estado lógico de la célula 2. En consecuencia, los datos pueden ser escritos y almacenados en el MTJ 1.

La MRAM tiene varias características deseables que hacen de ella una candidata para una memoria universal, tales como la alta velocidad, la alta densidad (es decir, el pequeño tamaño de células de bits), el bajo consumo de energía y ninguna degradación a lo largo del tiempo. Sin embargo, la MRAM tiene cuestiones de ajustabilidad a escala. Específicamente, según las células de bits se toman más pequeñas, aumentan los campos magnéticos usados para conmutar el estado de la memoria. En consecuencia, la densidad de corriente y el consumo de energía aumentan para proporcionar los mayores campos magnéticos, limitando así la ajustabilidad a escala de la MRAM.

A diferencia de la MRAM convencional, la Memoria de Acceso Aleatorio Magneto-resistente de Fuerza de Torsión de Transferencia de Giro (STT-MRAM) usa electrones que devienen polarizados en su giro, según los electrones atraviesan una película delgada (filtro de giro). La STT-MRAM también es conocida como RAM de Fuerza de Torsión de Transferencia de Giro (STT-RAM), RAM Conmutadora de Magnetización de Transferencia de Fuerza de Torsión de Giro (RAM de Giro) y Transferencia de Momento de Giro (SMT-RAM). Durante la operación de escritura, los electrones polarizados en giro ejercen una fuerza de torsión sobre la capa libre, lo que puede conmutar la polaridad de la capa libre. La operación de lectura es similar a la MRAM convencional en cuanto a que se usa una corriente para detectar la resistencia, o el estado lógico, del elemento de almacenamiento de MTJ, según lo expuesto en lo precedente. Según se

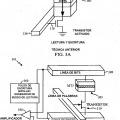

ilustra en la Flg. 3A, una célula 3 de bits de STT-MRAM incluye el MTJ 3, el transistor 31, la línea 32 de bits y la línea 33 de palabras. El transistor 31 se enciende para ambas operaciones de lectura y escritura, para permitir que la corriente fluya a través del MTJ 35, para que el estado lógico pueda ser leído o escrito.

Con referencia a la Fig. 3B, se ilustra un diagrama más detallado de una célula 31 de STT-MRAM, para una exposición 5 adicional de las operaciones de lectura / escritura. Además de los elementos previamente expuestos, tales como el MTJ 35, el transistor 31, la línea 32 de bits y la línea 33 de palabras, se ilustran una línea 34 de origen, un amplificador detector 35, los circuitos 36 de lectura / escritura y la referencia 37 de línea de bits. Como se ha expuesto anteriormente, la operación de escritura en una STT-MRAM es eléctrica. Los circuitos 36 de lectura / escritura generan un voltaje de escritura entre la línea 32 de bits y la línea 34 de origen. Según la polaridad del voltaje entre la línea 32 1 de bits y la línea 34 de origen, la polaridad de la capa libre del MTJ 35 puede ser cambiada y, de manera correspondiente, el estado lógico puede ser escrito en la célula 31. Análogamente, durante una operación de lectura, se genera una corriente de lectura, que fluye entre la línea 32 de bits y la línea 34 de origen a través del MTJ 35. Cuando se permite que la corriente fluya mediante el transistor 31, la resistencia (estado lógico) del MTJ 35 puede ser determinada en base al diferencial de voltaje entre la línea 32 de bits y la línea 34 de origen, que es comparado con 15 una referencia 37 y luego amplificado por el amplificador detector 35. Los expertos en la técnica apreciarán que el funcionamiento y la construcción de la célula 31 de memoria son conocidos en la técnica. Se proporcionan detalles adicionales, por ejemplo, en el documento, de M. Hosomi, et al., Una Novedosa Memoria No Volátil con Conmutación de Magnetización Magneto-resistente de Fuerza de Torsión de Transferencia de Giro: RAM de Giro, anales de la conferencia de IEDM (25).

La operación de escritura eléctrica de la STT-MRAM elimina el problema de ajustabilidad a escala debido a la operación de escritura magnética en la MRAM. Además, el diseño de circuitos es menos complicado para la STT-MRAM. Sin embargo, las fluctuaciones en el voltaje Vdd operativo pueden hacer que la corriente de lectura de la célula se aproxime a, o sea mayor que, el umbral actual de escritura, y provoque de tal modo una operación inválida de escritura y / o daño potencial a los componentes del sistema. Por el contrario, las fluctuaciones en el Vdd pueden degradar el voltaje 25 operativo hasta un nivel indeseablemente bajo que puede reducir las prestaciones del sistema e impedir, potencialmente, que el sistema funcione debidamente, o en absoluto.

El documento WO 28 / 19768 divulga el control... [Seguir leyendo]

Reivindicaciones:

1. Una memoria de acceso aleatorio magneto-resistente, de fuerza de torsión de transferencia de giro, en adelante denominada STT-MRAM, que comprende:

una célula (41) de bits con un empalme de túnel magnético (MTJ) (45) y un transistor (41) de línea de palabras, 5 en en la que la célula (41) de bits está acoplada con una línea (42) de bits y una línea (44) de origen; y

un controlador (432) de línea de palabras acoplado con una compuerta del transistor (41) de línea de palabras, en en la que el controlador (432) de línea de palabras está configurado para proporcionar un voltaje de línea de palabras (Vwl) mayor que un voltaje de suministro por debajo de un voltaje de transición (Vtrans) del voltaje de suministro (Vdd), caracterizada porque el controlador (432) de línea de palabras está adicionalmente configurado para 1 proporcionar un voltaje menor que el voltaje de suministro (Vdd) para voltajes de suministro por encima del voltaje de

transición (Vtrans), y en la cual

el voltaje de línea de palabras (Vwl) está fijado en, o por debajo de, un voltaje límite (WLJim) después de alcanzar el voltaje de transición (Vtrans); y

el voltaje (Vwl) de la línea de palabras es reducido después de alcanzar el voltaje de transición (Vtrans).

2. La STT-MRAM de la reivindicación 1, en la cual el controlador (432) de línea de palabras está configurado para crear una pendiente negativa del voltaje de línea de palabras (Vwl) con respecto al voltaje de suministro (Vdd) después del voltaje de transición (Vtrans).

3. La STT-MRAM de la reivindicación 1, en la cual el voltaje de transición (Vtrans) representa una transición entre una región de bajo Vdd y una región de alto Vdd.

4. La STT-MRAM de la reivindicación 1, que comprende adlclonalmente:

un controlador (5) de escritura configurado para proporcionar una señal eléctrica a la célula (41) de bits, para 25 almacenar un estado lógico en la célula (41) de bits; y

al menos un elemento (52, 54) de alslaclón de escritura, acoplado en serie con el controlador (5) de escritura entre la línea (42) de bits y la línea (44) de origen, en en la que el elemento (52, 54) de aislación de escritura está configurado para aislar el controlador (5) de escritura durante una operación de lectura.

5. La STT-MRAM de la reivindicación 4, en la cual el controlador (5) de escritura comprende:

Inversores primero (52) y segundo (53), acoplados en serie entre una entrada de datos y la línea (42) de bits; y un tercer inversor (51) acoplado en serie entre la entrada de datos y la línea (44) de origen.

6. La STT-MRAM de la reivindicación 1, que comprende adicionalmente:

un elemento (45) de aislación de lectura, interpuesto entre la célula (41) de bits y un amplificador detector (47), en en la que el elemento (45) de aislación está configurado para aislar selectivamente el amplificador detector (47) de la línea (42) de bits durante una operación de escritura.

7. La STT-MRAM de la reivindicación 6, en la cual el elemento (45) de aislación de lectura es al menos uno entre un 4 conmutador, una compuerta de transmisión o un multiplexor.

8. La STT-MRAM de la reivindicación 1, que comprende adicionalmente:

un circuito (74) de bombeo de voltaje, configurado para generar el voltaje (VWl) de línea de palabras a partir del voltaje de suministro (Vdd).

9. La STT-MRAM de la reivindicación 8, que comprende adicionalmente:

un detector (72) de nivel, configurado para controlar el circuito de bombeo de voltaje, para generar el voltaje de línea

de palabras (Vwl) a partir del voltaje de suministro (Vdd).

1. Un procedimiento para operaciones de lectura y escritura en una memoria de acceso aleatorio magneto-resistente, de fuerza de torsión de transferencia de giro, que comprende:

aplicar un primer voltaje a una compuerta de un transistor (41) de línea de palabras de una célula (41) de bits 5 durante una operación de escritura, en en la que el primer voltaje es superior a un voltaje de suministro (Vdd) si el

voltaje de suministro es inferior a un voltaje de transición (Vtrans); estando el procedimiento caracterizado por:

aplicar un segundo voltaje al transistor (41) de línea de palabras durante una operación de escritura, en en la 55 que el segundo voltaje es inferior al voltaje de suministro (Vdd) si el voltaje de suministro es superior a un voltaje

de transición (Vtrans);

fijar el voltaje de línea de palabras (VWL) en, o por debajo de, un voltaje límite (WLJim) más allá del voltaje de transición (Vtrans), para proporcionar el segundo voltaje; y

reducir el segundo voltaje después de alcanzar el voltaje de transición (Vtrans), para proporcionar el segundo voltaje.

11. El procedimiento de la reivindicación 1, que comprende reducir el segundo voltaje después de alcanzar el voltaje de transición, para proporcionar el segundo voltaje.

12. El procedimiento de la reivindicación 11, en el cual el voltaje de transición (Vtrans) representa una transición entre 1 una región de bajo Vdd y una región de alto Vdd.

13. El procedimiento de la reivindicación 11, que comprende adicionalmente:

bombear el voltaje de suministro para generar el primer voltaje, usando un circuito (74) de bombeo de carga.

Patentes similares o relacionadas:

Sistema de memoria de múltiples flujos de instrucciones, del 6 de Mayo de 2020, de QUALCOMM INCORPORATED: Un dispositivo de memoria que comprende: un decodificador ; una pluralidad de células de memoria , en el que cada una de las células […]

Procedimiento para determinar el estado de espín de compuestos de transición de espín, uso del procedimiento para leer datos digitales y medio de memoria óptica o magnetoóptica, del 10 de Julio de 2019, de TECHNISCHE UNIVERSITAT WIEN: Procedimiento para determinar el estado de espín de un compuesto de transición de espín por medio de radiación con luz en un dominio de longitudes de onda definido para […]

Generación de un estado no reversible en una célula de bits que tiene una primera unión de túnel magnética y una segunda unión de túnel magnética, del 2 de Julio de 2019, de QUALCOMM INCORPORATED: Un procedimiento que comprende: aplicar una tensión de programa a una primera unión de túnel magnética MTJ de una célula de bits sin aplicar la tensión […]

Uso de etiquetas RFID hechas resistentes a la radiación gamma en dispositivos farmacéuticos, del 28 de Febrero de 2019, de EMD Millipore Corporation: Procedimiento, que comprende: fijar etiquetas a componentes farmacéuticos, comprendiendo dichas etiquetas un dispositivo de memoria grabable, no basado […]

Métodos y sistemas para gestión de datos de memoria no volátil, del 9 de Enero de 2019, de Winbond Electronics Corp: Un sistema, que comprende: una primera matriz de memoria no volátil resistiva ; una segunda matriz de memoria no volátil basada en transistores […]

Utilización de etiquetas RFID endurecidas a los rayos gamma en dispositivos farmacéuticos, del 18 de Mayo de 2016, de EMD Millipore Corporation: Un sistema de gestión de activos farmacéuticos, que comprende componentes farmacéuticos, cada uno tiene una etiqueta fijada al mismo, caracterizado porque dicha […]

Procedimiento y dispositivo para manipular y seleccionar espines, del 7 de Octubre de 2015, de DORADO GONZALEZ,MANUEL: La presente invención consiste en construir un dispositivo tipo Hall al que se incorpora, como novedad, un tercer elemento: Este tercer elemento es una fuente que produce […]

Procedimiento y dispositivo para manipular y seleccionar espines, del 7 de Octubre de 2015, de DORADO GONZALEZ,MANUEL: La presente invención consiste en construir un dispositivo tipo Hall al que se incorpora, como novedad, un tercer elemento: Este tercer elemento es una fuente que produce […]

Estructura de unión túnel magnética, del 1 de Abril de 2015, de QUALCOMM INCORPORATED: Una célula MTJ que comprende: una zanja en un sustrato ; una estructura MTJ dentro de la zanja, teniendo la zanja dimensiones que determinan la forma […]