Tradcucción de dirección dinámica con gestión de trama.

Un método para llevar a cabo una función de gestión de trama en un procesador (101) capaz de traducir una dirección virtual a una dirección traducida de un bloque de datos en almacenamiento principal en un sistema informático (100) de una arquitectura de máquina que tiene una jerarquía de tablas (410,

412, 414, 416) de traducción utilizadas para la traducción de dicha dirección virtual, estando definida dicha función de gestión de trama para dicha arquitectura de máquina, estando el método caracterizado por que comprende:

obtener una instrucción de máquina que contiene un código de operación para una instrucción de activar clave de almacenamiento y borrar; y ejecutar la instrucción de máquina, comprendiendo:

obtener un campo de gestión de trama con un campo de clave que comprende una serie de bits de protección de acceso y un campo de indicador del tamaño de bloque;

obtener una dirección de operando de una trama de almacenamiento sobre la que ha de llevarse a cabo dicha instrucción de máquina, siendo dicha dirección de operando una entre una dirección de bloque grande de datos y una dirección de un bloque pequeño de datos;

en respuesta a la habilitación de una función de activar clave de almacenamiento, poner los bits de protección de acceso de almacenamiento de cada clave de almacenamiento asociada con dicho bloque datos determinado, a un valor de dichos bits de protección de acceso de dicho campo de clave; y en respuesta a la habilitación de una función de borrar, borrar cada bloque datos al que se dirige dicha dirección de operando poniendo a cero todos los bytes de cada bloque de datos.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2009/050051.

Solicitante: INTERNATIONAL BUSINESS MACHINES CORPORATION.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: NEW ORCHARD ROAD ARMONK, NY 10504 ESTADOS UNIDOS DE AMERICA.

Inventor/es: HELLER,LISA, SLEGEL,TIMOTHY, SITTMANN III,GUSTAV, GREINER,Dan, GAINEY JR.,Charles, OSISEK,Damian.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F12/10 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 12/00 Acceso, direccionamiento o asignación en sistemas o arquitecturas de memoria (entrada digital a partir de, o salida digital hacia soportes de registro, p. ej. hacia unidades de almacenamiento de disco G06F 3/06). › Traducción de direcciones.

- G06F12/14 G06F 12/00 […] › Protección contra la utilización no autorizada de la memoria.

- G06F9/30 G06F […] › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Disposiciones para ejecutar instrucciones de máquinas, p. ej. decodificación de instrucciones (para ejecutar microinstrucciones G06F 9/22).

PDF original: ES-2381428_T3.pdf

Fragmento de la descripción:

Traducción de dirección dinámica con gestión de trama.

CAMPO DE LA INVENCIÓN

La presente invención se refiere en general a sistemas y métodos para traducir una dirección virtual en un sistema informático y, más en particular, a sistemas y métodos que llevan a cabo una función de gestión de trama en un sistema informático con capacidad para traducir direcciones virtuales.

ANTECEDENTES DE LA INVENCIÓN

La traducción dinámica de direcciones proporciona la capacidad de interrumpir la ejecución de un programa en un momento arbitrario, grabar éste y sus datos en almacenamiento auxiliar, tal como un dispositivo de almacenamiento de acceso directo, y en un momento posterior devolver el programa y los datos a posiciones diferentes del almacenamiento principal para reanudar la ejecución. La transferencia del programa y sus datos entre el almacenamiento principal y el auxiliar puede llevarse a cabo de manera fragmentaria, y la devolución de la información al almacenamiento principal puede producirse en respuesta a un intento por parte de la CPU de acceder a la misma en el momento en que se requiere para la ejecución. Estas funciones pueden llevarse a cabo sin modificación o inspección del programa y sus datos, no requieren ninguna convención de programación explícita en el programa trasladado, y no perturban la ejecución del programa excepto por el retardo temporal implicado.

Con el soporte adecuado por parte del sistema operativo, la capacidad de traducción dinámica de direcciones puede utilizarse para proporcionar a un usuario un sistema en el que el almacenamiento parece mayor que el almacenamiento principal que está disponible en la configuración. Este almacenamiento principal aparente se denomina a menudo almacenamiento virtual, y las direcciones utilizadas para designar posiciones en el almacenamiento virtual se denominan a menudo direcciones virtuales. El almacenamiento virtual de un usuario puede exceder considerablemente el tamaño del almacenamiento principal que está disponible en la configuración y normalmente se mantiene en almacenamiento auxiliar. Se considera que el almacenamiento virtual se compone de bloques de datos, denominados normalmente páginas (también llamados segmentos y regiones) . Solamente las páginas del almacenamiento virtual a las que se ha hecho referencia más recientemente son asignadas para ocupar bloques de almacenamiento principal físico. Cuando el usuario hace referencia a páginas de almacenamiento virtual que no aparecen en el almacenamiento principal, éstas son incorporadas al almacenamiento principal sustituyendo páginas que es menos probable que se necesiten. En algunos casos, el almacenamiento virtual se asigna al almacenamiento principal durante un largo período de tiempo (o permanentemente) , independientemente de si se hace o no referencia al almacenamiento. El intercambio de páginas de almacenamiento puede ser realizado por el sistema operativo sin conocimiento del usuario.

Los programas utilizan direcciones (o direcciones virtuales) para acceder al almacenamiento virtual. El programa puede recuperar instrucciones desde el almacenamiento virtual o cargar datos o almacenar datos desde el almacenamiento virtual utilizando direcciones virtuales. Las direcciones virtuales asociadas con un rango del almacenamiento virtual definen un espacio virtual. Con el soporte apropiado por parte de un sistema operativo, la capacidad de traducción dinámica de direcciones puede ser utilizada para proporcionar una serie de espacios de direcciones. Estos espacios de direcciones pueden ser utilizados para proporcionar grados de aislamiento entre usuarios. Dicho soporte puede consistir en un espacio de direcciones completamente diferente para cada usuario, proporcionando de ese modo un aislamiento completo, o puede proporcionarse un área compartida mapeando una parte de cada espacio de direcciones a una sola área de almacenamiento común. Asimismo, se prevén instrucciones que permiten a un programa semi-privilegiado acceder a más de uno de dichos espacios de direcciones.

La traducción dinámica de direcciones proporciona la traducción de direcciones virtuales desde múltiples espacios de direcciones diferentes. Estos espacios de direcciones se denominan espacio primario de direcciones, espacio secundario de direcciones y espacios de direcciones especificados por registro de acceso. Asimismo, un programa privilegiado puede provocar el acceso al espacio de direcciones locales. La traducción dinámica de direcciones puede especificarse para direcciones de datos e instrucciones generadas por la CPU.

Lo que se necesita es una capacidad de traducción dinámica de direcciones mejorada que proporcione funcionalidad, capacidad y protecciones adicionales, desconocidas hasta ahora en esta técnica.

CARACTERÍSTICAS DE LA INVENCIÓN

La invención da a conocer un método acorde con la reivindicación 1, y un sistema y un programa informático correspondientes.

Lo que se da a conocer es una función de activar clave y una función de gestión de trama para borrado definidas para una arquitectura de máquina de un sistema informático que tiene una jerarquía de tablas de traducción utilizadas para la traducción de la dirección virtual en una dirección real o absoluta de un bloque de datos en una memoria o almacenamiento principal. Las direcciones reales pueden ser sometidas a anteposición de prefijo para formar direcciones absolutas.

En un ejemplo de realización, se obtiene una instrucción de máquina que contiene un código de operación para una instrucción de gestión de trama que tiene un primer campo que identifica un primer registro general y un segundo campo que identifica un segundo registro general. Obtenido por el primer registro general existe un campo de gestión de trama con un campo de clave que tiene una serie de bits de protección de acceso y un campo indicador del tamaño de bloque. A partir del segundo registro general se obtiene una dirección de operando de una trama de almacenamiento sobre la que ha de llevarse a cabo la instrucción de máquina. La dirección de operando es una dirección absoluta a un bloque grande de datos o una dirección real a un bloque pequeño de datos. Si la función activar clave de almacenamiento está habilitada, los bits de protección de acceso de almacenamiento de cada clave de almacenamiento asociada con el bloque de datos determinado se ponen al valor de los bits de protección de acceso del campo de clave. Si la función de borrado está habilitada, se borra cada bloque de datos al que se dirige la dirección de operando poniendo a cero todos los bytes de cada bloque de datos.

En otra realización, la clave de almacenamiento tiene bits de protección de almacenamiento, bits de referencia de almacenamiento y bits de modificación de almacenamiento. El campo de clave tiene un bit de protección contra lectura, un bit de referencia y un bit de modificación. El bloque grande de datos es mayor que el bloque pequeño de datos. Para el bloque pequeño de datos, se obtiene del segundo registro general una dirección de operando del bloque pequeño de datos que tiene una clave de almacenamiento con una serie de bits de protección de acceso de almacenamiento. Los bits de protección de acceso del campo de clave se ponen en los bits de protección de acceso de almacenamiento de la clave de almacenamiento.

A continuación se describirá la invención en relación con ciertas realizaciones ilustradas. Debe entenderse que los expertos en la materia pueden realizar diversos cambios y modificaciones sin apartarse del alcance de la invención.

BREVE DESCRIPCIÓN DE LOS DIBUJOS

Las figuras anexas, en las que los mismos números de referencia se refieren a elementos idénticos o funcionalmente similares a través de todas las diferentes vistas y que junto con la siguiente descripción detallada se incorporan a la especificación y forman parte de la misma, sirven para ilustrar diversas realizaciones y para explicar varios principios y ventajas, siempre de acuerdo con la presente invención. Las anteriores y otras características y ventajas de la materia objeto dada a conocer en la presente memoria resultarán evidentes a partir de la siguiente descripción detallada, tomada junto con los dibujos anexos, en los cuales:

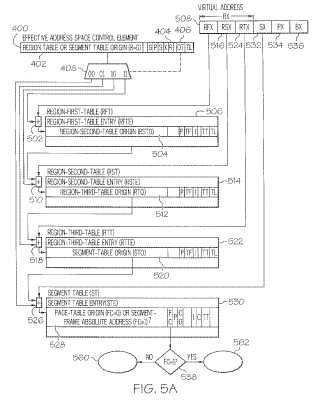

la figura 1 muestra una realización de un sistema de ordenador central en el que se llevará a cabo traducción dinámica de direcciones;

la figura 2 da a conocer un ejemplo de sistema de ordenador central emulado, que emula el sistema de ordenador central de una arquitectura de central;

... [Seguir leyendo]

Reivindicaciones:

1. Un método para llevar a cabo una función de gestión de trama en un procesador (101) capaz de traducir una dirección virtual a una dirección traducida de un bloque de datos en almacenamiento principal en un sistema informático (100) de una arquitectura de máquina que tiene una jerarquía de tablas (410, 412, 414, 416) de traducción utilizadas para la traducción de dicha dirección virtual, estando definida dicha función de gestión de trama para dicha arquitectura de máquina, estando el método caracterizado por que comprende:

obtener una instrucción de máquina que contiene un código de operación para una instrucción de activar clave de almacenamiento y borrar; y ejecutar la instrucción de máquina, comprendiendo:

obtener un campo de gestión de trama con un campo de clave que comprende una serie de bits de protección de acceso y un campo de indicador del tamaño de bloque;

obtener una dirección de operando de una trama de almacenamiento sobre la que ha de llevarse a cabo dicha instrucción de máquina, siendo dicha dirección de operando una entre una dirección de bloque grande de datos y una dirección de un bloque pequeño de datos;

en respuesta a la habilitación de una función de activar clave de almacenamiento, poner los bits de protección de acceso de almacenamiento de cada clave de almacenamiento asociada con dicho bloque datos determinado, a un valor de dichos bits de protección de acceso de dicho campo de clave; y en respuesta a la habilitación de una función de borrar, borrar cada bloque datos al que se dirige dicha dirección de operando poniendo a cero todos los bytes de cada bloque de datos.

2. El método acorde con la reivindicación 1, en el que la instrucción de máquina obtenida comprende además un primer campo que identifica un primer registro general y un segundo campo que identifica un segundo registro general; dicho campo de gestión de trama con un campo clave que comprende una serie de bits de protección de acceso y un campo indicador del tamaño del bloque, se obtienen desde dicho primer registro general, y en el que dicha dirección de operando de dicha trama de almacenamiento sobre la que ha de llevarse a cabo dicha instrucción de máquina se obtiene de dicho segundo registro general, en el que dicha dirección de operando es una entre una dirección absoluta de un bloque grande de datos y una dirección real de un bloque pequeño de datos, siendo dicha dirección real sometida a la anteposición de prefijo.

3. El método acorde con la reivindicación 1, en el que dicha clave de almacenamiento comprende además bits de protección de almacenamiento, bits de referencia almacenamiento y bits modificación de almacenamiento, y en el que dicho campo de clave comprende además un bit de protección contra lectura, un bit de referencia y un bit de modificación, y en el que dicho bloque grande de datos es mayor que dicho bloque pequeño de datos, comprendiendo además para dicho bloque pequeño de datos:

obtener de dicho segundo registro general una dirección de operando de dicho bloque pequeño de datos, teniendo dicho bloque pequeño de datos una clave de almacenamiento que comprende una serie de bits de protección de acceso de almacenamiento; y poner dichos bits de protección de acceso de dicho campo de clave en dichos bits de protección de acceso de almacenamiento de la clave de almacenamiento.

4. El método acorde con la reivindicación 3, en el que para dicho bloque grande de datos, se guarda una dirección de un próximo bloque de datos en dicho segundo registro general, siendo dicho próximo bloque de datos un bloque de datos siguiente a dicho bloque grande de datos.

5. El método acorde con la reivindicación 1, en el que el campo de gestión de trama comprende además un indicador de activar clave de almacenamiento y un indicador de borrar almacenamiento, en el que la etapa de determinación comprende además, habilitar la función de clave de almacenamiento si el indicador de activar clave de almacenamiento está habilitado, inhabilitar la función de activar clave de almacenamiento si el indicador de activar clave de almacenamiento no está habilitado, habilitar la función de borrar si el indicador de borrar almacenamiento está habilitado, e inhabilitar la función de borrar si el indicador de borrar almacenamiento no está habilitado.

6. El método acorde con la reivindicación 1, en el que la instrucción de máquina no es nativa de la arquitectura de instrucciones de máquina del procesador, y que comprende además:

interpretar la instrucción de máquina para identificar una rutina de soporte lógico predeterminada para emular la operación de la instrucción de máquina, comprendiendo la rutina de soporte lógico predeterminada una serie de instrucciones; y ejecutar la rutina soporte lógico predeterminada.

7. Un sistema que comprende medios adaptados para llevar a cabo todas las etapas del método acorde con cualquier reivindicación anterior de método.

8. Un programa informático que comprende instrucciones para llevar a cabo todas las etapas del método acorde con cualquier reivindicación anterior de método, cuando dicho programa informático es ejecutado en un sistema informático.

Patentes similares o relacionadas:

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Procedimiento de control sistemático de direcciones de zonas de memoria en el marco de una transferencia por acceso directo, del 1 de Abril de 2020, de THALES: Procedimiento de control sistemático por un dispositivo de control de al menos un mensaje de configuración de transferencia, siendo el mensaje de configuración […]

Servidor de seguridad de soporte lógico, del 19 de Febrero de 2020, de Idemia Identity & Security France: Procedimiento de verificación de ejecución de applets (AA1, AB1) desarrolladas en un lenguaje orientado objeto y compiladas en código intermedio, siendo el procedimiento […]

Múltiples conjuntos de campos de atributos dentro de una única entrada de tabla de páginas, del 25 de Septiembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento que comprende: traducir , por una primera unidad de procesamiento , una dirección de memoria virtual a una […]

Procedimiento para proteger datos relevantes para la seguridad en una memoria caché, del 14 de Agosto de 2019, de SIEMENS AKTIENGESELLSCHAFT: Procedimiento para proteger datos relevantes para la seguridad en una memoria caché, archivándose una copia de los datos relevantes para la seguridad […]

Archivo seguro, del 7 de Agosto de 2019, de Waterfall Security Solutions Ltd: Aparato de almacenamiento, que comprende: una memoria ; un procesador de encriptado , que está configurado para recibir y encriptar datos transmitidos desde uno […]

Sistemas y métodos para proporcionar como salida un resultado de una instrucción de procesador vigente tras su salida de una máquina virtual, del 3 de Abril de 2019, de Bitdefender IPR Management Ltd: Un sistema anfitrión que comprende al menos un procesador hardware configurado para ejecutar una máquina virtual y un programa de seguridad informática, en donde el al menos […]

Sistema y método para la gestión distribuida de ordenadores compartidos, del 20 de Febrero de 2019, de Zhigu Holdings Limited: Método para operar una arquitectura de gestión informática de múltiples niveles, teniendo dicho método los siguientes pasos: operar un ordenador […]