MÉTODO, CÉLULA DE RECURRENCIA Y CIRCUITO PARA REALIZAR DIVISIONES CON OPERANDOS DE COMA FIJA DE ALTA VELOCIDAD.

La presente invención se refiere a un método para aplicar en las células de recurrencia de un circuito divisor para dividir un dividendo de coma fija por un divisor de coma fija.

Además se proporcionan dichas células de recurrencia y un circuito divisor, que divide en una base r = 2k, generando k bits en cada iteración. El divisor divide un dividendo X de n bits por un divisor Y de m bits mayor que cero, devolviendo un cociente Q de n bits y un resto R de m bits. La presente invención hace la división más rápida, preferentemente usando una propagación de acarreo eficaz para la suma y la resta. El circuito divisor puede modificarse fácilmente con el fin de devolver más bits fraccionales en el cociente Q. Se describen dos arquitecturas, denominadas para la célula de recurrencia de dígitos. La primera es para una implementación de hardware general y la segunda está optimizada para la lógica programable. También se proporciona un conjunto de instrucciones para implementar dicho método en un medio programable, y/o configurar dicho u otro medio programable.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P200901646.

Solicitante: UNIVERSIDAD AUTONOMA DE MADRID.

Nacionalidad solicitante: España.

Inventor/es: SUTTER,Gustavo.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F7/49 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 7/00 Métodos o disposiciones para el procesamiento de datos actuando sobre el orden o el contenido de los datos tratados (circuitos lógicos H03K 19/00). › Cálculos con una base diferente de una base 2, 8, 16 ó 10, p. ej. con una base ternaria, negativa o imaginaria, con una base mixta.

- G06F7/535 G06F 7/00 […] › Sólo división.

PDF original: ES-2372132_A1.pdf

Fragmento de la descripción:

Método, célula de recurrencia y circuito para realizar divisiones con operandos de coma fija de alta velocidad.

Campo de la invención

La presente invención se encuentra dentro del campo de las divisiones entre dos números de coma fija. Más en particular, se refiere a un método para aplicar en una célula de recurrencia de un circuito divisor, dicha célula de recurrencia y un circuito divisor que comprende estas células. La invención puede adaptarse para llevar a cabo la división entre un dividendo con signo y un divisor con signo, y además, obtener dígitos fraccionales adicionales en el resultado.

Antecedentes de la invención

La división digital de dos valores binarios ha sido implementada de varias maneras. Puede encontrar descripciones completas en la bibliografía (1) J.P. Deschamps, G.A. Bioul, and G. Sutter, "Synthesis of Arithmetic Circuits: FPGA, ASIC and Embedded Systems", Wiley Intescience. 2006. (2) S.F. Oberman and M.J. Flynn. "Division algorithms and implementations". IEEE Transactions on Computers. 46(8):833-854. August 1997. (3) B. Parhami. Computer Arithmetic: Algorithms and Hardware Design. Oxford University Press. 2000. (4) Milos. D. Ercegovac and Tomas Lang. Digital arithmetic San Francisco. California: Morgan Kaufmann. cop. 2004.

A modo de resumen, cuando los operandos están normalizados pueden aplicarse varios algoritmos de recurrencia como el SRT (Sweeney-Robertson-Tocher) en diferentes bases y representaciones del resto, ó bien con algoritmos de convergencia de dígitos como Newton-Rapshon, Goldschmidt (Expansión de MacLaurin), etc. Si los operandos no están normalizados se aplican normalmente los algoritmos binarios de división con restauración y sin restauración. Aunque pueden utilizarse bases superiores normalmente con el fin de hacer más rápidos estos algoritmos, las implementaciones de la división con lógica programable más comunes (Xilinx y Altera) utilizan algoritmos de división sin restauración en base 2.

Los costes de área C y de tiempo T de los circuitos divisores de base 2 para un dividendo X de n bits y un divisor Y de m bits que retorna un cociente Q de n bits y un resto R de m bits son distintos para la división con restauración y sin restauración, dependiendo de los siguientes parámetros:

Así para la división con restauración el coste de área y el de tiempo quedan:

Mientras que para la división sin restauración, quedan como

Dichos componentes constituyen una unidad capaz de realizar un conjunto de operaciones aritméticas sobre un conjunto de números expresados en una base r=2k que se denomina célula_base_2^k. El resultado del conjunto de operaciones de la célula_base_2^k comprende un cociente de k dígitos y un nuevo resto de m+1 dígitos.

Si se utilizan bases mayores con el fin de acelerar el proceso de división. El área y el tiempo esperados para una base r = 2k son:

C(n,m,k) = (n/k) Ccélula_base2wedge k(m) + Cmux + Csumador (m), y

T(n,m,k) = (n/k)Tcélula_base2wedge k(m) + Tsumador(m).

Los esfuerzos en acelerar el cómputo se basan en utilizar métodos de división y células con el menor retardo posible y con un coste en área menor e implementar mediante ellos un circuito divisor.

Resumen de la invención

El objeto de la invención es proporcionar un método más rápido y con menor costo de área para hallar los restos parciales y los cocientes durante las etapas de una división sin restauración en una célula de base 2k según la reivindicación 1 independiente. Además, en un segundo aspecto se proporciona una célula de base 2k según la reivindicación independiente 4. En un tercer aspecto se proporciona un circuito divisor según una primera arquitectura en la reivindicación 11 independiente, y en un cuarto aspecto inventivo se reivindica un circuito divisor según una segunda arquitectura en la reivindicación 14. Conjuntamente se proporciona en un quinto aspecto un conjunto de instrucciones que pueden ejecutarse en un medio programable que llevan a cabo las variantes de realización definidas por cualquiera de los aspectos inventivos segundo, tercero o cuarto. Además, en un sexto aspecto inventivo se proporciona un producto destinado a ejecutarse en medios programables que c comprende un conjunto de instrucciones según la reivindicación 19.

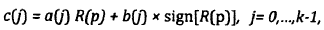

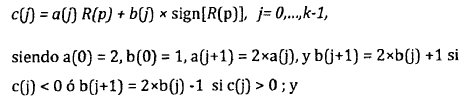

En una división sin restauración en base 2k de un dividendo de n dígitos entre un divisor de m dígitos comprende p=0, .., [n/k] pasos en los que se halla en cada etapa:

En un primer aspecto inventivo se describe un método para aplicar a una célula célula_base_2^k en que calcula en paralelo de todos los posibles restos en base y de las condiciones de selección del resto correcto.

En una primera etapa se le suministran a cada célula:

En una segunda etapa se calculan los valores posibles de la suma y de la resta de los 2k-1 múltiplos impares del divisor con el valor del resto parcial.

En una tercera etapa se determina a su vez, de entre estos posibles valores de los restos, el valor del resto parcial siguiente R(p+1) a partir de los signos de estos valores posibles del resto como c(k-1)

dónde

a(0) = 2;

b(0) = 1;

a(j+1) = 2×a(j)

b(j+1) = 2×b(j) + 1 si c(j) < 0

ó

b(j+1) = 2×b(j) - 1 si c(j) > 0

En una cuarta etapa, los signos de los valores posibles del resto son utilizados para calcular los k dígitos del cociente q(k+p), ..., q(p) asignándose el valor... [Seguir leyendo]

Reivindicaciones:

1. Método para hallar los restos durante una división sin restauración en una célula de base 2k entre un dividendo X de n bits y un divisor Y de m bits que en la etapa p (p=0...[n/k]) de la división sin restauración comprende las siguientes etapas:

2. Método según la reivindicación 1 caracterizado porque la representación de los números es binaria de complemento a dos.

3. Método según la reivindicación 2 caracterizado porque los bits del signo de cada uno de los números del conjunto de restos c(j) se concatenan para obtener los bits del cociente.

4. Célula para hallar k dígitos de un cociente Q y un valor de un resto parcial R(p+1) entre un dividendo X de n bits y un divisor Y de m bits que comprende:

5. Célula según la reivindicación anterior caracterizada porque los medios adaptados para realizar las operaciones lógicas son multiplexores.

6. Célula según la reivindicación anterior caracterizada porque comprende 1+2k-1 multiplexores para implementar la selección del resto parcial en función del bit de los posibles restos parciales y un multiplexor para seleccionar el registro del cociente.

7. Célula según cualquiera de las reivindicaciones 4 a 6 caracterizada porque comprende sumadores condicionales que determina la operación suma o resta entre dos posibles valores de restos correspondientes a c(j), j=1, ..., k-1 en función del bit más significativo del registro del resto parcial c(j-1).

8. Célula según la reivindicación caracterizada porque los dígitos q(k-1-j), j=0, ..., k-1 del registro del cociente q(k-1-j) corresponden a la concatenación de los bits de signo de los restos parciales según el bit más significativo del registro del resto c(j) con una representación binaria de complemento a dos.

9. Célula según la reivindicación 2 caracterizada porque está implementada utilizando una arquitectura en donde los multiplexores seleccionan los registros de los restos c(j), j= 0, ..., k-1.

10. Célula según la reivindicación 2 caracterizada porque está implementada utilizando una arquitectura en donde los sumadores condicionales seleccionan los registros de los restos c(j), j= 0, ..., k-1.

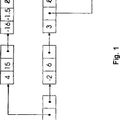

11. Circuito para implementar un método de división sin restauración que comprende una célula de base 2k en la que se introducen los múltiplos impares del divisor, el resto parcial y k bits del dividendo y genera como resultado k bits de cociente y un nuevo resto para la siguiente etapa en donde la arquitectura es secuencial.

12. Circuito según la reivindicación anterior caracterizado porque comprende:

13. Circuito para implementar un implementar un método de división sin restauración que comprende una célula de base 2k en la que se introducen los múltiplos impares del divisor, el resto parcial y k bits del dividendo y genera como resultado k bits de cociente y un nuevo resto para la siguiente etapa en donde la arquitectura es paralela.

14. Circuito según la reivindicación anterior caracterizado porque comprende:

15. Conjunto de instrucciones que, cuando son interpretadas por un medio programable, hacen que este medio realice un método según cualquiera de las reivindicaciones 1 a 3.

16. Conjunto de instrucciones cuya interpretación por un medio programable hacen que un medio de lógica programable configure una célula de recurrencia según cualquiera de las reivindicaciones 4 a 10.

17. Conjunto de instrucciones para implementar un método en un medio programable que, cuando son interpretadas por dicho medio programable, hacen que un medio de lógica programable configure un circuito divisor según cualquiera de las reivindicaciones 11 a 14.

18. Conjunto de instrucciones para implementar un método en un medio programable que, cuando son interpretadas por dicho medio programable, hacen que este medio realice dicho método según cualquiera de las reivindicaciones 1 a 3.

19. Producto que comprende un conjunto de instrucciones registradas en un medio legible y ejecutables en un medio programable, cuya ejecución comprende que dicho medio programable realice cualquiera de las reivindicaciones 15 a 18.

Patentes similares o relacionadas:

Aplicación de un lenguaje cuaternario para ordenador, del 14 de Febrero de 2017, de PORRAS VILA,F. JAVIER: La aplicación de un lenguaje cuaternario para ordenador, es un sistema básico de hardware que cada letra del teclado de un ordenador, multiplicará por cuatro para significar […]

SISTEMA COMPUTACIONAL PARA ALAMCENAR CANTIDADES INFINITAS, INFINITESIMAS Y FINITAS Y EJECUTAR OPERACIONES ARITMETICAS CON ELLAS, del 20 de Noviembre de 2009, de YAROSLAV, SERGEEV: Un sistema computacional adaptado para operar sobre estructuras de datos que representan respectivos operandos infinitos, infinitésimos y/o finitos (X), […]

SISTEMA COMPUTACIONAL PARA ALAMCENAR CANTIDADES INFINITAS, INFINITESIMAS Y FINITAS Y EJECUTAR OPERACIONES ARITMETICAS CON ELLAS, del 20 de Noviembre de 2009, de YAROSLAV, SERGEEV: Un sistema computacional adaptado para operar sobre estructuras de datos que representan respectivos operandos infinitos, infinitésimos y/o finitos (X), […]