DISPOSITIVO DE CARACTERIZACIÓN DE TRANSITORIOS DE CORRIENTE PRODUCIDOS POR INTERACCIÓN DE PARTÍCULAS IONIZANTES CON UN BLOQUE DE TRANSISTORES DE UNA PUERTA LÓGICA.

Dispositivo de caracterización de transitorios de corriente producidos por interacción de partículas ionizantes con un bloque de transistores de una puerta lógica,

que comprende un bloque de memoria con condensadores y un bloque de sincronismo,

- estando el bloque de memoria provisto de medios para replicar dicha corriente y enviarla a una pluralidad de salidas conectadas cada una a una derivación hacia un condensador mediante un interruptor de evaluación,

- siendo el bloque de sincronismo capaz de generar a intervalos regulares unas señales de control de abertura de los interruptores,

de modo que durante un transitorio de corriente la variación de carga de los diferentes condensadores a través de los interruptores de evaluación se inicia a intervalos regulares, siendo posible caracterizar a partir de los estados de carga de los condensadores el perfil temporal aproximado de la integral del transitorio de corriente.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P200930030.

Solicitante: UNIVERSITAT DE LES ILLES BALEARS.

Nacionalidad solicitante: España.

Inventor/es: VERD MARTORELL,JAUME, MERINO PANADES,JOSE LUIS, BOTA FERRAGUT,SEBASTIAN ANTON, ALORDA LADARIA,BARTOMEU, ROSSELLO SANZ,JOSE LUIS, SEGURA FUSTER,JAUME AGAPIT.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G01R31/00 FISICA. › G01 METROLOGIA; ENSAYOS. › G01R MEDIDA DE VARIABLES ELECTRICAS; MEDIDA DE VARIABLES MAGNETICAS (indicación de la sintonización de circuitos resonantes H03J 3/12). › Dispositivos para ensayo de propiedades eléctricas; Dispositivos para la localización de fallos eléctricos; Disposiciones para el ensayo eléctrico caracterizadas por lo que se está ensayando, no previstos en otro lugar (ensayo o medida de dispositivos semiconductores o de estado sólido, durante la fabricación H01L 21/66; ensayo de los sistemas de transmisión por líneas H04B 3/46).

- G01R31/3187 G01R […] › G01R 31/00 Dispositivos para ensayo de propiedades eléctricas; Dispositivos para la localización de fallos eléctricos; Disposiciones para el ensayo eléctrico caracterizadas por lo que se está ensayando, no previstos en otro lugar (ensayo o medida de dispositivos semiconductores o de estado sólido, durante la fabricación H01L 21/66; ensayo de los sistemas de transmisión por líneas H04B 3/46). › Ensayos integrados.

Fragmento de la descripción:

Dispositivo de caracterización de transitorios de corriente producidos por interacción de partículas ionizantes con un bloque de transistores de una puerta lógica.

La presente invención se refiere a un dispositivo para la captura y medida experimental de los efectos transitorios producidos por un SEE en un circuito microelectrónico que puede ser implementado en cualquier tecnología CMOS estándar.

Antecedentes de la invención

Las partículas alfa o los neutrones provenientes de la radiación cósmica son partículas ionizantes que pueden generar procesos de ionización en circuitos integrados.

El efecto producido por una de dichas partículas en un dispositivo electrónico recibe el nombre de SEE (Single Event Effect). La tendencia de la industria microelectrónica consistente en fabricar dispositivos cada vez más pequeños trabajando con voltajes cada vez más bajos está provocando que la carga eléctrica necesaria para producir un error en un nodo determinado del circuito sea cada vez más pequeña.

En consecuencia, los dispositivos microelectrónicos son cada vez más sensibles a la generación de pulsos transitorios producidos por SEEs. Si bien dichos efectos son transitorios, pueden tener consecuencias nefastas en aplicaciones que requieran elevada fiabilidad, como por ejemplo las relacionadas con la aeronáutica, la automoción o las aplicaciones médicas.

Un tipo frecuente de SEE es el conocido como SEU (Single Event Upset). Un SEU es un error que se produce en el circuito causado por la carga eléctrica que se genera por la pérdida de energía que experimenta una partícula ionizante cuando impacta en un cristal semiconductor como el silicio. Si dicha carga es suficientemente grande, puede cambiar el estado lógico de un nodo que contenga la información del estado de un elemento de memoria.

Otro tipo de SEE es el SET (Single Event Transient). Un SET tiene lugar cuando una partícula impacta en un nodo determinado de un circuito lógico combinacional, produciendo una perturbación transitoria del voltaje de dicho nodo. Dicha perturbación puede dar lugar a una falsa transición lógica, que puede propagarse a través de varias etapas de puertas lógicas para ser capturada en última estancia por un elemento de memoria dando lugar a un SEU.

Típicamente un SEE es generado por radiación ionizante presente en la atmósfera procedente de la radiación cósmica tal como neutrones o protones. El flujo de dichas partículas es más elevado en zonas altas de la atmósfera que en el nivel del mar, por ejemplo en la zona destinada a la aviación comercial. Adicionalmente, un SEE puede ser producido por partículas alfa originadas por la desintegración de átomos de uranio o torio, presentes en forma de trazas en el encapsulado de los circuitos integrados.

Los SEEs pueden generarse también en circuitos que trabajen en ambientes con presencia de materiales radioactivos o tras la explosión de armas nucleares.

Hasta el momento se han desarrollado numerosas técnicas encaminadas a mitigar el efecto de los SEEs, tanto en circuitos lógicos como en memorias (consultar por ejemplo las patentes US7319253, US2007/0109865, comentadas más abajo), que tienen como objetivo incrementar el tiempo medio entre fallos que presenta un circuito electrónico cuando opera en su entorno habitual de funcionamiento.

También se conocen trabajos previos encaminados a detectar el instante específico en que se produce un SEU (US7109746, US2007/0162798, EP1758022) o a medir la tasa de errores debida a SEEs en circuitos trabajando en condiciones normales de operación. En dichos trabajos se utilizan memorias SRAM de elevada capacidad y se detecta el número de posiciones de memoria que han cambiado de estado lógico como consecuencia de un SEU. Sin embargo, estas técnicas no permiten determinar las características eléctricas que han causado dicho SEU.

Otro problema diferente es el de determinar las características eléctricas producidas por un SEE en un nudo determinado del circuito, como por ejemplo los transitorios de corriente inducidos en dicho nudo.

Respecto a este último problema, no se conoce ningún dispositivo encaminado a dicha finalidad. Tres son los motivos que dificultan dicha tarea:

Estas circunstancias provocan que en la práctica se recurra a técnicas de simulación por ordenador para obtener información relativa a las características de dichos transitorios (US 2007/0096754).

Se describen a continuación algunos de los antecedentes mencionados así como otros documentos del estado de la técnica relacionados con la presente invención.

En EP 1 906 526 se describe la "utilización de filtros de promedio móvil para detectar transitorios debidos a la radiación y corregir sus efectos", de modo que no es necesario con este procedimiento emplear memorias redundantes para detectar cambios en el circuito. Sin embargo, se trata de un procedimiento de detección que no permite medir ni caracterizar las corrientes originadas por la radiación ionizante.

En US 5 657 267 se describe una RAM dinámica capaz de detectar SEU, en el cual se emplean memorias redundantes para poder comparar entre instantes diferentes. Sin embargo, es un dispositivo basado en la comparación y que tampoco permite caracterizar las corrientes producidas en acontecimientos SEU o SET. Además, también precisa de memorias redundantes.

En US 5 898 711 A1 se describe un procedimiento en el que se distribuyen una pluralidad de detectores de SEU, los cuales funcionan por registros de bits, y para cuya aplicación son necesarios registros blindados redundantes para poder realizar comparaciones, y por lo tanto, presenta las mismas carencias que el anterior.

En US 2007/0096754, ya mencionada y considerado como el antecedente más cercano de la invención, se describe un procedimiento y un sistema para analizar SEU's en dispositivos semiconductores, concretamente en el que se usa un modelo para predecir la respuesta de un dispositivo semiconductor a un SEU. Este procedimiento de análisis incluye simular el impacto de una partícula en un nodo, determinar si provoca cambios en el nodo y finalmente variar la carga de la partícula para obtener un rango de valores de la carga que provocan cambios en el nodo. Sin embargo, tampoco se basa en la medida de corrientes y su eficacia depende de los modelos de simulación, necesariamente simplificadores, empleados.

Finalmente, en el artículo de Maya Gokhale y Paul Graham "Dynamic reconfiguration for management of radiation-induced faults in FPGAs" se describe un sistema de reconfiguración dinámica para la gestión de SEU en FPGA's. Este sistema incluye la posibilidad de inducir fallos artificialmente, que puede tratarse de una exposición a radiación conocida y controlada o bien una simulación por ordenador, pero tampoco permite caracterizar con precisión los acontecimientos SEU y SET y los transitorios de corriente que tienen asociados. También se basa en la comparación entre memorias redundantes.

Ante lo expuesto, el solicitante de la presente invención ha considerado necesario concebir un dispositivo y un procedimiento basado en este capaces de caracterizar con precisión SEU y SET en dispositivos microelectrónicos, en especial mediante la medida de corrientes provocadas por estos transitorios.

Descripción de la invención

Para ello, la presente invención propone un dispositivo de caracterización de transitorios de corriente producidos por interacción de partículas ionizantes...

Reivindicaciones:

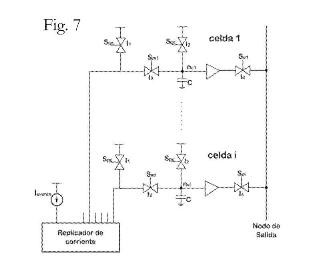

1. Dispositivo de caracterización de transitorios de corriente (I) producidos por interacción de partículas ionizantes con un bloque de transistores de una puerta lógica (1), caracterizado por el hecho de que comprende un bloque de memoria (2) con condensadores (C) y un bloque de sincronismo (3),

- estando el bloque de memoria (2) provisto de medios para replicar dicha corriente (I) y enviarla a una pluralidad de salidas conectadas cada una a una derivación (nc) hacia una condensador (C) mediante un interruptor de evaluación (mi),

- siendo el bloque de sincronismo (3) capaz de generar a intervalos regulares (tmuestreo) unas señales de control de abertura (Smi) de los interruptores de evaluación (mi),

de modo que durante un transitorio de corriente (I) la variación de carga de los diferentes condensadores (C) a través de los interruptores de evaluación se inicia a intervalos regulares (tmuestreo), siendo posible caracterizar a partir de los estados de carga de los condensadores (C) el perfil temporal aproximado de la integral del transitorio de corriente (I).

2. Dispositivo según la reivindicación anterior, en el que cada derivación (nc) está conectada a un nodo de salida (N) común a través de un interruptor de lectura (oi).

3. Dispositivo según cualquiera de las reivindicaciones anteriores, provisto de medios de restablecimiento del potencial de los condensadores a una tensión determinada (Vdd).

4. Dispositivo según la reivindicación anterior, en el que dichos medios comprenden sendos interruptores (PC) conectados en la entrada y salida de cada uno de dichos interruptores de evaluación (mi).

5. Dispositivo según cualquiera de las reivindicaciones 2, 3 ó 4, que comprende un amplificador dispuesto entre cada condensador (C) y el nodo de salida (N).

6. Dispositivo según cualquiera de las reivindicaciones anteriores, el bloque de memoria (2) tiene los condensadores (C), y sus interruptores asociados (mi, pc), organizados en dos bancos idénticos.

7. Dispositivo según cualquiera de las reivindicaciones anteriores, en el que el bloque de sincronismo (3) comprende una cadena de celdas monoestables.

8. Dispositivo según cualquiera de las reivindicaciones anteriores, en el que el bloque de sincronismo (3) comprende dos sub-bloques (A, B) de sincronismo conectados entre sí.

9. Dispositivo según cualquiera de las reivindicaciones anteriores, que comprende un bloque de detección (4) configurado para detectar el inicio de un transitorio de corriente (I).

10. Dispositivo según la reivindicación anterior, en el que dicho bloque de detección (4) comprende un condensador (Cd), un interruptor (m1) que conecta la salida de dicho bloque de transistores de la puerta lógica (1) a una derivación (nc) hacia dicho condensador (Cd) y medios para emitir una señal de detección a partir de un valor umbral de carga de dicho condensador (Cd).

11. Dispositivo según la reivindicación anterior, en el que dichos medios para emitir una señal de detección consisten en un trigger de Schmitt.

12. Dispositivo según cualquier combinación de las reivindicaciones anteriores, que comprende una unidad de control (5) configurada para controlar el bloque generador de sincronismo (3) en función de consignas externas y de las señales emitidas por el bloque de detección (4).

13. Dispositivo según cualquiera de las reivindicaciones anteriores, en el que la puerta lógica (1), el bloque de memoria (2), el bloque de sincronismo (3) y el bloque de detección (4) están integrados en un mismo sustrato.

14. Dispositivo según cualquiera de las reivindicaciones, que comprende un bloque de generación inducida de corrientes (6) capaz de suministrar una corriente a dicho bloque de memoria (2) para su calibración.

15. Dispositivo según la reivindicación anterior, en el que dicho bloque de generación inducida de corrientes 6 comprende un monoestable conectado a la puerta de un transistor.

16. Dispositivo según cualquiera de las reivindicaciones anteriores, que comprende un bloque de atenuación (7) conectado en la entrada del bloque de memoria (2).

17. Dispositivo según la reivindicación anterior, en el que dicho bloque de atenuación (7) es un transistor.

18. Dispositivo según cualquiera de las reivindicaciones anteriores, en el que cada derivación (nc) está conectada a un nodo de salida (N) común a través de un interruptor de lectura (oi).

19. Dispositivo según cualquiera de las reivindicaciones anteriores, en el que dicho bogue de transistores de una puerta lógica (1) está realizado con tecnología CMOS.

20. Procedimiento de caracterización de transitorios de corriente (I) producidos por interacción de partículas ionizantes con una puerta lógica CMOS (1), en el que se emplea un dispositivo según cualquiera de las reivindicaciones anteriores, que comprende las etapas de:

- replicar dicha corriente (I) para enviarla a dichas salidas,

- abrir secuencialmente y a intervalos de tiempo regulares (tmuestreo) los diferentes interruptores de evaluación (mi),

de modo que durante un transitorio de corriente (I) la variación de carga de los diferentes condensadores (C) se inicia a intervalos regulares (tmuestreo), siendo posible caracterizar a partir de los estados de carga de los condensadores (C) el perfil temporal aproximado de la integral del transitorio de corriente (I).

Patentes similares o relacionadas:

Método, aparato y sistema para detectar el estado de funcionamiento de panel fotovoltaico, y sistema eléctrico fotovoltaico, del 15 de Julio de 2020, de GREE ELECTRIC APPLIANCES INC. OF ZHUHAI: Un método para detectar un estado operativo de un panel fotovoltaico, en donde el panel fotovoltaico está dispuesto en un sistema eléctrico fotovoltaico, el […]

Procedimiento para el funcionamiento de una red eléctrica de a bordo, del 29 de Abril de 2020, de ROBERT BOSCH GMBH: Procedimiento para el funcionamiento una red eléctrica de a bordo en un vehículo a motor; en donde la red de a bordo presenta un convertidor de tensión continua […]

Procedimiento para el funcionamiento de una red eléctrica de a bordo, del 29 de Abril de 2020, de ROBERT BOSCH GMBH: Procedimiento para el funcionamiento una red eléctrica de a bordo en un vehículo a motor; en donde la red de a bordo presenta un convertidor de tensión continua […]

Procedimiento y dispositivo para la vigilancia de líneas y conexiones eléctricas en subestaciones de rectificación y en los tramos de línea correspondientes de ferrocarriles eléctricos, del 15 de Abril de 2020, de Elpro GmbH: Procedimiento para la vigilancia de líneas y conexiones eléctricas para verificar la seguridad operacional y personal en subestaciones de rectificación y en […]

Análisis de las oscilaciones y los ruidos de una máquina eléctrica alimentada por un convertidor, del 6 de Noviembre de 2019, de SIEMENS AKTIENGESELLSCHAFT: Procedimiento de determinación para determinar una función (GE, GMP, GMR) de transferencia eléctrica y al menos una mecánica de una máquina eléctrica, la cual se conecta […]

Dispositivo de prueba de alta tensión y alta potencia, del 18 de Septiembre de 2019, de b2 electronics GmbH: Un dispositivo de prueba de alta tensión y alta potencia que comprende - medios para generar una tensión de prueba, en el que la tensión de prueba es un tensión […]

Equipo y procedimiento de prueba de transformador de instrumentos, del 26 de Junio de 2019, de RADIAN RESEARCH, INC: Un procedimiento para probar un transformador , comprendiendo el procedimiento operar un controlador para generar una señal de conmutación, […]

Equipo y procedimiento de prueba de transformador de instrumentos, del 26 de Junio de 2019, de RADIAN RESEARCH, INC: Un procedimiento para probar un transformador , comprendiendo el procedimiento operar un controlador para generar una señal de conmutación, […]

Método y aparato para proteger transformadores de energía de perturbaciones magnéticas grandes, del 21 de Junio de 2019, de Advanced Power Technologies, Inc: Un sistema para la protección de un transformador que tiene: (a) un devanado de entrada, (b) al menos un devanado de salida destinado a ser […]

Procedimiento para supervisar un estado de conmutación de un conmutador de un sistema de seguridad para trenes, así como sistema de seguridad para trenes, del 3 de Junio de 2019, de Thales Management & Services Deutschland GmbH: Procedimiento para supervisar un estado de conmutación de un conmutador (3, 3a, 3b) en un circuito de conmutación (1, 1',1'',1'''), conforme a la técnica de señales, de un […]