Aparato y procedimiento para la adquisición de una secuencia de ensanchamiento en sistemas DSSS aperiódicos.

Un detector DSSS (19) para detectar una sincronización entre una señal de espectro ensanchado(r(nTc)),

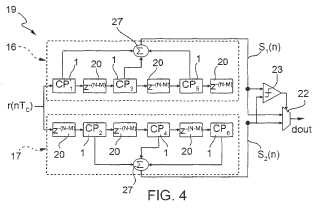

que tiene una pluralidad de chips, r(n), y un valor del factor de ensanchamiento, N, y una secuencia deensanchamiento, PN, que tiene una pluralidad de chips, pi, comprendiendo el detector DSSS (19) al menos unaramificación (16) adaptada para recibir la señal de espectro ensanchado, comprendiendo la al menos unaramificación una pluralidad de correladores (1), incluyendo cada correlador un número, M, de fases de correlación(2) que es inferior a dicho valor del factor de ensanchamiento, N, estando los correladores (1) conectados encascada entre sí y separados entre sí por un bloque de retardo de ramificación (20), estando dicho bloque de retardode ramificación (20) adaptado para retardar la señal de espectro ensanchado recibida por una cantidad de retardo,N-M, que es inferior al valor del factor de ensanchamiento, N, comprendiendo cada correlador (1) medios decorrelación (3, 4, 12) para correlacionar chips de la secuencia de ensanchamiento con chips de la señal de espectroensanchado y generar cada una un valor de correlación propio (y(n)),

comprendiendo adicionalmente el detector DSSS (19) medios de detección de concordancia (27, 22, 23) para recibirdichos valores de correlación y detectar cuando dichos chips de la secuencia de ensanchamiento están alineadoscon dichos chips de la señal de espectro ensanchado.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/IT2008/000138.

Solicitante: SELEX ELSAG S.P.A.

Nacionalidad solicitante: Italia.

Dirección: Via Giacomo Puccini 2 16154 Genova ITALIA.

Inventor/es: TEDESCHI,RAFFAELE.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F17/15 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 17/00 Equipo o métodos de procesamiento de datos o de cálculo digital, especialmente adaptados para funciones específicas (recuperación de la información, estructuras de las bases de datos o estructuras de los sistemas de archivos G06F 16/00). › Cálculo de funciones de correlación.

- H04B1/7075 ELECTRICIDAD. › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04B TRANSMISION. › H04B 1/00 Detalles de los sistemas de transmision, no cubiertos por uno de los grupos H04B 3/00 - H04B 13/00; Detalles de los sistemas de transmisión no caracterizados por el medio utilizado para la transmisión. › con código de adquisición de fase.

- H04B1/708 H04B 1/00 […] › Implementación paralela.

- H04B1/709 H04B 1/00 […] › Estructura de correlación.

PDF original: ES-2390311_T3.pdf

Fragmento de la descripción:

Aparato y procedimiento para la adquisición de una secuencia de ensanchamiento en sistemas DSSS aperiódicos.

5 CAMPO DE LA INVENCION

La presente invención se refiere a un aparato y un procedimiento para la adquisición de una secuencia de ensanchamiento en sistemas DSSS aperiódicos, y más particularmente un aparato y un procedimiento para adquirir una secuencia de pseudo ruido (PN) en sistemas de telecomunicaciones que emplean una modulación aperiódica

de espectro ensanchado por secuencia directa (DSSS) .

ANTECEDENTES DE LA INVENCION

Como se conoce, en un sistema de comunicaciones de espectro ensanchado, un transmisor propaga una señal de

información sobre un amplio ancho de banda y un receptor, tras la recepción de la señal de información, desensancha la señal de información en la banda ancha original.

Una técnica posible para ensanchar la banda ancha de una señal se denomina espectro ensanchado por secuencia directa (DSSS) .

En un sistema que emplea una técnica de DSSS, antes de la transmisión, se multiplica una señal de información de banda estrecha por un código de propagación para ensanchar su energía sobre una banda más ancha, generando de esta manera una señal de información de banda ancha. Después de la recepción, la señal de información de banda ancha se multiplica de nuevo por el mismo código de propagación usado en la transmisión, recuperando de

este modo la señal de información de banda estrecha original.

Los sistemas de comunicaciones DSSS permiten un aumento de la inmunidad de la señal útil frente a señales interferentes de banda estrecha; cuando la señal recibida se multiplica por el código de propagación, la energía de la señal interferente se ensancha en una banda que es más amplia que la banda de señal útil. Después, un filtro de

banda estrecha pasa la señal útil y rechaza la mayor parte de la señal interferente.

Normalmente, se usan secuencias de ruido pseudo-aleatorias (PN) como códigos de propagación. El periodo de un bit de la secuencia (PN) normalmente se denomina tiempo de chip o periodo de chip (Tc) , y el periodo de un bit de la señal de información no ensanchada se denomina habitualmente tiempo de bit o periodo de bit (TB) . Por

consiguiente, los bits de la secuencia PN se denominan chips, así como los bits de la señal de información de banda ancha, que también se denominan chips, para distinguirlos de los bits de la señal de información no ensanchada.

Además, el tiempo de chip (Tc) es inferior al tiempo de bit (TB) y su relación TB/Tc se denomina factor de ensanchamiento N; el valor de N también representa la longitud en chips de un bit de la señal de información no

ensanchada.

Para una mejor comprensión de las formas de onda usadas en los sistemas de comunicaciones DSSS, se hace referencia a las figuras 1a-1c. En detalle, la figura 1a muestra una señal no ensanchada u (nTB) , que es una señal de información que se transmitirá; la figura 1b muestra una secuencia PN p (nTc) , usada para ensanchar la señal no 45 ensanchada formada por una pluralidad de chips pi; y la figura 1c muestra una señal de espectro ensanchado r (nTc) = u (nTB) ·p (nTc) , resultante del ensanchamiento. Como se observa, la secuencia PN p (nTc) tiene un periodo Nc que es independiente de la señal no ensanchada u (nTB) . En este caso particular, el factor de ensanchamiento es N =

20.

50 Existen dos tipologías de sistemas DSSS: sistemas DSSS periódicos, en los que el tiempo de bit es igual a o múltiplo de la extensión de tiempo de la secuencia PN completa, y sistemas DSSS aperiódicos, en los que no existe relación entre el tiempo de bit y la extensión de tiempo de la secuencia PN. Se usan comúnmente sistemas DSSS aperiódicos junto con códigos concatenados.

55 Para que el sistema funcione eficazmente, el receptor debe ser capaz de realizar una adquisición sincronizada, es decir, debe ser capaz de generar una replica local de la secuencia PN usada en la transmisión y después sincronizar la fase de la replica local con la fase de la secuencia PN contenida en la señal recibida.

La adquisición de la sincronización en un sistema DSSS se divide normalmente en dos operaciones, normalmente denominadas operación de adquisición y de seguimiento. Durante la operación de adquisición, la señal de información recibida y la replica local de la secuencia PN se alinean toscamente dentro de un error aceptable predeterminado (por ejemplo, 1/2 de un tiempo de chip) . Durante la operación de seguimiento, se realiza una alineación más fina entre la señal de información recibida y la replica local de la secuencia PN y se mantiene con el

tiempo.

Al considerar la operación de adquisición, existen tres técnicas principales: Búsqueda en serie, búsqueda secuencial y técnica de filtro adaptado. En un sistema que emplea la técnica de filtro adaptado, la señal de información recibida se suministra secuencialmente a un correlador cuyos coeficientes son una replica exacta de la secuencia PN (es

decir, un filtro adaptado) . El filtro adaptado genera una señal de salida que es máxima cuando la secuencia PN contenida en la señal recibida se alinea (en fase) con los coeficientes del correlador. Esta técnica permite detectar la fase de la secuencia PN contenida en la señal de información recibida y después alinear la replica local, con el fin de desensanchar la señal de información recibida y recuperar la señal de información de banda estrecha original.

En particular, la técnica de filtro adaptado ofrece los mejores rendimientos en cuando a velocidad de adquisición en condiciones de una baja relación señal a ruido (SN) y se ve menos afectada por problemas de adquisición perdida y/o falsa. Sin embargo, la característica más limitante de la técnica de filtro adaptado es la gran cantidad de recursos computacionales requeridos para su implementación y el hecho de que no puede usarse en sistemas DSSS aperiódicos.

Hoy en día el interés hacia esta técnica está considerablemente en aumento, en su mayor parte debido a los avances en los recursos computacionales, ya que puede obtenerse a partir de dispositivos lógicos programables o matrices de puertas programables en campo (FPGA) , y una reducción del coste de los mismos.

El documento WO 99/41846 es un ejemplo de un detector DSSS para detectar una sincronización entre una secuencia de ensanchamiento de señal de espectro ensanchado. El detector comprende al menos una ramificación que comprende una pluralidad de correladores conectados en cascada entre sí y separados unos de otros por un bloque de retardo de ramificación. Cada correlador correlaciona chips de la secuencia de ensanchamiento con chips de la señal de espectro ensanchado y genera su propio valor de correlación. Los medios de detección de

concordancia reciben los valores de correlación y detectan cuando los chips de la secuencia de ensanchamiento están alineados con los chips de la señal de espectro ensanchado.

Como se conoce, en un sistema DSSS aperiódico, la secuencia PN experimenta una modulación de señal debido a la señal de información que se está transmitiendo. Considerando que la señal de información es una palabra digital

de 1 a 0, y suponiendo que 1 se transmite con un signo positivo y 0 se transmite con un signo negativo, una porción de la secuencia PN puede modularse y transmitirse con un signo positivo, mientras que la otra porción puede modularse y transmitirse con un signo negativo.

La secuencia PN se somete de este modo a una modulación de señal impredecible debido a los bits de la señal de

información, ya que no existe relación entre la duración de la secuencia PN y la duración de cada bit de la señal de información. En el receptor, por lo tanto, se desconoce en que punto de la secuencia PN puede haber un cambio de signo.

La técnica de filtro adaptado no se puede aplicar con sistemas DSSS aperiódicos ya que, incluso cuando la

45 secuencia PN está alineada perfectamente con la señal de información, la salida del correlador puede no ser máxima. De hecho, la parte modulada positivamente de la secuencia PN contenida en la señal de información recibida se correlaciona... [Seguir leyendo]

Reivindicaciones:

1. Un detector DSSS (19) para detectar una sincronización entre una señal de espectro ensanchado (r (nTc) ) , que tiene una pluralidad de chips, r (n) , y un valor del factor de ensanchamiento, N, y una secuencia de

ensanchamiento, PN, que tiene una pluralidad de chips, pi, comprendiendo el detector DSSS (19) al menos una ramificación (16) adaptada para recibir la señal de espectro ensanchado, comprendiendo la al menos una ramificación una pluralidad de correladores (1) , incluyendo cada correlador un número, M, de fases de correlación

(2) que es inferior a dicho valor del factor de ensanchamiento, N, estando los correladores (1) conectados en cascada entre sí y separados entre sí por un bloque de retardo de ramificación (20) , estando dicho bloque de retardo

de ramificación (20) adaptado para retardar la señal de espectro ensanchado recibida por una cantidad de retardo, N-M, que es inferior al valor del factor de ensanchamiento, N, comprendiendo cada correlador (1) medios de correlación (3, 4, 12) para correlacionar chips de la secuencia de ensanchamiento con chips de la señal de espectro ensanchado y generar cada una un valor de correlación propio (y (n) ) , comprendiendo adicionalmente el detector DSSS (19) medios de detección de concordancia (27, 22, 23) para recibir

dichos valores de correlación y detectar cuando dichos chips de la secuencia de ensanchamiento están alineados con dichos chips de la señal de espectro ensanchado.

2. Un detector DSSS de acuerdo con la reivindicación 1, en el que dichos medios de detección de concordancia (27, 22, 23) comprenden un elemento sumador de ramificación (27) adaptado para recibir dichos

valores de correlación y generar una señal de suma de ramificación (s1 (n) ) ; y un detector de máximo (23) adaptado para detectar un máximo de dicha señal de suma de ramificación.

3. Un detector DSSS de acuerdo con la reivindicación 1 ó 2, en el que cada fase de correlación (2) tiene una entrada de fase (13) configurada para recibir un chip, r (n) , r (n-1) , ..., r (n-M-1) , de la señal de espectro 25 ensanchado (r (nTc) ) , a elemento de retardo del correlador (11) conectado a dicha entrada de fase, un elemento de correlación de chips (12) conectado a dicha entrada de fase y configurado para correlacionar un chip de la señal de espectro ensanchado con un coeficiente propio, c1, c2, ..., cM, una primera salida de datos (16) conectada a dicho elemento de correlación de chips (12) y que transmite un chip correlacionado, r (n) ·c1, r (n-1) ·c2, ..., r (n-M-1) ·cM, y una segunda salida de datos (15) conectada a dicho elemento de retardo de correlador (11) y a una fase de correlación

posterior (2) ; comprendiendo adicionalmente el correlador (1) un elemento de suma (3) adaptado para recibir dichos chips correlacionados y calcular una suma de correlación (rs (n) ) y un elemento de módulo (4) adaptado para recibir dicha suma de correlación y calcular el valor de correlación (y (n) ) .

4. Un detector DSSS de acuerdo con la reivindicación 3, en el que los elementos de correlación son 35 multiplicadores (12) .

5. Un detector DSSS de acuerdo con la reivindicación 3 ó 4, en el que dichos coeficientes (c1, c2, ..., cM) de dichas fases de correlación (2) se seleccionan entre los chips (pi) de dicha secuencia de ensanchamiento, PN, y en el que los coeficientes, c1, c2, ..., cM, de un primer correlador (1) de dicha pluralidad de correladores (1) son

iguales a los primeros chips M, p1, p2, ..., pM, de dicha secuencia de ensanchamiento, PN, y los coeficientes de los correladores posteriores (1) son iguales a M chips posteriores de dicha secuencia de ensanchamiento, separados por N chips con respecto a los coeficientes correspondientes de un correlador inmediatamente anterior (1) , siendo M el número de fases de correlación (2) en cada correlador (1) , y siendo N el valor del factor de ensanchamiento.

45 6. Un detector DSSS de acuerdo con la reivindicación 5, en el que cada bloque de retardo de ramificación (20) está adaptado para generar un retardo de N-M chips.

7. Un detector DSSS de acuerdo con cualquiera de las reivindicaciones anteriores, que comprende m-1 ramificaciones adicionales (17, 25) , con m ≥ 2, recibiendo cada ramificación adicionalmente dicha señal de espectro

50 ensanchado (r (nTc) ) e incluyendo una pluralidad de correladores (1) conectados en cascada entre sí y separados unos de otros por un bloque de retardo de ramificación (20) , comprendiendo cada correlador de las ramificaciones adicionales medios de correlación (3, 4, 12) para correlacionar chips, pi, de la secuencia de ensanchamiento, PN, con chips de la señal de espectro ensanchado.

55 8. Un detector DSSS de acuerdo con la reivindicación 7, que depende de la reivindicación 4, en el que los correladores (1) de dichas ramificaciones adicionales (17, 25) comprenden cada una M fases de correlación (2) , en las que

M= (k/m) ·N

k es un número positivo, m es el número de ramificaciones que incluye dicha al menos una ramificación (16) y dichas ramificaciones adicionales (17, 25) , N es el factor de ensanchamiento de la señal de espectro ensanchado, y (k/m) <1.

9. Un detector DSSS de acuerdo con la reivindicación 8, en el que la señal de espectro ensanchado (r (nTc) ) introducida en la ramificación m (16; 17; 25) se retrasa por (m-1) (N-M) chips.

10. Un detector DSSS de acuerdo con cualquiera de las reivindicaciones 7-9, que dependen de la

reivindicación 3, en el que cada ramificación adicional (17, 25) comprende un elemento sumador de ramificación adicional (27) conectado a dichos correladores (1) de una ramificación adicional propia y adaptado para generar una señal de suma de ramificación propia (s2 (n) , s3 (n) ) ; y un detector de máximo (22, 23) adaptado para detectar un máximo entre dichas señales de suma de ramificaciones (s1 (n) , s2 (n) , s3 (n) ) .

11. Un detector DSSS de acuerdo con la reivindicación 10, en el que dicho detector de máximo (22, 23) comprende un comparador (23) adaptado para generar una señal de ramificación máxima, comprendiendo adicionalmente el detector un multiplexor (22) adaptado para recibir dicha señal de ramificación máxima y dichas señales de suma de ramificaciones (s1 (n) , s2 (n) , s3 (n) ) y para transmitir una señal de suma de ramificaciones máxima (dout) en respuesta a la señal de ramificación máxima.

12. Un módem DSSS que comprende un detector DSSS (19) de acuerdo con cualquiera de las reivindicaciones 1-11 y un desmodulador (47) adaptado para recibir dicha señal de espectro ensanchado (r (nTc) ) y la señal de suma de ramificación máxima (dout) .

13. Un procedimiento de detección de una sincronización entre una señal de espectro ensanchado (r (nTc) ) , que tiene una pluralidad de chips, r (n) , y un valor del factor de ensanchamiento, N, y una secuencia de ensanchamiento, PN, que tiene una pluralidad de chips, pi, que comprende las etapas de:

a. recibir la señal de espectro ensanchado (r (nTc) ) por una pluralidad de correladores (1) conectados en cascada

entre sí, incluyendo cada correlador un número (M) de fases de correlación (2) que es inferior a dicho valor del factor de ensanchamiento, N;

b. generar al menos una señal retardada, r ( (n-1) Tc) , a partir de la señal de espectro ensanchado (r (nTc) ) que retarda la señal de espectro ensanchado recibida por una cantidad de retardo, N-M, que es inferior al valor del factor de ensanchamiento, N;

c. correlacionar la señal de espectro ensanchado y la señal retardada con chips de la secuencia de ensanchamiento para generar valores de correlación (y (n) ) ; y

d. detectar una concordancia entre la señal de espectro ensanchado y la secuencia de ensanchamiento en base a dichos valores de correlación.

14. Un procedimiento de acuerdo con la reivindicación 13, en el que la etapa de detectar una concordancia comprende la adición de dichos valores de correlación (y (n) ) para generar una primera señal de suma de ramificación (s1 (n) ) y la detección de un máximo de dicha señal de suma de ramificación.

15. Un procedimiento de acuerdo con la reivindicación 13 ó 14, en el que dicha al menos una señal

45 retardada, r ( (n-1) Tc) , se retrasa para generar al menos una señal retardada adicional, r ( (n-2) Tc) , y el procedimiento comprende la etapa de correlacionar la señal retardada adicional con chips adicionales (pi) de la secuencia de ensanchamiento para generar valores de correlación adicionales (y (n) ) .

16. Un procedimiento de acuerdo con cualquiera de las reivindicaciones 13-15, en el que la etapa de

50 correlacionar comprende recibir un chip r (n) , r (n-1) , ..., r (n-M-1) de la señal de espectro ensanchado (r (nTc) ) o señales retardadas, r ( (n-1) Tc) , r ( (n-2) Tc) , en una fase de correlación (2) , retrasar el chip recibido, suministrar el chip retardado recibido a una fase de correlación posterior (2) , realizar una correlación de chips entre el chip recibido y un coeficiente, c1, c2, ..., cM, suministrar el resultado de la correlación de chips, r (n) ·c1, r (n-1) ·c2, ..., r (n-M-1) ·cM, a un elemento de suma (3) , calcular una suma de correlación (s1 (n) ) y calcular dicho valor de correlación (y (n) ) .

17. Un procedimiento de acuerdo con la reivindicación 16, que depende de la reivindicación 15, en el que la correlación de chips se realiza mediante M fases de correlación (2) , estando seleccionados los coeficientes, c1, c2, ..., cM, de dichas fases de correlación (2) entre los chips de dicha secuencia de ensanchamiento, PN, y en el que las etapas de correlacionar la señal de espectro ensanchado (r (nTc) ) , correlacionar la al menos una señal retardada, r ( (n-1) Tc) , y correlacionar la al menos una señal retardada adicional, r ( (n-2) Tc) , se realizan mediante una pluralidad de correladores (1) , en el que los coeficientes de un primer correlador de dicha pluralidad de correladores son iguales a los primeros M chips, p1, p2, ..., pM, de dicha secuencia de ensanchamiento PN, y los coeficientes de los correladores posteriores son iguales a los M chips posteriores de dicha secuencia de ensanchamiento, separados

por N chips con respecto a los coeficientes correspondientes de un correlador inmediatamente anterior, donde N es el valor del factor de ensanchamiento.

18. Un procedimiento de acuerdo con la reivindicación 17, en el que las etapas de retrasar la señal de

espectro ensanchado (r (nTc) ) y retrasar la al menos una señal retardada, r ( (n-1) Tc) , comprende generar un retardo 10 de N-M chips.

19. Un procedimiento de acuerdo con cualquiera de las reivindicaciones 13-18, generando al menos una señal de ramificación retardada, r ( (n-M) Tc) , a partir de la señal de espectro ensanchado; correlacionando la señal de ramificación retardada con chips, pi, de la secuencia de ensanchamiento, PN, para generar los segundos valores de

correlación (y (n) ) ; sumando dichos segundos valores de correlación para obtener unos segundos valores de suma de ramificación (s2 (n) ) ; comparando dichos primeros (s1 (n) ) y segundos (s2 (n) ) valores de suma de ramificación; transmitiendo el mayor del primer y el segundo valores de suma de ramificación; generando una secuencia (dout) de valores de suma de ramificación máxima y detectando una sincronización en base a dicha secuencia (dout) .

Patentes similares o relacionadas:

Procedimiento de emulación del sonido de un amplificador de válvulas de vacío, del 23 de Agosto de 2017, de MARTINEZ GARCIA-CASARRUBIOS, José Manuel: Procedimiento de emulación del sonido de un amplificador de válvulas de vacío grabado en un estudio profesional mediante un pedal preamplificadar de estado sólido […]

Método y sistema de determinación de la duración de los potenciales de acción de unidad motora en señales electromiográficas intramusculares, del 17 de Junio de 2014, de UNIVERSIDAD PUBLICA DE NAVARRA: Método y sistema de determinación de la duración de los potenciales de acción de unidad motora en señales electromiográficas intramusculares.

La invención […]

Método y sistema de determinación de la duración de los potenciales de acción de unidad motora en señales electromiográficas intramusculares, del 17 de Junio de 2014, de UNIVERSIDAD PUBLICA DE NAVARRA: Método y sistema de determinación de la duración de los potenciales de acción de unidad motora en señales electromiográficas intramusculares.

La invención […]

PROCEDIMIENTO PARA LA OBTENCION DE LA ACTIVIDAD DE TRANSICION DE UN CIRCUITO A PARTIR DE SU FUNCION DE TRANSFERENCIA, del 14 de Julio de 2010, de UNIVERSITAT POLITECNICA DE CATALUNYA: Procedimiento para la obtención de la actividad de transición de un circuito a partir de su función de transferencia. Procedimiento para la obtención […]

PROCEDIMIENTO DE ESTIMACION DE UNA MATRIZ DE CORRELACION DE SEÑALES INTERFERENTES RECIBIDAS POR UNA RED DE CAPTADORES., del 16 de Mayo de 2007, de THALES: Procedimiento para estimar la matriz de correla- ción de señales de características desconocidas recibidas por una red que comprende un número N de captadores, […]

CORRELACIONADOR PARALELO DE BAJA POTENCIA PARA MEDIR LA CORRELACION ENTRE SEGMENTOS DE SEÑAL DIGITAL., del 16 de Junio de 2002, de GENERAL ELECTRIC COMPANY: LA CORRELACION ENTRE UN PAR DE SEGMENTOS DE SEÑALES DIGITALES SE MIDE CON UN APARATO QUE INCLUYE UNA PLURALIDAD DE MULTIPLICADORES . […]

UN CIRCUITO CORRELADOR DE 1 BIT/2 NIVELES DE ALTA VELOCIDAD CON CAPACIDAD DE AUTOCALIBRACION DE LA FUNCION FRINGE-WASH., del 16 de Diciembre de 2000, de UNIVERSITAT POLITECNICA DE CATALUNYA: Un circuito correlador de 1 bit/2 niveles de alta velocidad con capacidad de autocalibración de la función de fringe - wash. Si bien la medida de la función de correlación cruzada […]

METODO Y APARATO PARA LA SIMULTANEA CONVOLUCION MULTIPLE DE IMAGENES BINARIAS DIGITALES, UTILIZANDO UN UNICO CONVOLUCIONADOR CON UNA MASCARA BINARIA PARA DETERMINAR LAS DENSIDADES DE PIXEL., del , de UNITED PARCEL SERVICE OF AMERICA, INC.: SE PRESENTA UN SISTEMA PARA ENROLLAR SIMULTANEAMENTE UNA PRIMERA Y UNA SEGUNDA IMAGEN DIGITAL BINARIA EN PARALELO CON UN ENROLLADOR SIMPLE QUE TIENE UNA […]

BUSCADOR PROGRAMABLE DE FILTRO ADAPTADO PARA LA BUSQUEDA DE MULTIPLES SEÑALES PILOTO, del 16 de Diciembre de 2007, de QUALCOMM INCORPORATED: Un buscador programable de filtro adaptado que comprende: un registro de desplazamiento (401A-K, 403A-K, 800A-K) que funciona como un registro de desplazamiento […]

BUSCADOR PROGRAMABLE DE FILTRO ADAPTADO PARA LA BUSQUEDA DE MULTIPLES SEÑALES PILOTO, del 16 de Diciembre de 2007, de QUALCOMM INCORPORATED: Un buscador programable de filtro adaptado que comprende: un registro de desplazamiento (401A-K, 403A-K, 800A-K) que funciona como un registro de desplazamiento […]