CHIP QUE COMPRENDE UN MEMS DISPUESTO EN UN CIRCUITO INTEGRADO Y PROCEDIMIENTO DE FABRICACION CORRESPONDIENTE.

Chip que comprende un MEMS dispuesto en un circuito integrado y procedimiento de fabricación correspondiente.

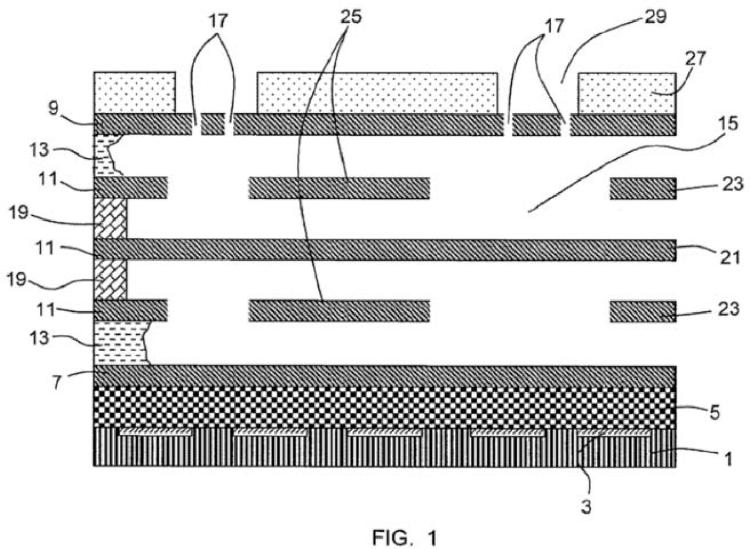

Clip que comprende un circuito integrado, con: A) unas capas que configuran unos elementos eléctricos y/o electrónicos sobre un substrato de material semiconductor, B) una estructura de capas de interconexión, con una pluralidad de capas de material conductor (7, 9) separadas por unas capas de material dieléctrico (13), C) por lo menos un MEMS dispuesto en la estructura de capas de interconexión. El MEMS comprende un espacio hueco (15) con una parte del mismo dispuesta debajo de una lámina de material conductor perteneciente a una de las capas de material conductor. El procedimiento de fabricación comprende una etapa de interconexión, en la que se genera la estructura de capas de interconexión, y un ataque posterior con HF gaseoso durante el cual se genera el espacio hueco (15) del MEMS

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P200901282.

Solicitante: BAOLAB MICROSYSTEMS S.L..

Nacionalidad solicitante: España.

Provincia: BARCELONA.

Inventor/es: MONTANYA SILVESTRE,JOSEP.

Fecha de Solicitud: 20 de Mayo de 2009.

Fecha de Publicación: .

Fecha de Concesión: 18 de Mayo de 2011.

Clasificación Internacional de Patentes:

- B81B7/02 TECNICAS INDUSTRIALES DIVERSAS; TRANSPORTES. › B81 TECNOLOGIA DE LAS MICROESTRUCTURAS. › B81B DISPOSITIVOS O SISTEMAS DE MICROESTRUCTURA, p. ej. DISPOSITIVOS MICROMECANICOS (elementos piezoeléctricos, electroestrictivos o magnetoestrictivos en sí H01L 41/00). › B81B 7/00 Sistemas de microestructura. › que tienen distintos dispositivos eléctricos u ópticos de particular importancia por su función, p.ej. sistemas micro-electromecánicos (SMEM, MEMS) (B81B 7/04 tiene prioridad).

- H01L21/30 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 21/00 Procedimientos o aparatos especialmente adaptados para la fabricación o el tratamiento de dispositivos semiconductores o de dispositivos de estado sólido, o bien de sus partes constitutivas. › Tratamiento de cuerpos semiconductores utilizando procesos o aparatos no cubiertos por los grupos H01L 21/20 - H01L 21/26 (fabricación de electrodos sobre estos cuerpos H01L 21/28).

Clasificación PCT:

- B81B7/02 B81B 7/00 […] › que tienen distintos dispositivos eléctricos u ópticos de particular importancia por su función, p.ej. sistemas micro-electromecánicos (SMEM, MEMS) (B81B 7/04 tiene prioridad).

- H01L21/30 H01L 21/00 […] › Tratamiento de cuerpos semiconductores utilizando procesos o aparatos no cubiertos por los grupos H01L 21/20 - H01L 21/26 (fabricación de electrodos sobre estos cuerpos H01L 21/28).

Fragmento de la descripción:

Chip que comprende un MEMS dispuesto en un circuito integrado y procedimiento de fabricación correspondiente.

Campo de la invención

La invención se refiere a un procedimiento de fabricación de un chip que comprende un MEMS dispuesto en un circuito integrado, donde el MEMS comprende por lo menos un espacio hueco. El procedimiento comprende:

a) unas etapas de generación de capas que configuran unos elementos eléctricos y/o electrónicos sobre un substrato de material semiconductor, y

b) una etapa de interconexión, en la que se genera una estructura de capas de interconexión y que comprende la deposición de por lo menos una capa inferior de material conductor y una capa superior de material conductor separadas por por lo menos una capa de material dieléctrico.

La invención también se refiere a un chip que comprende un circuito integrado, donde el circuito integrado comprende:

A) unas capas que configuran unos elementos eléctricos y/o electrónicos sobre un substrato de material semiconductor, y

B) una estructura de capas de interconexión, con por lo menos una capa inferior de material conductor y una capa superior de material conductor separadas por por lo menos una capa de material dieléctrico.

Estado de la técnica

Son perfectamente conocidos los chips que comprenden un circuito integrado. El circuito integrado es un dispositivo semiconductor que tiene un substrato de un material semiconductor y sobre el que se depositan una serie de capas, preferentemente mediante técnicas fotolitográficas, eventualmente se dopan, se polarizan y se atacan, de manera que se generan unos elementos eléctricos (como por ejemplo resistencias y condensadores, e incluso impedancias) y/o unos elementos electrónicos (como por ejemplo diodos y transistores). Posteriormente se depositan otras capas, que establecen las conexiones eléctricas necesarias, formando la estructura de capas de interconexión.

De acuerdo con la invención, el substrato es preferentemente de un material del grupo formado por Si, Ge, SiGe, GaAs, GaN y zafiro. Muy preferentemente el substrato es de Si.

De acuerdo con la invención, el chip es preferentemente de una tecnología del grupo formado por MOSFET, bipolar y BiCMOS, entendiéndose que la tecnología MOSFET incluye las variantes CMOS, PMOS, NMOS, UltraCMOS, SOI y SOS. Muy preferentemente el chip es de tecnología CMOS.

Por su parte, los microelectromecanismos o sistemas microelectromecánicos, usualmente abreviados MEMS, son pequeños dispositivos electromecánicos fabricados también por tecnologías de deposición de capas mediante técnicas fotolitográficas. Una característica básica de los MEMS es que tienen cavidades o espacios huecos en su interior, que pueden estar rellenados de líquidos o gases, mientras que los circuitos integrados convencionales son dispositivos totalmente macizos, es decir, sin ningún tipo de huecos (lógicamente, en la presente descripción y reivindicaciones se entiende por huecos a cavidades de tamaño superior que los huecos a escala atómica o subatómica). En la mayoría de los casos los MEMS tienen en su interior elementos móviles, que pueden estar unidos por alguno de sus extremos al resto de la estructura del MEMS o que pueden estar totalmente sueltos (como una pieza totalmente separada del resto, es decir, que no está unida físicamente con su entorno) en el interior de un alojamiento al menos parcialmente cerrado (para evitar que la pieza suelta se "escape" del MEMS).

Es frecuente que en un mismo chip se tenga que incluir tanto un MEMS como un circuito integrado que, entre otras cosas, tendrá la función de controlar el MEMS. Hay varias técnicas para fabricar un chip que incluya tanto un MEMS como un circuito integrado. Una primera técnica consiste en fabricar un elemento encima del otro. Otra técnica consiste en juntar los dos elementos (el MEMS y el circuito integrado) en un substrato común y unirlos entre sí por diversos medios, mediante una técnica denominada MCM (del inglés "multiple-chip-module"). Sin embargo todas estas técnicas no permiten una fabricación en masa y en paralelo como se hace en el caso de los chips incluidos en una oblea, no permiten establecer elevadas cantidades de conexiones entre el MEMS y el circuito integrado, las prestaciones de radiofrecuencia sufren una degradación importante y el rendimiento del conjunto es pobre. Adicionalmente, el coste es elevado.

Por otro lado, otro inconveniente presente en el estado de la técnica es que los MEMS solamente pueden ser diseñados con una precisión de aproximadamente 1 miera, siendo muy difícil conseguir reducir esta precisión.

Sumario de la invención

La invención tiene por objeto superar estos inconvenientes. Esta finalidad se consigue mediante un procedimiento de fabricación de un chip del tipo indicado al principio caracterizado porque tras dicha etapa b) de interconexión tiene lugar una etapa c) que comprende un ataque con HF (fluoruro de hidrógeno) gaseoso, donde durante el ataque se genera (entre otras cosas) el espacio hueco del MEMS en la estructura de capas de interconexión.

Efectivamente la presente invención tiene por objeto integrar totalmente la fabricación del MEMS en la fabricación del circuito integrado, de manera que el circuito integrado sea generado siguiendo la secuencia de pasos normal que le es propia, de manera que no se interfiera en ningún momento ni en la calidad ni en las prestaciones del procedimiento de fabricación normal del circuito integrado. Únicamente se añade una etapa adicional (o eventualmente más de una, como se verá más adelante). Para ello se tiene en cuenta que el procedimiento de fabricación del circuito integrado incluye una etapa denominada de interconexión, en la que se depositan una pluralidad de capas de material conductor (preferentemente son de aluminio, cobre o sus aleaciones (como por ejemplo AlCu, AlSi, AlCuSi, etc.), eventualmente con un recubrimiento de titanio y/o TiN) separadas entre sí por unas capas de material dieléctrico (usualmente denominadas IMD, del inglés inter metal dielectric), que preferentemente es dióxido de silicio o compuestos derivados del mismo. Esta estructura de capas de interconexión tiene por objeto establecer las interconexiones necesarias entre los diversos componentes eléctricos y/o electrónicos del circuito integrado y establecer los puntos de contacto necesarios para establecer las conexiones eléctricas con el exterior. La invención propone aprovechar esta etapa de interconexión para incluir, en la propia estructura de capas de interconexión, la estructura de capas de material conductor y capas de material dieléctrico necesarias para la obtención del MEMS. Normalmente el circuito integrado ya necesita, para su uso propio, tres o más capas de material conductor (la estructura de capas de interconexión usualmente comprende entre 2 y 10 capas de material conductor). Por ello, es probable que por el hecho de incluir el MEMS en la estructura de capas de interconexión no se necesiten más capas. En cualquier caso, aun suponiendo que, por el hecho de incluir el MEMS en la estructura de capas de interconexión, sea necesario incluir algunas capas de material conductor (y/o capas de material dieléctrico) adicionales, estas capas adicionales se aplican con la misma tecnología y durante la misma etapa que las capas de interconexión que el circuito integrado necesita para su uso propio. De esta manera, el procedimiento de fabricación del circuito integrado no se ve afectado cualitativamente por el hecho de incluirle un MEMS en su estructura de capas de interconexión. La etapa de ataque con HF gaseoso permite eliminar el material dieléctrico dispuesto entre las capas de material conductor durante la etapa de interconexión.

El HF, en particular el HF seco, ataca de una forma muy selectiva el material dieléctrico, mientras que las capas de material conductor casi no son atacadas. Además, el ataque con HF se extiende por debajo de las capas de material conductor, rodeándolo, lo que permite la creación de huecos o cavidades, e incluso la fabricación de piezas sueltas.

Normalmente los procedimientos de fabricación de chips comprenden una etapa de pasivado que, entre otras cosas, tiene por objeto aislar el circuito integrado del entorno y/o ambiente, tanto desde un punto de vista eléctrico como físico/químico. La etapa de ataque con HF gaseoso puede realizarse justo después de la etapa b) de interconexión y antes de la etapa de pasivado. Esto puede ser útil en algunos casos, ya que se reducen etapas del proceso. Sin embargo, puede ser interesante...

Reivindicaciones:

1. Procedimiento de fabricación de un chip que comprende un MEMS dispuesto en un circuito integrado, donde dicho MEMS comprende por lo menos un espacio hueco (15), donde dicho procedimiento comprende:

caracterizado porque

2. Procedimiento según la reivindicación 1, caracterizado porque entre dicha etapa b) y dicha etapa c) se realizan las siguientes etapas:

3. Procedimiento según la reivindicación 2, caracterizado porque en dicha etapa b') de generación de una capa de pasivado (27), dicha capa de nitruro de silicio es una capa de nitruro de silicio rico en silicio.

4. Procedimiento según la reivindicación 3, caracterizado porque dicha capa de nitruro de silicio rico en silicio tiene un índice de refractividad superior a 2'2, y preferentemente superior a 2'3.

5. Procedimiento según cualquiera de las reivindicaciones 1 a 4, caracterizado porque tras dicha etapa c) se somete a dicho chip a un calentamiento.

6. Procedimiento según la reivindicación 5, caracterizado porque se somete, a dicho chip a un calentamiento a una temperatura superior a 115ºC, preferentemente, superior a 170ºC, y muy preferentemente superior a 180ºC.

7. Procedimiento según cualquiera de las reivindicaciones 1 a 6, caracterizado porque tras dicha etapa c) se realiza una etapa de recubrimiento ALD.

8. Procedimiento según la reivindicación 7, caracterizado porque dicha etapa de recubrimiento ALD se hace en un tiempo menor al tiempo de percolación.

9. Procedimiento según una de las reivindicaciones 7 u 8, donde dicho MEMS tiene un elemento móvil (21), caracterizado porque se somete a dicho elemento móvil (21) a un movimiento durante dicha etapa de recubrimiento ALD.

10. Procedimiento según cualquiera de las reivindicaciones 1 a 9, caracterizado porque se realiza una etapa de generación de una nueva capa de sellado.

11. Procedimiento según cualquiera de las reivindicaciones 1 a 10, caracterizado porque dicha capa superior de material conductor (9) tiene una pluralidad de orificios (17) que son de una dimensión tal que dejan pasar al HF pero que, preferentemente, no dejan pasar los nitruros.

12. Procedimiento según la reivindicación 11, caracterizado porque cada uno de dichos orificios (17) tiene un diámetro menor o igual que 500 nm, y preferentemente menor o igual que 100 nm.

13. Procedimiento según una de las reivindicaciones 11 o 12, caracterizado porque antes de dicha etapa de generación de una nueva capa de sellado, se somete a dicha capa superior de material conductor (9) a un recubrimiento ALD.

14. Procedimiento según cualquiera de las reivindicaciones 1 a 13, caracterizado porque por debajo de dicha capa inferior de material conductor (7) se añade una capa específica que resista el ataque de HF.

15. Procedimiento según cualquiera de las reivindicaciones 1 a 14, caracterizado porque en dicha etapa de interconexión se depositan como máximo 10 capas de material conductor y, preferentemente, se depositan como máximo 6 capas de material conductor.

16. Procedimiento según cualquiera de las reivindicaciones 10 a 15, caracterizado porque dicha eliminación al menos parcial de dicha etapa b'') genera unas aberturas (29) que están dispuestas sobre unas placas (31) de material conductor pertenecientes a dicha capa superior de material conductor (9) y porque en dicha etapa de generación de una nueva capa de sellado dicha nueva capa de sellado llena, por lo menos parcialmente, el espacio hueco entre cada una de dichas aberturas (29) y su correspondiente placa (31).

17. Procedimiento según cualquiera de las reivindicaciones 1 a 16, caracterizado porque alrededor de dicho MEMS se añade un tabique de material resistente al HF, donde dicho tabique se extiende perpendicularmente a dicho substrato y envuelve a dicho MEMS en sentido paralelo a dicho substrato.

18. Procedimiento según cualquiera de las reivindicaciones 1 a 17, caracterizado porque se establece por lo menos una interconexión directa entre dicho substrato y por lo menos una de dichas capas de material conductor mediante un material resistente al HF.

19. Procedimiento según cualquiera de las reivindicaciones 1 a 18, caracterizado porque se establece por lo menos una interconexión entre el sustrato y por lo menos una de dichas capas de material conductor mediante un material resistente al HF, donde entre el sustrato y dicho material hay una capa de silicio amorfo.

20. Chip que comprende un circuito integrado, donde dicho circuito integrada comprende:

caracterizado porque comprende, adicionalmente, por lo menos un MEMS dispuesto en dicha estructura de capas de interconexión, donde dicho MEMS comprende por lo menos un espacio hueco (15), donde por lo menos una parte de dicho espacio hueco (15) está dispuesta debajo de una lámina de material conductor perteneciente a una de dichas capas de material conductor.

21. Chip según la reivindicación 20, caracterizado porque comprende adicionalmente,

22. Chip según una de las reivindicaciones 20 o 21, caracterizado porque dicho MEMS comprende un elemento conductor que es una pieza suelta.

23. Chip según la reivindicación 22, caracterizado porque dicho MEMS comprende, adicionalmente, por lo menos dos placas de condensador aptas para generar unos campos electrostáticos sobre dicha pieza suelta capaces de mover dicha pieza suelta.

24. Chip según la reivindicación 23, caracterizado porque dicho MEMS comprende, adicionalmente por lo menos dos puntos de contacto de un circuito eléctrico, donde dicha pieza suelta es apta para adoptar una posición en la que está en contacto simultáneamente con ambos puntos de contacto, de manera que se establece una conexión eléctrica entre dichos puntos de contacto, actuando así dicho MEMS como un relé.

25. Chip según cualquiera de las reivindicaciones 20 a 24, caracterizado porque comprende un dispositivo del grupo de dispositivos formado por relés eléctricos acelerómetros, inclinómetros, detectores de fuerzas de Coriolis, sensores de presión, micrófonos, sensores de caudal, sensores de temperatura, sensores de gas, sensores de campo magnético, dispositivos electroópticos, matrices de conmutación óptica, dispositivos proyectores de imágenes, matrices de conexión analógica, dispositivos emisores y/o receptores de señales electromagnéticas, fuentes de alimentación, convertidores DC/DC, convertidores AC/DC, convertidores DC/AC, convertidores A/D, convertidores D/A, y amplificadores de potencia.

26. Chip según cualquiera de las reivindicaciones 20 a 25, caracterizado porque la parte de dicha capa superior de material conductor (9) dispuesta sobre dicho MEMS tiene una pluralidad de orificios y porque la siguiente capa de material conductor dispuesta debajo de dicha capa superior de material conductor (9) tiene asimismo una pluralidad de orificios no alineados con los orificios de dicha capa superior de material conductor (9) de manera que dicho HF gaseoso debe realizar un recorrido en zig-zag para poder llegar a la zona de dicho MEMS.

Patentes similares o relacionadas:

Procedimiento de fabricación de un sensor de presión y sensor correspondiente, del 29 de Mayo de 2019, de AUXITROL SA: Procedimiento de fabricación de un sensor de presión que comprende las etapas siguientes: ensamblar (E1) un sustrato de soporte con una membrana […]

Micro-reflectrón para espectómetro de masas de tiempo de vuelo, del 14 de Marzo de 2018, de COMMISSARIAT A L'ENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES: Un micro-reflectrón para espectrómetro de masas de tiempo de vuelo que comprende un sustrato […]

Estabilización de frecuencia de un oscilador de referencia, del 30 de Noviembre de 2016, de Nokia Technologies OY: Un método para estabilizar la frecuencia de un oscilador de referencia basado en MEMS (Sistemas Micro Electro Mecánicos), caracterizado por que el oscilador de […]

Procedimiento de medición y registro de aceleraciones con sensores de bajo coste para su aplicación en sismología, y equipo para llevar a cabo dicho procedimiento, del 21 de Septiembre de 2015, de MARTIN GARCIA, Eduardo: Procedimiento de medición y registro de aceleraciones con sensores de bajo coste para su aplicación en sismología, y equipo para llevar a cabo dicho procedimiento […]

Procedimiento de medición y registro de aceleraciones con sensores de bajo coste para su aplicación en sismología, y equipo para llevar a cabo dicho procedimiento, del 21 de Septiembre de 2015, de MARTIN GARCIA, Eduardo: Procedimiento de medición y registro de aceleraciones con sensores de bajo coste para su aplicación en sismología, y equipo para llevar a cabo dicho procedimiento […]

MICRO-SONDA NEURONAL Y PROCEDIMIENTO DE FABRICACION DE LA MISMA, del 25 de Junio de 2015, de CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC): Procedimiento de fabricación de al menos una micro-sonda neuronal flexible, biocompatible e implantable, que comprender las etapas de: proporcionar […]

MICRO-SONDA NEURONAL Y PROCEDIMIENTO DE FABRICACION DE LA MISMA, del 25 de Junio de 2015, de CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC): Procedimiento de fabricación de al menos una micro-sonda neuronal flexible, biocompatible e implantable, que comprender las etapas de: proporcionar […]

ACTUADORES E INTERRUPTORES MEMS, del 13 de Febrero de 2012, de RÉSEAUX MEMS: Interruptor microelectromecánico (MEMS) montado sobre un sustrato , comprendiendo el interruptor MEMS: un primer actuador MEMS en voladizo (10, 10') que comprende […]

PROCESO DE PROTOTIPADO MULTIPLE PARA MICROSENSORES MECANICOS DE TIPO CAPACITIVO, del 2 de Febrero de 2011, de FARSENS, S.L: Proceso de prototipado múltiple para microsensores mecánicos de tipo capacitivo, basado en la identidad del valor de un determinado número de parámetros geométricos: en los microsensores […]

PROCESO DE PROTOTIPADO MULTIPLE PARA MICROSENSORES MECANICOS DE TIPO CAPACITIVO, del 2 de Febrero de 2011, de FARSENS, S.L: Proceso de prototipado múltiple para microsensores mecánicos de tipo capacitivo, basado en la identidad del valor de un determinado número de parámetros geométricos: en los microsensores […]

DISPOSITIVO PARA LA CONEXION DE DOS PUNTOS DE UN CIRCUITO ELECTRICO, del 1 de Octubre de 2007, de BAOLAB MICROSYSTEMS S.L.: Dispositivo para la conexión de dos puntos de un circuito eléctrico. El dispositivo se comporta externamente como un único relé, pero comprende un primer relé MEMS y por […]

DISPOSITIVO PARA LA CONEXION DE DOS PUNTOS DE UN CIRCUITO ELECTRICO, del 1 de Octubre de 2007, de BAOLAB MICROSYSTEMS S.L.: Dispositivo para la conexión de dos puntos de un circuito eléctrico. El dispositivo se comporta externamente como un único relé, pero comprende un primer relé MEMS y por […]