PROCEDIMIENTO PARA SINCRONIZAR DATOS E INTERFAZ DE TRANSMISION.

SE PROPONEN INTERFACES MUY SENCILLAS PARA LA TRANSMISION Y RECEPCION DE DATOS,

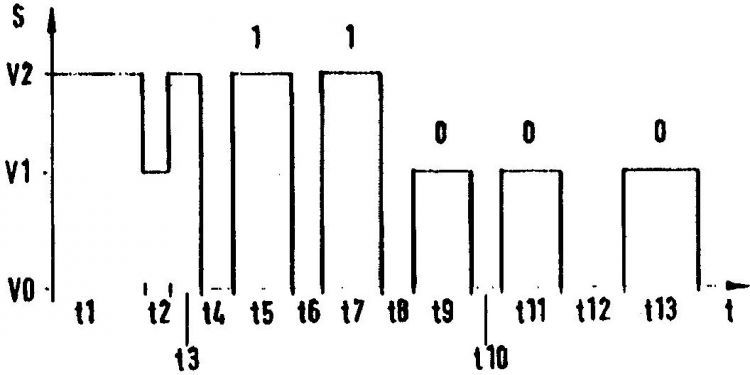

QUE ADEMAS PUEDEN OPERARSE CON UN PROCEDIMIENTO DE GRAN SIMPLICIDAD. EN LA INVENCION SE HA PREVISTO QUE POR EL BUS SE TRANSMITAN TRES NIVELES DIFERENTES. UNO DE ESTOS NIVELES (V0) SIRVE PARA GENERAR UNA SEÑAL DE SINCRONIZACION PARA LA TRANSMISION SUBSIGUIENTE DE UN BIT ALTO O DE UN BIT BAJO. LOS BITS SE TRANSMITEN A LOS OTROS DOS NIVELES (V2, V1). EN UNA VARIANTE, SE INTERCAMBIAN INFORMACIONES POR INTERFACES O POR LINEAS DE UNION QUE SE REPRESENTAN CON AYUDA DE DOS NIVELES DIFERENTES. EN ESTA VARIANTE SE GENERAN IMPULSOS DE SINCRONIZACION, ASI COMO DOS IMPULSOS DE INFORMACION DIFERENTES, QUE SE DIFERENCIAN POR SU LONGITUD

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/DE97/01532.

Solicitante: ROBERT BOSCH GMBH.

Nacionalidad solicitante: Alemania.

Dirección: POSTFACH 30 02 20,70442 STUTTGART.

Inventor/es: NASSWETTER, GUENTER, KOSS, THOMAS, SUELZLE, HELMUT, SCHLEUPEN, RICHARD, KOHL, WALTER, JAKOBI,LOTHAR.

Fecha de Publicación: .

Fecha Concesión Europea: 31 de Marzo de 2010.

Clasificación Internacional de Patentes:

- G06F13/40E2B

- G06F13/42S2

- H04L25/02K7

- H04L25/02K9

- H04L5/04 ELECTRICIDAD. › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › H04L 5/00 Disposiciones destinadas a permitir la utilización múltiple de la vía de transmisión. › estando representadas las señales por diferentes amplitudes o polaridades, p. ej. cuádruplex.

- H04L7/06 H04L […] › H04L 7/00 Disposiciones para sincronizar el receptor con el emisor. › diferiendo las señales de sincronización de las señales de información, en amplitud, polaridad o frecuencia.

Clasificación PCT:

- H04J3/06 H04 […] › H04J COMUNICACIONES MULTIPLEX (peculiar de la transmisión de información digital H04L 5/00; sistemas para transmitir las señales de televisión simultánea o secuencialmente H04N 7/08; en las centrales H04Q 11/00). › H04J 3/00 Time-division multiplex systems (H04J 14/08 takes precedence). › Disposiciones de sincronización.

Clasificación antigua:

- H04J3/06 H04J 3/00 […] › Disposiciones de sincronización.

Fragmento de la descripción:

Procedimiento para sincronizar datos e interfaz de transmisión.

Estado actual del arte

La presente invención hace referencia a un procedimiento para la transmisión de datos o de interfaces para la transmisión o la recepción de datos de acuerdo al tipo de las reivindicaciones independientes y hace referencia especialmente a un regulador de tensión con interfaz en un automóvil.

De la DE 35 06 118 ya se conoce un procedimiento para la transmisión de datos mediante una línea de datos, en el que se transmiten a través de la línea de datos una secuencia de primeros y segundos estados, que pueden ser distinguidos unos de otros. En este caso, estos estados representan un bit alto o un bit bajo.

La GB-A-2180712 hace referencia a un procedimiento para la transmisión de datos mediante una línea de transmisión mediante la transmisión de una secuencia de un primer o de un segundo estado, que pueden ser distinguidos entre sí y que representan un bit alto o un bit bajo, en la línea de transmisión, con lo que en la línea de transmisión se puede generar un tercer estado que se puede distinguir de los dos primeros estados, y el tercer estado es utilizado como señal de sincronización. En este caso, los estados son distinguidos entre sí con ayuda de la amplitud del pulso.

Además, la US-A-2794858 muestra un procedimiento para la transmisión de datos desde un primer dispositivo, que se encuentra conectado a través de, al menos, una línea de transmisión con un segundo dispositivo, con lo que en la línea de transmisión se generan secuencias de un primer o de un segundo estado, que pueden ser distinguidos entre sí, y en la línea de transmisión se puede generar un tercer estado que es diferente a los dos primeros estados, y el tercer estado es utilizado como señal de sincronización. En este caso, los dos primeros estados que representan señales de información se pueden distinguir en su amplitud de puso, mientras que la señal de sincronización como tercer estado es distinguida de las señales de información debido a una duración de pulso diferente.

Al respecto, la EP 00 082 38 A2 muestra un sistema multiplex de procesamiento de información en el que la información se encuentra codificada en su amplitud de pulso en forma de pares de dos bit. Sin embargo, debido a la tolerancia de sincronización del 25% en el marco del muestreo de bit en los, respectivos, dos bits de información el primer y el segundo bit se encuentran determinados en su duración de pulso y más precisamente de manera tal, que el segundo bit siempre posee el doble de la duración que el primer bit. De esta manera se garantiza que el muestreo del segundo bit realmente se realice siempre en el segundo bit, a pesar de la tolerancia mencionada del 25%. A cada transmisión de información se antepone, además, un pulso de sincronización que presenta una duración de pulso notablemente aumentada en relación con los bit de información para poder reconocerlo de forma unívoca como pulso de sincronización. De esta manera existen en total tres duraciones de pulso diferentes, con lo que, sin embargo, en el caso de los bits de información la duración del pulso siempre es igual y se encuentra determinada, de manera que la información o el respectivo estado se encuentra codificado en la amplitud del pulso de forma usual mediante bits.

La GB-A-2072463 muestra una red de transmisión de voz o de datos en la que una fuente de pulsos conectada a una línea de alimentación bifilar marca el final de ciclos temporales multiplex, con una ranura de control y ocho pares de ranuras de tiempo. Un microprocesador que realiza una llamada encuentra un par de ranura de tiempo libre y direcciona el punto de conexión llamado en la ranura de control. Las interfaces temporales multiplex de los dispositivos del punto de control que realizan y reciben la llamada transmiten pulsos en las ranuras de tiempo. Las interfaces de líneas de alimentación provocan una modulación y demodulación del ancho del pulso de los pulsos para la transmisión de voz en dúplex completo. Para ello, el microprocesador envía y recibe datos excluyendo pulsos que representan bits cero. Los datos se encuentran formateados de manera tal, que la interrupción más prolongada posible de la transmisión de voz asciende a diez ciclos de tiempo multiplex, en los que se pueden transmitir entonces datos digitales. Para la sincronización se encuentra prevista una señal de sincronización, cuya duración es claramente mayor que una señal de datos.

Es objeto de la presente invención, representar un sistema que pueda ser realizado de manera más sencilla y sin embargo más segura en relación con el estado actual del arte.

Ventajas de la invención

El procedimiento o las interfaces conforme a la invención con las características identificativas de las reivindicaciones independientes presenta en cambio la ventaja, de que los tres estados se pueden distinguir claramente a través de su duración de pulsos y que debido a la sincronización de cada bit alto o bit bajo los errores y tolerancias sólo son válidos para bits individuales.

Por ello, la sincronización puede ser generada en una de las estaciones de datos participantes y ser comunicada a las otras estaciones participantes a través de la línea de datos. De esta manera es posible, que sólo una de las estaciones de datos participantes presente internamente los medios para generar una señal de sincronización, mientras que las demás estaciones no deben presentar medios de este tipo.

Es especialmente ventajoso que también se pueda trabajar con dos niveles de tensión. Esta ventaja se logra realizando los pulsos de sincronización así como las otras dos informaciones, por ejemplo una información cero y una información uno, a través de pulsos con diferentes duraciones de señales. De forma ventajosa los pulsos que comprenden ambas informaciones comienzan simultáneamente con el pulso de sincronización correspondiente. De manera ventajosa la transmisión se realiza entre una primera estación de datos y una segunda estación de datos, que se encuentran unidas entre sí a través de una línea de transmisión Es especialmente ventajoso, que el sistema también se pueda implementar en el caso de múltiples receptores y que se genere un protocolo de transmisión.

En las reivindicaciones dependientes se indican perfeccionamientos y mejoras ventajosas del procedimiento o de la interfaz de acuerdo a las reivindicaciones independientes. La señal de sincronización es especialmente sencilla cuando consiste en que la línea de transmisión sea llevada al tercer estado por un tiempo mínimo predeterminado. La estación receptora puede ser sincronizada entonces en e flanco de señal que indica el final del tercer estado. La lectura de un bit alto o de un bit bajo es realizada entonces de manera sencilla porque después de la señal de sincronización es leído si la línea de datos se encuentra en el primer o en el segundo estado. Es ventajoso además, que la duración de la señal de sincronización o del bit alto o de un bit bajo no importa mientras superen un tiempo mínimo predeterminado que es necesario para el reconocimiento fiable del estado correspondiente en la línea de datos. Los diferentes estados son realizados de manera especialmente sencilla a través de diferentes niveles de tensión en la línea de datos.

La implementación de las interfaces conforme a la invención y del procedimiento conforme a la invención para la transmisión de datos es posible, de manera ventajosa, como aplicación de una interfaz sincrónica de bit en un automóvil. Una aplicación especialmente ventajosa de la interfaz es la conexión entre el regulador de tensión y la red de a bordo de un automóvil. Una conexión entre el regulador de tensión y el microordenador de la electrónica digital del motor como parte integrante del dispositivo de control también es posible de manera ventajosa.

Dibujos

Ejemplos de ejecución de la invención se explican en la siguiente descripción y se encuentran representados en los dibujos. La figura 1 muestra esquemáticamente dos estaciones de datos que se encuentran conectadas con una línea de datos; la figura 3 dos interfaces conforme a la invención y la figura 4 una lógica simple para la valoración de datos.

La figura 2 muestra un ejemplo de diferentes estados un línea de datos.

La figura 5 muestra, además, un diseño de la técnica de conmutación de una interfaz entre el regulador de tensión y la red de a bordo en un automóvil o la interfaz entre la electrónica digital del motor (DME) y el regulador de tensión. En la figura...

Reivindicaciones:

1. Procedimiento para la transmisión de datos mediante una línea de transmisión (15) mediante la transmisión de una secuencia de un primer o de un segundo estado, que pueden ser distinguidos entre sí, en la línea de transmisión, con lo que el primer estado corresponde a un bit alto y el segundo estado, a un bit bajo, con lo que en la línea de transmisión (15) se puede generar un tercer estado que se puede distinguir de los dos primeros estados, y que el tercer estado es utilizado como señal de sincronización, con lo que los estados son representados mediante duraciones de pulsos y las duraciones de los pulsos de los tres estados se diferencian entre sí, caracterizado porque para formar la señal de sincronización la línea de transmisión es llevada al tercer estado por un tiempo mínimo predeterminado, con lo que la línea de transmisión además es llevada por un tiempo mínimo predeterminado al primer o al segundo estado para indicar un bit alto o un bit bajo, y que antes de cada bit alto o bit bajo es transmitida una señal de sincronización.

2. Procedimiento conforme a la reivindicación 1, caracterizado porque la línea de transmisión presenta un estado de reposo si es mantenida en uno de los tres estados, y que el comienzo de una transmisión de datos es indicado porque la línea de transmisión es llevada a otro estado, diferente al de reposo.

3. Procedimiento conforme a una de las reivindicaciones anteriores, caracterizado porque los tres estados diferentes son realizados porque en un conductor eléctrico son generados diferentes niveles de tensión.

4. Procedimiento conforme a la reivindicación 1, caracterizado porque el primer dispositivo es un microprocesador, especialmente un dispositivo de control en un automóvil, y el segundo dispositivo es el regulador de tensión del automóvil.

5. Procedimiento conforme a la reivindicación 1 o 4, caracterizado porque existen múltiples receptores y se genera un protocolo de transmisión.

6. Interfaz (2) para emitir datos y que se encuentra unida a una línea de transmisión, con lo que la interfaz presenta primeros medios para generar una secuencia de un primer o un segundo estado, que pueden ser distinguidos entre sí, en la línea de transmisión, con lo que el primer estado corresponde a un bit alto y el segundo estado, a un bit bajo, y se encuentran previstos segundos medios para generar, cuando se implementa una señal de sincronización, un tercer estado en la línea de datos que puede ser distinguido el primer y del segundo estado, con lo que los medios representan los estados mediante duraciones de pulsos y las duraciones de los pulsos de los tres estados se diferencian entre sí, caracterizado porque los segundos medios se encuentran diseñados de manera tal, que para formar la señal de sincronización la línea de transmisión es llevada al tercer estado por un tiempo mínimo predeterminado, con lo que los primeros medios se encuentran diseñados de manera de llevar la línea de transmisión, además, por un tiempo mínimo predeterminado al primer o al segundo estado para indicar un bit alto o un bit bajo, y los segundos medios se encuentran diseñados de manera tal, que antes de cada bit alto o bit bajo es transmitida una señal de sincronización.

7. Interfaz conforme a la reivindicación 6, caracterizada porque los tres estados diferentes son realizados por niveles de tensión en un conductor eléctrico.

8. Interfaz conforme a la reivindicación 7, caracterizada porque los primeros medios presentan un divisor de tensión con una primera resistencia (5) y una segunda resistencia (6), porque la primera resistencia (5) se encuentra dispuesta entre una primera tensión (VCC) y un nodo, porque la segunda resistencia se encuentra dispuesta entre el nodo y un interruptor, y porque el interruptor se encuentra dispuesto entre la segunda resistencia (6) y una segunda tensión (masa), porque el interruptor se puede conmutar opcionalmente para la emisión de un bit alto o un bit bajo, y porque la línea de transmisión (15) se encuentra unido con el nodo (4).

9. Interfaz conforme a la reivindicación 8, caracterizada porque los segundos medios presentan un interruptor con el que la línea de transmisión se puede conectar con la primera o la segunda tensión, y que el interruptor se puede conmutar dependiendo de las señales de sincronización.

10. Interfaz conforme a la reivindicación 7 a 9, caracterizada porque para la activación de los interruptores se encuentran previstas una línea de datos (out-data) y una línea de sincronización (Out-CLK), y porque la línea de datos (Out-Data) y la línea de sincronización (Out-CLK) se encuentran conectadas con un microprocesador, especialmente un microprocesador de una unidad de control de motor.

11. Dispositivo con una interfaz conforme a la reivindicación 6.

12. Dispositivo conforme a la reivindicación 11, caracterizado porque los tres estados diferentes son realizados por niveles de tensión que pueden ser diferenciados entre sí.

Patentes similares o relacionadas:

Método y aparatos para la transmisión de señal de latido a un nivel más bajo que la solicitud de latido, del 15 de Marzo de 2017, de INTEL CORPORATION: Un dispositivo de usuario con acceso múltiple por división de código (CDMA) que comprende: una antena; un controlador configurado para controlar un transceptor […]

Aparatos para la transmisión de una señal de latido de corazón a un nivel inferior que la solicitud de latido de corazón, del 15 de Febrero de 2017, de INTEL CORPORATION: Una unidad de campo que comprende: al menos un procesador configurado para transmitir una primera señal que tenga uno de una pluralidad de formatos; […]

Método y aparato para la transmisión de una señal de latido de corazón a un nivel inferior que la solicitud de latido de corazón, del 16 de Noviembre de 2016, de INTEL CORPORATION: Un método en una unidad de campo para el alojamiento de canal de tráfico dinámico que comprende: - transmitir una señal de marcador en un intervalo de tiempo asignado, […]

Unidad móvil y procedimiento implementado en una unidad móvil, del 2 de Marzo de 2016, de INTEL CORPORATION: Un procedimiento en una unidad móvil para transmitir datos útiles (42a, 42b, 42c) a una estación base , comprendiendo el procedimiento transmitir una […]

Unidad móvil y procedimiento implementado en una unidad móvil, del 2 de Marzo de 2016, de INTEL CORPORATION: Un procedimiento en una unidad móvil para transmitir datos útiles (42a, 42b, 42c) a una estación base , comprendiendo el procedimiento transmitir una […]

Pasarela y estación de base basadas en la sincronización de contenido de ventana y su procedimiento, del 24 de Septiembre de 2014, de ALCATEL LUCENT: Una estación de base (200; eNB1; eNB2; eNB3) que comprende: una unidad de recepción configurada para recibir paquetes de datos desde […]

CODIFICADOR DE DIVERSIDAD DE TRANSMISION ESPACIO-TEMPORAL DE BLOQUES MODIFICADOS., del 1 de Noviembre de 2006, de INTERDIGITAL TECHNOLOGY CORPORATION: Un método para transmitir símbolos de datos en un sistema de comunicación de CDMA que incluye un transmisor , que tiene una matriz o conjunto geométricamente ordenado […]

DISPOSITIVO DE TRANSMISION Y RECEPCION PARA UNA RED CINCRONA CDMA PUNTO-MULTIPUNTO., del 16 de Marzo de 2005, de ALCATEL: Dispositivo emisor para una red síncrona (NET) CDMA de varios puntos a un punto, conteniendo una primera unidad para la generación de una […]

PROCEDIMIENTO Y DISPOSITIVOS PARA TRANSMITIR DATOS SOBRE UNA LINEA DE DATOS ENTRE UN APARATO CENTRAL DE CONTROL Y AL MENOS UNA INTERFAZ DE UN APARATO DE PROCESAMIENTO DE DATOS DE AL MENOS UN APARATO DESCENTRALIZADO DE PROCESAMIENTO DE DATOS, del 16 de Noviembre de 2008, de CONTINENTAL AUTOMOTIVE GMBH: Procedimiento para la transmisión de datos sobre una línea de datos (PDL) entre un aparato central de control (ECU) y al menos una interfaz de un aparato de procesamiento […]

PROCEDIMIENTO Y DISPOSITIVOS PARA TRANSMITIR DATOS SOBRE UNA LINEA DE DATOS ENTRE UN APARATO CENTRAL DE CONTROL Y AL MENOS UNA INTERFAZ DE UN APARATO DE PROCESAMIENTO DE DATOS DE AL MENOS UN APARATO DESCENTRALIZADO DE PROCESAMIENTO DE DATOS, del 16 de Noviembre de 2008, de CONTINENTAL AUTOMOTIVE GMBH: Procedimiento para la transmisión de datos sobre una línea de datos (PDL) entre un aparato central de control (ECU) y al menos una interfaz de un aparato de procesamiento […]