GESTION EFICIENTE DE LA JERARQUIA DE MEMORIAS.

Un procedimiento (500) para hallar una instrucción en una memoria caché de datos que es distinta a una memoria caché de instrucciones,

comprendiendo el procedimiento:

determinar (512) que un intento de extracción de la instrucción falló en la memoria caché de instrucciones, en una dirección de extracción de instrucción; caracterizado por:

determinar (518) que un atributo de comprobación de memoria caché de datos ha sido fijado en un estado activo en una entrada de una tabla de páginas asociada a la dirección de extracción de la instrucción;

seleccionar (520) la dirección de extracción de la instrucción como una dirección de extracción de datos en respuesta a la determinación de que falló un intento de extracción y de que el atributo de comprobación de memoria caché de datos está en el estado activo; y

hacer un intento de extracción en la memoria caché de datos para la instrucción, en la dirección seleccionada de extracción de datos

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2007/060815.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 5775 MOREHOUSE DRIVE,SAN DIEGO, CA 92121.

Inventor/es: SARTORIUS,THOMAS ANDREW, MORROW,MICHAEL WILLIAM.

Fecha de Publicación: .

Fecha Concesión Europea: 5 de Mayo de 2010.

Clasificación Internacional de Patentes:

- G06F9/38F

Clasificación PCT:

- G06F9/38 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Ejecución simultánea de instrucciones, p. ej. segmentación, anticipación.

Fragmento de la descripción:

Gestión eficiente de la jerarquía de memorias.

Campo

La presente revelación se refiere, en general, a técnicas para extraer instrucciones de una memoria que tiene memoria caché para instrucciones y una memoria caché para datos y, más específicamente, a un enfoque mejorado para extraer una instrucción después de un fallo en la memoria caché de instrucciones, extrayendo directamente la instrucción de la memoria caché para datos si la instrucción reside allí.

Antecedentes

Los productos usualmente portátiles, tales como los teléfonos celulares, los ordenadores portátiles, las agendas electrónicas (PDA) o similares, requieren el uso de un procesador que ejecute programas tales como programas de comunicación y multimedios. El sistema de procesamiento para tales productos incluye un complejo de procesador y memoria para almacenar instrucciones y datos. Por ejemplo, las instrucciones y los datos pueden almacenarse en una memoria jerárquica que consiste en niveles múltiples de memorias caché, incluyendo, por ejemplo, una memoria caché para instrucciones, una memoria caché para datos y una memoria del sistema. El uso de una memoria caché separada para instrucciones y una memoria caché separada para datos se conoce como la arquitectura Harvard. Como la arquitectura Harvard aísla la memoria caché de instrucciones de la memoria caché para datos, pueden surgir problemas cuando las instrucciones se almacenan en la memoria caché para datos.

En el procesamiento general de sistemas con una arquitectura Harvard, hay situaciones que surgen, en las cuales las instrucciones pueden almacenarse en la memoria caché para datos. Por ejemplo, si un programa está cifrado o en formato comprimido, debe ser descifrado/descomprimido antes de permitir que el programa se ejecute. El proceso de descifrado/descompresión trata el programa cifrado/comprimido como datos a fin de de procesarlo, y almacena las instrucciones descifradas/descomprimidas como datos en una memoria caché para datos, por ejemplo, una memoria caché para datos de nivel 1, en camino hacia la memoria del sistema. La generación de instrucciones a partir de códigos de octetos Java es otra situación en la cual las instrucciones se tratan inicialmente como datos que se almacenan usando la trayectoria de los datos, incluyendo la memoria caché para datos, hacia la memoria del sistema. El estado inicial de un programa en el cual las instrucciones de programa están tratándose como datos crea un problema de consistencia dentro de la jerarquía de memorias, dado que al menos algunas partes de un programa pueden residir en la memoria caché para datos antes de la ejecución del programa.

A fin de resolver el problema de consistencia, se adopta habitualmente un enfoque de software, en el cual el programa, o segmentos de programa, en la memoria caché para datos se llevan a la memoria del sistema bajo control de programa, la memoria caché para datos se invalida habitualmente para limpiar la memoria caché de segmentos de viejos programas, y las instrucciones que comprenden el programa se extraen luego de la memoria del sistema. El movimiento de las instrucciones desde la memoria caché para datos hasta la memoria del sistema, y la extracción de las instrucciones desde la memoria del sistema antes de la ejecución, pueden ocupar varios ciclos, reduciendo el rendimiento del procesador debido al sobregasto de tiempo de procesamiento que debe tener lugar para acceder a instrucciones que residen inicialmente en la memoria caché para datos antes de que el programa se ejecute en el procesador.

El documento US 2002/010837 describe un sistema y procedimiento de memoria de códigos para controlar la memoria caché.

Resumen

Entre sus diversos aspectos, la presente revelación reconoce que el sobregasto de tratar con instrucciones en una memoria caché para datos puede estar limitando el rendimiento del procesador y, posiblemente, limitando la calidad del servicio que puede lograrse. La presente revelación también reconoce que puede ser deseable acceder a instrucciones que están residentes en una memoria caché para datos.

Además, la presente revelación describe un aparato, procedimientos y un medio legible por ordenador para extraer directamente una instrucción desde una memoria caché para datos cuando esa instrucción no ha sido hallada en la memoria caché para instrucciones, un fallo de la memoria caché para instrucciones, y se determina que la instrucción está en la memoria caché para datos. Extrayendo la instrucción directamente de la memoria caché para datos, después de un fallo de la memoria caché para instrucciones, puede mejorarse el rendimiento del procesador.

Según la invención, se proporciona el procedimiento de la reivindicación 1, la disposición de procesador de la reivindicación 11 y el procedimiento de la reivindicación 15.

Una comprensión más completa de los presentes conceptos inventivos revelados en el presente documento, así como otras características, serán evidentes a partir de la siguiente Descripción Detallada y de los dibujos adjuntos.

Breve descripción de los dibujos

La Fig. 1 es un diagrama en bloques de un sistema ejemplar de comunicación inalámbrica.

La Fig. 2 es un diagrama en bloques funcionales de un complejo de procesador y memoria, en el cual el funcionamiento de la memoria caché para datos está adaptado para operaciones eficientes, en términos de memoria, de extracción de instrucciones;

La Fig. 3 es un diagrama de flujo de un procedimiento ejemplar para extraer una instrucción almacenada en una memoria caché para datos, a fin de reducir el sobregasto de gestión de fallos asociado a la instrucción inicialmente almacenada como datos en la memoria caché para datos;

La Fig. 4 es un diagrama en bloques funcionales de un complejo de procesador y memoria que incluye una tabla de páginas de instrucciones, en el cual el funcionamiento de la memoria caché para datos está adaptado para una eficiente extracción de instrucciones;

La Fig. 5 es un diagrama de flujo de un procedimiento ejemplar para extraer una instrucción almacenada en una memoria caché para datos; y

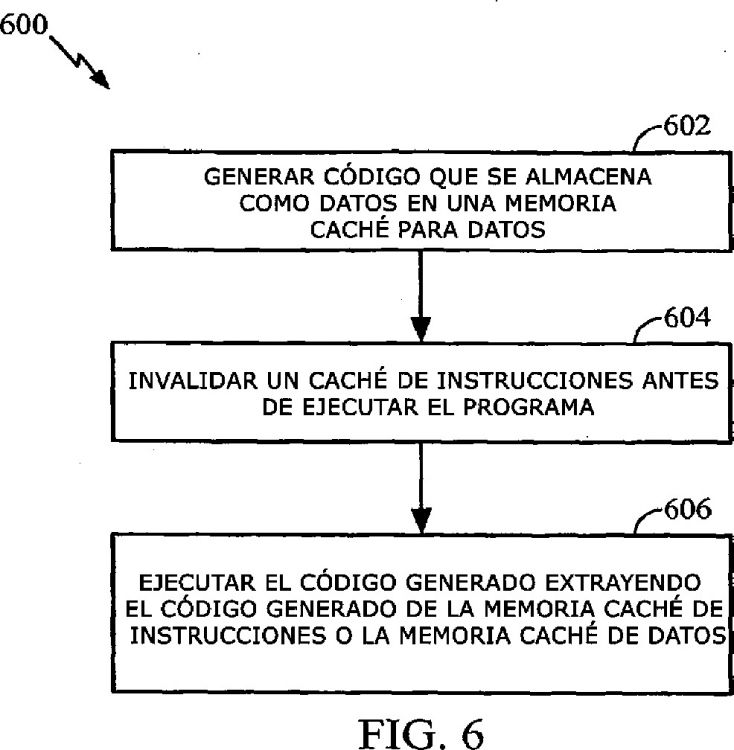

La Fig. 6 es un diagrama de flujo de un procedimiento ejemplar para ejecutar código que se genera como datos y que se almacena en una memoria caché para datos.

Descripción detallada

Aspectos inventivos de la presente revelación se ilustrarán más completamente con referencia a los dibujos adjuntos, en los cuales se muestran varias realizaciones de la revelación. La realización de esta invención, sin embargo, puede realizarse de diversas formas, y no debería interpretarse como limitada a las realizaciones expuestas en el presente documento. Antes bien, estas realizaciones se proporcionan a fin de que esta revelación sea exhaustiva y completa, y que transmita totalmente el alcance de la revelación a aquellos versados en la tecnología.

Se apreciará que la presente revelación puede realizarse como procedimientos, sistemas o productos de programa de ordenador. En consecuencia, los presentes conceptos inventivos revelados en el presente documento pueden tomar la forma de una realización de hardware, una realización de software o una realización que combina aspectos de software y de hardware. Además, los presentes conceptos inventivos revelados en el presente documento pueden tomar la forma de un producto de programa de ordenador en un medio de almacenamiento utilizable por ordenador, con código de programa utilizable por ordenador realizado en el medio. Cualquier medio adecuado legible por ordenador puede utilizarse, incluyendo los discos rígidos, los CD-ROM, los dispositivos ópticos de almacenamiento, las memorias flash o los dispositivos magnéticos de almacenamiento.

El código de programa de ordenador que pueda compilarse, ensamblarse y cargarse en un procesador puede escribirse inicialmente en un lenguaje de programación tal como C, C++, Ensamblador nativo, JAVA®, Smalltalk, JavaScript®, Visual Basic®, TSQL, Perl, o en varios otros lenguajes de programación, de acuerdo a las enseñanzas de la presente revelación. El código de programa, o el medio legible por ordenador, se refiere a código de lenguaje de máquina, tal como el código objeto, cuyo formato es comprensible por un procesador. Las realizaciones de software de la revelación no dependen de su implementación con un lenguaje de programación específico. Cuando se ejecuta el código de programa, se crea una nueva tarea que define el entorno operativo para el código de programa.

La Fig....

Reivindicaciones:

1. Un procedimiento (500) para hallar una instrucción en una memoria caché de datos que es distinta a una memoria caché de instrucciones, comprendiendo el procedimiento:

determinar (512) que un intento de extracción de la instrucción falló en la memoria caché de instrucciones, en una dirección de extracción de instrucción; caracterizado por:

2. El procedimiento de la reivindicación 1, que comprende adicionalmente:

fijar como activa una señal de acierto si la instrucción se halló en la memoria caché de datos en respuesta al intento de extracción en la memoria caché de datos.

3. El procedimiento de la reivindicación 1, que comprende adicionalmente:

fijar como activo un atributo de comprobación de memoria caché de datos en la entrada asociada de la tabla de páginas, al generar instrucciones que se almacenan como datos en la memoria caché de datos.

4. El procedimiento de la reivindicación 3, en el cual el atributo de comprobación de memoria caché de datos es un bit almacenado en una tabla de páginas de instrucciones.

5. El procedimiento de la reivindicación 1, que comprende adicionalmente:

generar, por parte de un programa, datos que se usarán como instrucciones; y solicitar, por parte del programa, que un sistema operativo fije como activo el atributo de comprobación de memoria caché de datos en las entradas de la tabla de páginas asociadas a las instrucciones.

6. El procedimiento de la reivindicación 3, en el cual el atributo de comprobación de memoria caché de datos se desactiva más tarde cuando la entrada de la tabla de páginas se usa para un proceso distinto.

7. El procedimiento de la reivindicación 1, en el cual la etapa de seleccionar la dirección de extracción de instrucción comprende adicionalmente:

multiplexar la dirección de extracción de instrucción y una dirección de extracción de datos; y

seleccionar la dirección de extracción de instrucción para su aplicación a la memoria caché de datos como dirección transformada de extracción de datos, en el que la dirección de extracción de instrucción se selecciona después de determinar que el intento de extracción de instrucción erró en la memoria caché de instrucciones.

8. El procedimiento de la reivindicación 1, en el cual la etapa de hacer un intento de extracción en la memoria caché de datos comprende adicionalmente:

determinar el acierto de la instrucción en la memoria caché de datos; y

extraer la instrucción de la memoria caché de datos.

9. El procedimiento de la reivindicación 1, que comprende adicionalmente:

determinar que el intento de extracción falló en la memoria caché de datos; y

informar a un control de memoria de instrucciones de que el intento de extracción falló en la memoria caché de datos.

10. El procedimiento de la reivindicación 9, que comprende adicionalmente:

extraer la instrucción desde una memoria del sistema.

11. Una disposición de procesador que comprende:

una memoria caché (406) de instrucciones;

una memoria caché (408) de datos; caracterizada por:

12. La disposición procesadora de la reivindicación 11, que comprende adicionalmente:

un segundo selector (438) para seleccionar un bus de salida de instrucciones desde la memoria caché de instrucciones, o un bus de salida de datos desde la memoria caché de datos, a aplicar a una entrada del bus de instrucciones del procesador.

13. La disposición procesadora (400) de la reivindicación 12, en la cual el segundo selector (438) selecciona el bus de salida de datos desde la memoria caché de datos si ocurrió un fallo en la memoria caché (404) de instrucciones y ocurrió un acierto en la memoria caché (408) de datos, en la dirección de extracción de instrucción seleccionada a través del primer selector (432).

14. La disposición procesadora (400) de la reivindicación 12, en la cual el segundo selector (438) selecciona el bus de salida de instrucciones si ocurre un acierto en la memoria caché (404) de instrucciones.

15. Un procedimiento para ejecutar código de programa, que comprende:

generar instrucciones que se almacenan como datos en una memoria caché de datos;

invalidar una memoria caché de instrucciones antes de la ejecución del código de programa que usa las instrucciones generadas; caracterizado por:

Patentes similares o relacionadas:

ALMACENAMIENTO EN MEMORIA CACHÉ EN EL PROCESADO DE DATOS, del 25 de Abril de 2011, de SONY COMPUTER ENTERTAINMENT INC.: Procesador de datos que comprende: una memoria principal ; una memoria caché de instrucciones y una memoria caché de datos dispuestas, cada una […]

ALMACENAMIENTO EN MEMORIA CACHÉ EN EL PROCESADO DE DATOS, del 25 de Abril de 2011, de SONY COMPUTER ENTERTAINMENT INC.: Procesador de datos que comprende: una memoria principal ; una memoria caché de instrucciones y una memoria caché de datos dispuestas, cada una […]

PROCEDIMIENTO Y APARATO DE AHORRO DE ENERGIA PARA INSTRUCCIONES DE LONGITUD VARIABLE, del 30 de Junio de 2010, de QUALCOMM INCORPORATED: Un aparato para ahorrar energía en un entorno de procesador que soporta instrucciones de longitud variable, comprendiendo el aparato:

un predecodificador para […]

PROCEDIMIENTO Y APARATO DE AHORRO DE ENERGIA PARA INSTRUCCIONES DE LONGITUD VARIABLE, del 30 de Junio de 2010, de QUALCOMM INCORPORATED: Un aparato para ahorrar energía en un entorno de procesador que soporta instrucciones de longitud variable, comprendiendo el aparato:

un predecodificador para […]

Control de ejecución de hilos en un procesador multihilo, del 24 de Junio de 2020, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para controlar la ejecución de hilos en un entorno informático, comprendiendo dicho método: detener , mediante un hilo […]

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Predicados uniformes en sombreadores para unidades de procesamiento de gráficos, del 11 de Diciembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para procesar datos, comprendiendo el procedimiento: recibir una indicación de que todos los subprocesos de una urdimbre […]

Aumento de protocolo de coherencia para indicar estado de transacción, del 4 de Diciembre de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método implementado por ordenador para implementar un protocolo de coherencia, comprendiendo el método: enviar , por un procesador (112a) solicitante, […]

Método y aparato para un acceso a memoria basado en hilos en un procesador multihilo, del 11 de Septiembre de 2019, de QUALCOMM INCORPORATED: Método para acceder a una memoria por un procesador multihilo , comprendiendo el método: determinar un identificador de hilo asociado a un […]

Procedimientos y aparatos para predecir la no ejecución de instrucciones de no bifurcación condicional, del 15 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para manejar una instrucción de no bifurcación condicional, que comprende: identificar una instrucción […]