ALMACENAMIENTO EN MEMORIA CACHÉ EN EL PROCESADO DE DATOS.

Procesador de datos que comprende: una memoria principal (130);

una memoria caché (140) de instrucciones y una memoria caché (150) de datos dispuestas, cada una de ellas, como una pluralidad de páginas de memoria caché; una lógica (110) de recuperación de instrucciones que se puede hacer funcionar para buscar en la memoria caché (140) de instrucciones una instrucción requerida; y si la instrucción requerida no está presente en la memoria caché (140) de instrucciones, para buscar en la memoria caché (150) de datos; si la instrucción requerida está presente en la memoria caché de datos para recuperar la página que comprende la instrucción requerida desde la memoria caché de datos hacia la memoria caché de instrucciones, y si la instrucción requerida no está presente en la memoria caché (150) de datos, para recuperar la página que comprende la instrucción requerida desde la memoria principal (130) hacia la memoria caché (140) de instrucciones; una lógica (110) de escritura de datos que se puede hacer funcionar para escribir un valor de datos en la página pertinente de la memoria caché (150) de datos en una dirección de datos y, si la misma página está representada también en la memoria caché (140) de instrucciones, para escribir ese valor de datos en la dirección correspondiente de esa página en la memoria caché (140) de instrucciones; y una lógica (110) de control de memorias caché que se puede hacer funcionar para transferir páginas desde la memoria caché (150) de datos hacia la memoria principal (130), en el que valores de datos almacenados en la memoria caché (140) de instrucciones no se vuelven a escribir nunca en la memoria principal

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/GB2006/001660.

Solicitante: SONY COMPUTER ENTERTAINMENT INC..

Nacionalidad solicitante: Japón.

Dirección: 2-6-21, MINAMI-AOYAMA, MINATO-KU TOKYO 107-0062 JAPON.

Inventor/es: EZRA,RABIN.

Fecha de Publicación: .

Fecha Solicitud PCT: 5 de Mayo de 2006.

Fecha Concesión Europea: 6 de Octubre de 2010.

Clasificación Internacional de Patentes:

- G06F9/38F

- G06F9/38F6

Clasificación PCT:

- G06F9/38 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Ejecución simultánea de instrucciones, p. ej. segmentación, anticipación.

Países PCT: Alemania, España, Francia, Reino Unido, Italia.

PDF original: ES-2357308_T3.pdf

Fragmento de la descripción:

La presente invención se refiere al almacenamiento en memoria caché en el procesado de datos.

A continuación se describirá un problema a título de ejemplo con respecto a la emulación de un microprocesador particular, aunque se observará que la invención presenta una aplicabilidad mucho más amplia.

Los núcleos de microprocesador se usan en varias aplicaciones tales como terminales particulares del televisor 5 y el sistema de entretenimiento informático familiar Playstation 2™ (PS2) de SonyRTM. En el procesador de entrada/salida (IOP) de la PS2, el núcleo está provisto de 2 Megabytes de memoria principal y una memoria caché muy pequeña. Hace uso de la denominada “escritura directa” de la memoria caché, en la que cualquier información escrita por el procesador en una posición de memoria caché se escribe también en la memoria principal subyacente. Esto significa que la información nueva se escribe en la memoria caché en el caso de que sea necesario leerla de nuevo en 10 un futuro próximo, pero la propia operación de escritura no se almacena en memoria caché ya que sigue siendo necesario cada vez un acceso a la memoria principal. Una ventaja de esta disposición es que permite implementar más fácilmente un código de programa automodificable. La técnica anterior es el documento US 2002/0010837, que da a conocer un sistema y un método de memoria caché para controlar esta última.

Se ha propuesto que el IOP se emule mediante un procesador de emulación que tiene una memoria interna 15 demasiado pequeña para proporcionar los 2 MB de la memoria del IOP. Se puede acceder a una memoria externa, aunque esto se realiza únicamente a través de un controlador de DMA. Para permitir que la emulación funcione a una velocidad útil, se requiere por lo tanto una estrategia de almacenamiento en memoria caché, ya que los accesos a una memoria externa en el sistema de emulación que usa el controlador de DMA son lentos. Para reducir el número de accesos a la memoria externa que son necesarios, la estrategia de almacenamiento en memoria caché debería incluir el 20 almacenamiento en memoria caché de escrituras de datos así como de lecturas de datos. No obstante, esto significaría que el código automodificable no se puede emular fácilmente.

La presente invención proporciona un procesador de datos según la reivindicación 1 adjunta a la presente memoria.

La invención proporciona una forma eficaz de acceder a datos e instrucciones al mismo tiempo que se reduce 25 la necesidad de acceder a una memoria principal.

Vista desde un segundo aspecto, la presente invención proporciona un método de procesado de datos según la reivindicación 10 adjunta a la presente memoria.

Otros aspectos de la invención incluyen software de ordenador que comprende un código de programa para llevar a cabo este método; y un soporte (por ejemplo, un medio de transmisión o un soporte de almacenamiento) por 30 medio del cual se proporciona dicho código de programa.

En las reivindicaciones adjuntas se definen otros diversos aspectos y características de la invención. A continuación se describirán formas de realización de la invención, únicamente a título de ejemplo, haciendo referencia a los dibujos adjuntos, en los que:

la Figura 1 ilustra esquemáticamente un sistema de procesado de datos; 35

la Figura 2 ilustra esquemáticamente un sistema de procesado de datos que usa memorias caché de datos y de instrucciones;

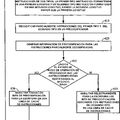

la Figura 3 es un diagrama de flujo esquemático referente a una operación para leer una instrucción;

la Figura 4 es un diagrama de flujo esquemático referente a una operación para escribir un valor de datos; y

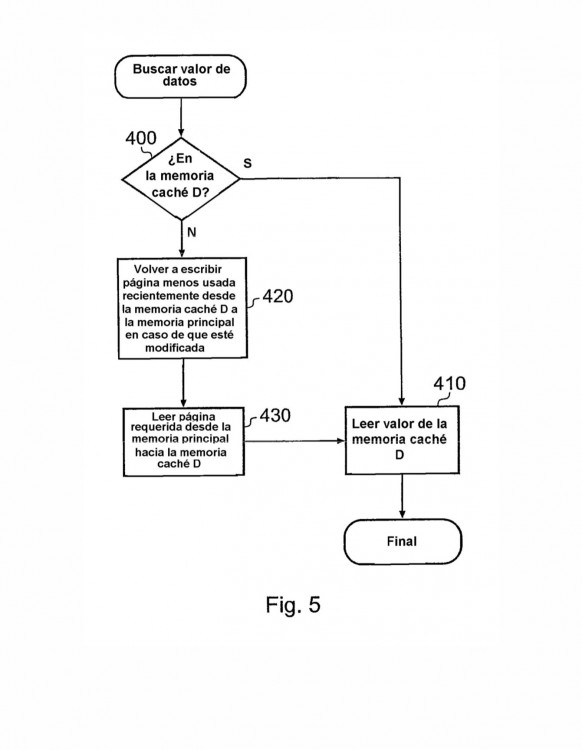

la Figura 5 es un diagrama de flujo esquemático referente a una operación para leer un valor de datos. 40

La Figura 1 ilustra esquemáticamente un sistema de procesado de datos del que se va a realizar una emulación. El sistema comprende un procesador 10 que lee datos e instrucciones desde, y escribe datos e instrucciones modificadas en, una memoria principal 20.

La siguiente descripción se refiere a una técnica para la emulación del funcionamiento del sistema de la Figura 1 que usa un procesador cuya memoria local es demasiado pequeña para contener una imagen de la memoria principal 45 20 del sistema del que se va a realizar la emulación. Debido a esta restricción, se debe utilizar una estrategia de memoria caché.

La Figura 2 ilustra esquemáticamente la disposición de emulación. Las técnicas de emulación son en general bien conocidas, y, por claridad, se omiten las características que no son relevantes directamente para la presente forma de realización. La emulación conlleva un procesador de emulación que ejecuta un software de emulación escrito en un 50 lenguaje nativo para el procesador de emulación, de manera que se ejecuta un grupo de dichas instrucciones nativas para emular el tratamiento de una instrucción en el sistema emulado. En la descripción que se ofrece a continuación, el

término “instrucción” se referirá a una instrucción en el sistema emulado, y no a una instrucción nativa del software de emulación.

Haciendo referencia a la Figura 2, un procesador 110 que ejecuta un software 120 de emulación accede a una memoria principal 130 a través de una memoria caché (I) 140 de instrucciones y una memoria caché (D) 150 de datos. La razón de usar la memoria caché I y la memoria caché D es que la memoria local para el procesador 110 es 5 demasiado pequeña para contener una imagen de la memoria principal 20 del sistema emulado, y se debe acceder a la memoria principal 130 asociada al procesador 110 a través de un acceso DMA caro (es decir, que consume mucho tiempo).

La memoria caché I 140 es de correspondencia directa para obtener más velocidad de acceso y contiene 8 páginas de memoria de 4 kilobytes cada una de ellas (es decir, cada página contiene diversas líneas de memoria 10 caché). En esta forma de realización se usa un número reducido de páginas de memoria de gran tamaño para conseguir que el proceso de comprobación de un acierto de memoria caché resulte más eficaz. Las páginas de memoria de gran tamaño amortizan los accesos lentos a la memoria. Se pueden leer páginas de memoria desde la memoria principal 130 hacia la memoria caché I 140, y el procesador puede leer instrucciones de la memoria caché I 140. No obstante, los valores almacenados en la memoria caché I 140 no se vuelven a escribir nunca en la memoria principal 130. 15

Las transferencias hacia y desde memorias caché se realizan página a página. De modo similar, la búsqueda de una memoria caché, para detectar si la misma contiene un elemento de datos requerido, se lleva a cabo detectando si la página que contiene ese elemento está contenida en la memoria caché.

La memoria caché D 150 es totalmente asociativa para reducir la denominada “hiperpaginación” – es decir, un cambio rápido de las páginas de la memoria caché – y contiene nuevamente 8 páginas de 4 kilobytes cada una de ellas. 20 Cuando se va a leer una página nueva hacia la memoria caché D desde la memoria principal 130, una página a la que se ha accedido menos recientemente, almacenada en la memoria caché D, se vuelve a escribir en la memoria principal (si la misma se ha cambiado desde que se leyó de la memoria principal). Por lo tanto, si el procesado modifica cualquier dato almacenado en la memoria caché D, la modificación queda contenida en la memoria caché D 150 hasta que esa página se vuelva a escribir en la memoria principal 130. 25

A continuación se describirá la interacción de la memoria caché D y la memoria caché I haciendo referencia a diagramas de flujo mostrados en las figuras 3 a 5.

La Figura 3 es un diagrama de flujo esquemático referente a una operación para leer una instrucción.

En una etapa 200, el procesador 110 intenta acceder a la instrucción requerida desde la memoria caché I 140. Si la instrucción requerida está presente en la memoria caché I 140, el control se traslada a una etapa 210 en la que se 30 lee la instrucción desde la memoria caché I y la misma se traslada al procesador 110 para su tratamiento según la manera habitual. A continuación, el proceso finaliza.

No obstante, si la instrucción requerida no estaba en la memoria caché I 140, se realiza a continuación una comprobación en relación con... [Seguir leyendo]

Reivindicaciones:

1. Procesador de datos que comprende:

una memoria principal (130);

una memoria caché (140) de instrucciones y una memoria caché (150) de datos dispuestas, cada una de ellas, como una pluralidad de páginas de memoria caché; 5

una lógica (110) de recuperación de instrucciones que se puede hacer funcionar para buscar en la memoria caché (140) de instrucciones una instrucción requerida; y si la instrucción requerida no está presente en la memoria caché (140) de instrucciones, para buscar en la memoria caché (150) de datos; si la instrucción requerida está presente en la memoria caché de datos para recuperar la página que comprende la instrucción requerida desde la memoria caché de datos hacia la memoria caché de instrucciones, y si la instrucción requerida no está presente en la memoria caché 10 (150) de datos, para recuperar la página que comprende la instrucción requerida desde la memoria principal (130) hacia la memoria caché (140) de instrucciones;

una lógica (110) de escritura de datos que se puede hacer funcionar para escribir un valor de datos en la página pertinente de la memoria caché (150) de datos en una dirección de datos y, si la misma página está representada también en la memoria caché (140) de instrucciones, para escribir ese valor de datos en la dirección 15 correspondiente de esa página en la memoria caché (140) de instrucciones; y

una lógica (110) de control de memorias caché que se puede hacer funcionar para transferir páginas desde la memoria caché (150) de datos hacia la memoria principal (130),

en el que valores de datos almacenados en la memoria caché (140) de instrucciones no se vuelven a escribir nunca en la memoria principal. 20

2. Procesador de datos según la reivindicación 1, en el que la memoria caché de instrucciones es de correspondencia directa y la memoria caché de datos es totalmente asociativa.

3. Procesador de datos según la reivindicación 1 ó 2, en el que transferencias hacia o desde una memoria caché se llevan a cabo basándose en un esquema de página a página.

4. Procesador de datos según la reivindicación 3, en el que la lógica de recuperación de instrucciones se 25 puede hacer funcionar para buscar en la memoria caché de instrucciones y en la memoria caché de datos detectando si una página requerida está contenida en la memoria caché respectiva.

5. Procesador de datos según la reivindicación 3 ó 4, en el que la lógica de control de memorias caché está dispuesta para transferir una página de datos a la que menos se ha accedido recientemente, desde la memoria caché de datos hacia la memoria principal cuando se va a escribir una página recién requerida en la memoria caché de datos y 30 esa página a la que menos se ha accedido recientemente contiene datos que han sido modificados.

6. Procesador de datos según cualquiera de las reivindicaciones anteriores, en el que cada una de las memorias caché contiene 32 kilobytes dispuestos en forma de 8 páginas de 4 kilobytes cada una de ellas.

7. Procesador de datos según cualquiera de las reivindicaciones anteriores, que comprende una lógica de ejecución de instrucciones para ejecutar instrucciones. 35

8. Procesador de datos según la reivindicación 7, en el que la lógica de ejecución de instrucciones comprende una disposición de procesado de datos que ejecutan software para la emulación de la ejecución de las instrucciones.

9. Procesador de datos según cualquiera de las reivindicaciones anteriores, no proporcionando el procesador de datos una función de invalidación de entradas en la memoria caché de instrucciones. 40

10. Método de procesado de datos en un sistema que tiene una memoria principal (130), y una memoria caché (140) de instrucciones y una memoria caché (150) de datos dispuestas, cada una de ellas, como una pluralidad de páginas de memoria caché;

comprendiendo el método las etapas siguientes:

buscar (200) en la memoria caché de instrucciones una instrucción requerida; 45

si la instrucción requerida no está presente en la memoria caché (140) de instrucciones, buscar (220) en la memoria caché (150) de datos; si la instrucción requerida está presente en la memoria caché de datos, recuperar la página que comprende la instrucción requerida desde la memoria caché de datos hacia la memoria caché de instrucciones;

si la instrucción requerida no está presente en la memoria caché de datos, recuperar (240) la página que comprende la instrucción requerida desde la memoria principal (130) hacia la memoria caché (140) de instrucciones;

cuando se va a escribir un valor de datos, escribir (310) ese valor de datos en la página pertinente de la memoria caché (150) de datos en una dirección de datos y, si la misma página está representada también en la memoria caché (140) de instrucciones, escribir (330) ese valor de datos en la dirección correspondiente de esa página 5 en la memoria caché (140) de instrucciones; y

transferir páginas desde la memoria caché (150) de datos hacia la memoria principal (130),

en el que valores de datos almacenados en la memoria caché (140) de instrucciones no se vuelven a escribir nunca en la memoria principal.

11. Software de ordenador que comprende código de programa para llevar a cabo un método según la 10 reivindicación 10.

12. Soporte mediante el cual se proporciona código de programa según la reivindicación 11.

13. Soporte según la reivindicación 12, siendo el soporte un medio de transmisión.

14. Soporte según la reivindicación 13, siendo el soporte un soporte de almacenamiento.

Patentes similares o relacionadas:

GESTION EFICIENTE DE LA JERARQUIA DE MEMORIAS, del 30 de Septiembre de 2010, de QUALCOMM INCORPORATED: Un procedimiento para hallar una instrucción en una memoria caché de datos que es distinta a una memoria caché de instrucciones, comprendiendo […]

GESTION EFICIENTE DE LA JERARQUIA DE MEMORIAS, del 30 de Septiembre de 2010, de QUALCOMM INCORPORATED: Un procedimiento para hallar una instrucción en una memoria caché de datos que es distinta a una memoria caché de instrucciones, comprendiendo […]

PROCEDIMIENTO Y APARATO DE AHORRO DE ENERGIA PARA INSTRUCCIONES DE LONGITUD VARIABLE, del 30 de Junio de 2010, de QUALCOMM INCORPORATED: Un aparato para ahorrar energía en un entorno de procesador que soporta instrucciones de longitud variable, comprendiendo el aparato:

un predecodificador para […]

PROCEDIMIENTO Y APARATO DE AHORRO DE ENERGIA PARA INSTRUCCIONES DE LONGITUD VARIABLE, del 30 de Junio de 2010, de QUALCOMM INCORPORATED: Un aparato para ahorrar energía en un entorno de procesador que soporta instrucciones de longitud variable, comprendiendo el aparato:

un predecodificador para […]

Control de ejecución de hilos en un procesador multihilo, del 24 de Junio de 2020, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para controlar la ejecución de hilos en un entorno informático, comprendiendo dicho método: detener , mediante un hilo […]

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Predicados uniformes en sombreadores para unidades de procesamiento de gráficos, del 11 de Diciembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para procesar datos, comprendiendo el procedimiento: recibir una indicación de que todos los subprocesos de una urdimbre […]

Aumento de protocolo de coherencia para indicar estado de transacción, del 4 de Diciembre de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método implementado por ordenador para implementar un protocolo de coherencia, comprendiendo el método: enviar , por un procesador (112a) solicitante, […]

Método y aparato para un acceso a memoria basado en hilos en un procesador multihilo, del 11 de Septiembre de 2019, de QUALCOMM INCORPORATED: Método para acceder a una memoria por un procesador multihilo , comprendiendo el método: determinar un identificador de hilo asociado a un […]

Procedimientos y aparatos para predecir la no ejecución de instrucciones de no bifurcación condicional, del 15 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para manejar una instrucción de no bifurcación condicional, que comprende: identificar una instrucción […]