PROCEDIMIENTO Y APARATO DE AHORRO DE ENERGIA PARA INSTRUCCIONES DE LONGITUD VARIABLE.

Un aparato para ahorrar energía en un entorno de procesador que soporta instrucciones de longitud variable,

comprendiendo el aparato:

un predecodificador para decodificar parcialmente instrucciones de una primera longitud y una segunda longitud, siendo la segunda longitud mayor que la primera longitud, y generar bits de predecodificación para instrucciones tanto de la primera longitud como de la segunda longitud;

un indicador de estado de modo de operación de procesador, indicando el indicador de estado de modo de operación de procesador que el procesador está operando en un modo que restringe las instrucciones a instrucciones de la segunda longitud;

una caché de instrucciones que tiene una pluralidad de líneas de caché, almacenando una línea de caché instrucciones y bits de predecodificación; y

una lógica de control de escritura para escribir selectivamente bits de predecodificación en una línea de caché dependiendo del indicador de estado de modo de operación de procesador por lo que menos de todos los bits de predecodificación se escriben para instrucciones de la segunda longitud

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2006/007758.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 5775 MOREHOUSE DRIVE,SAN DIEGO, CALIFORNIA 92121.

Inventor/es: STEMPEL,BRIAN MICHAEL, DIEFFENDERFER,JAMES NORRIS, BRIDGES,JEFFREY TODD, SMITH,RODNEY WAYNE, SARTORIUS,THOMAS ANDREW.

Fecha de Publicación: .

Fecha Concesión Europea: 5 de Mayo de 2010.

Clasificación Internacional de Patentes:

- G06F9/30T2

- G06F9/38F

Clasificación PCT:

- G06F9/30 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Disposiciones para ejecutar instrucciones de máquinas, p. ej. decodificación de instrucciones (para ejecutar microinstrucciones G06F 9/22).

Fragmento de la descripción:

Procedimiento y aparato de ahorro de energía para instrucciones de longitud variable.

Antecedentes de la invención

La presente invención se refiere, en general, a técnicas para reducir la energía en un procesador que procesa instrucciones que tienen una diversidad de longitudes, y, más particularmente, a técnicas ventajosas para habilitar y deshabilitar selectivamente la escritura y lectura de bits de predecodificación en una caché de instrucciones.

Muchos procesadores soportan normalmente conjuntos de instrucciones que tienen instrucciones de longitud variable. Por ejemplo, el conjunto de instrucciones de un procesador puede estar constituido por instrucciones de 32 bits e instrucciones de 16 bits. Un procesador también puede tener una configuración de memoria jerárquica con múltiples niveles de cachés incluyendo una caché de instrucciones, una caché de datos y memoria de sistema. Si el procesador también tiene un cauce de ejecución profundo que opera a una tasa de reloj elevada con fases de encauzado de corta duración, también es probable que el procesador tenga una fase de predecodificación para preprocesar la instrucciones para simplificar una fase de decodificación posterior y, por tanto, simplificar el encauzado. La fase de encauzado de predecodificación es comúnmente operativa durante un fallo de caché de instrucciones para decodificar parcialmente instrucciones que se extraen debido al fallo de instrucción. La información de predecodificación se escribe en la caché de instrucciones junto con las instrucciones extraídas.

En un procesador de instrucciones de longitud variable, las instrucciones extraídas debido a un fallo pueden ser de longitud variable. La operación de predecodificación determina un conjunto de bits de predecodificación para cada instrucción y los bits de predecodificación e instrucción se almacenan en la caché de instrucciones independientemente del estado de operación del procesador. La escritura y lectura de bits de predecodificación que puede ser innecesaria debido al estado de operación del procesador es una fuente de pérdida de energía.

Se dirige la atención adicionalmente al documento US-A-6 141 745, que describe un microprocesador superescalar que incluye una unidad de predecodificación adaptada para predecodificar instrucciones de longitud de bytes variable. La unidad de predecodificación predecodifica las instrucciones antes de su almacenamiento en una caché de instrucciones. En un sistema, una unidad de predecodificación está configurada para generar una pluralidad de bits de predecodificación incluyendo un bit inicial, un bit final y un bit funcional para cada byte de instrucción. La pluralidad de bits de predecodificación asociados con cada byte de instrucción se denomina en conjunto etiqueta de predecodificación. Entonces una unidad de alineación de instrucciones usa las etiquetas de predecodificación para enviar las instrucciones de longitud de bytes variable a una pluralidad de unidades de decodificación en el microprocesador superescalar. La unidad de predecodificación está configurada de tal modo que el significado del bit funcional de una etiqueta de predecodificación particular depende del estado del bit final. La unidad de predecodificación está configurada además para generar bits funcionales asociados con bytes de una instrucción diferentes del byte de finalización, que indican si los bytes de la instrucción diferentes del byte de finalización son un prefijo. La codificación de las etiquetas de predecodificación es tal que una cantidad relativamente grande de información de predecodificación puede transportarse con un número relativamente pequeño de bits de predecodificación.

Sumario de la divulgación

Según la presente invención, se proporcionan un aparato para ahorrar energía en un entorno de procesador, tal como se expone en la reivindicación 1, un aparato para ahorrar energía cuando se lee una línea de caché de instrucciones, tal como se expone en la reivindicación 11, y un procedimiento, tal como se expone en la reivindicación 16. Realizaciones de la invención se reivindican en las reivindicaciones dependientes.

Entre sus diversos aspectos, la presente invención reconoce que la energía puede conservarse habilitando selectivamente la escritura y lectura de bits de predecodificación. Una primera realización de la invención reconoce que existe la necesidad de una técnica que extraiga y ejecute instrucciones de longitud variable de una primera longitud y de una segunda longitud, siendo la segunda longitud mayor que la primera longitud. Un indicador de estado de modo de operación de procesador indica que el procesador está en un modo de operación que restringe las instrucciones a instrucciones de la segunda longitud. Un predecodificador decodifica parcialmente instrucciones de la primera longitud y la segunda longitud y genera bits de predecodificación para cada instrucción parcialmente decodificada. Las instrucciones y los bits de predecodificación se almacenan en una línea de caché en una caché de instrucciones. Una lógica de control de escritura escribe selectivamente bits de predecodificación en una línea de caché dependiendo del indicador de estado de modo de operación de procesador por lo que menos de todos los bits de predecodificación se escriben para instrucciones de la segunda longitud. Una etiqueta asociada con la línea de caché se escribe con una dirección de instrucción y un bit de estado de procesador. Cuando se lee, una dirección de instrucción de extracción y un indicador de modo de operación de procesador se comparan con la etiqueta y si la comparación es igual los bits de predecodificación seleccionados se leen a partir de la línea de caché por lo que menos de todos los bits de predecodificación disponibles en la línea de caché se leen para instrucciones de la segunda longitud.

Una comprensión más completa de la presente invención, así como las características y ventajas adicionales de la invención, será evidente a partir de la siguiente descripción detallada y los dibujos adjuntos.

Breve descripción de los dibujos

La figura 1 es una ilustración gráfica de un sistema de comunicación inalámbrica ejemplar en el que puede emplearse ventajosamente una realización de la invención;

la figura 2 es una ilustración gráfica de un complejo de procesador según la presente invención;

la figura 3A es una ilustración gráfica de un segmento de programa ejemplar que contiene instrucciones de longitud variable de 16 y 32 bits según la presente invención;

la figura 3B es una ilustración gráfica de una línea de instrucciones desde una caché de datos e instrucciones de nivel 2 (caché de L2) que contiene instrucciones desde el segmento de programa de la figura 3A según la presente invención;

la figura 3C es una ilustración gráfica de una línea de instrucciones desde una caché de instrucciones de nivel 1 (Icaché de L1) que contiene instrucciones desde el segmento de programa de la figura 3A según la presente invención;

la figura 4A es una ilustración gráfica de un segmento de programa ejemplar que sólo contiene instrucciones de 32 bits operativas en un modo de procesador restringido a sólo instrucciones de 32 bits según la presente invención;

la figura 4B es una ilustración gráfica de una línea de instrucciones desde una caché de L2 que contiene instrucciones desde el segmento de programa de la figura 4A según la presente invención;

la figura 4C es una ilustración gráfica de una línea de instrucciones desde una Icaché de L1 que contiene instrucciones desde el segmento de programa de la figura 4A según la presente invención;

la figura 5 es una ilustración gráfica de fases de encauzado de procesador que operan según la presente invención para ahorrar energía cuando se escribe en la Icaché de L1 y se lee desde la Icaché de L1; y

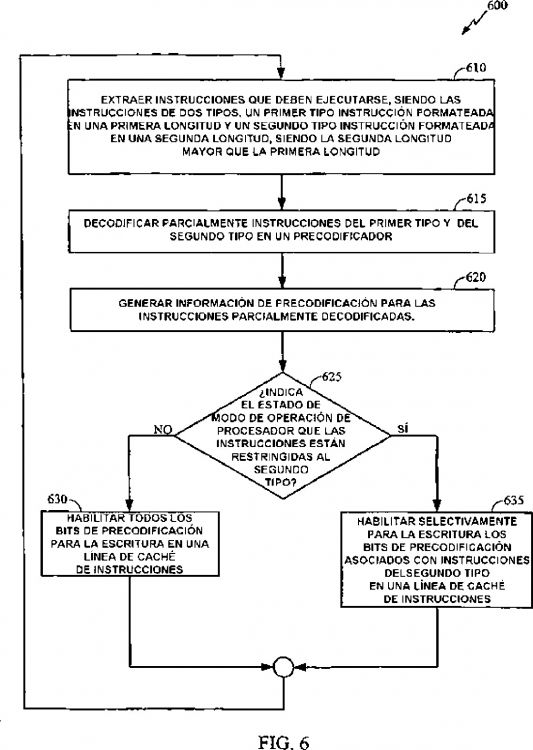

la figura 6 es un diagrama de flujo de etapas operacionales requeridas para ahorrar energía cuando se escribe y lee información de predecodificación desde una línea de caché de instrucciones según la presente invención.

Descripción detallada

Ahora se describirá la presente invención de manera más completa con referencia a los dibujos adjuntos, en los que se muestran diversas realizaciones de la invención. Sin embargo, esta invención puede implementarse de diversas formas y no debe interpretarse como limitada a las realizaciones expuestas...

Reivindicaciones:

1. Un aparato para ahorrar energía en un entorno de procesador que soporta instrucciones de longitud variable, comprendiendo el aparato:

2. El aparato según la reivindicación 1, en el que la línea de caché de instrucciones está dividida en secciones para instrucciones y secciones para bits de predecodificación, y menos de todas las secciones de predecodificación se escriben para instrucciones de la segunda longitud.

3. El aparato según la reivindicación 2, en el que las secciones para instrucciones son campos de 16 bits y las secciones para bits de predecodificación son campos de cuatro bits.

4. El aparato según la reivindicación 2, en el que las secciones para instrucciones son campos de 8 bits y las secciones para bits de predecodificación son campos de dos bits.

5. El aparato según la reivindicación 1, en el que la pluralidad de líneas de caché se almacenan en una primera memoria y la caché de instrucciones comprende además:

6. El aparato según la reivindicación 1, en el que la primera longitud es 16 bits y la segunda longitud es 32 bits, y en el que cada instrucción de primera longitud tiene cuatro bits de predecodificación y cada instrucción de segunda longitud tiene grupos primero y segundo de cuatro bits de predecodificación, y el segundo grupo de bits de predecodificación para la instrucción de segunda longitud no está escrito.

7. El aparato según la reivindicación 1, en el que el campo de bit de predecodificación clasifica instrucciones en categorías de instrucciones funcional y de control.

8. El aparato según la reivindicación 2, en el que la lógica de control de escritura escribe una instrucción de segunda longitud en múltiples secciones de instrucciones de la línea de caché y escribe una sección de predecodificación asociada con una de las secciones de instrucciones que está ocupada por una parte de la instrucción de segunda longitud, no siendo válidas ni escribiéndose las demás secciones de predecodificación asociadas con secciones de instrucciones que están ocupadas por otras partes de la instrucción de segunda longitud.

9. El aparato según la reivindicación 1, en el que el indicador de estado de modo de operación de procesador indica además que el procesador está operando en un modo que restringe las instrucciones a instrucciones de una tercera longitud mayor que la segunda longitud, y el predecodificador opera además para decodificar instrucciones de la tercera longitud.

10. El aparato según la reivindicación 1, en el que la caché de instrucciones comprende además:

11. Un aparato para ahorrar energía cuando se lee una línea de caché de instrucciones, comprendiendo el aparato:

12. El aparato según la reivindicación 11 que comprende además:

13. El aparato según la reivindicación 11, en el que los campos de bits de predecodificación seleccionados clasifican instrucciones de tal modo que las instrucciones leídas a partir de la línea de caché pueden alinearse y decodificarse.

14. El aparato según la reivindicación 11, en el que las operaciones de extracción de procesador incluyen suministrar una dirección de instrucción y el indicador de estado de modo de operación de procesador.

15. El aparato según la reivindicación 11, en el que la caché de instrucciones comprende:

16. Un procedimiento que comprende:

17. El procedimiento según la reivindicación 16, en el que la línea de caché de instrucciones se divide en campos de instrucciones y campos de bits de predecodificación, y en la etapa de escribir bits de predecodificación seleccionados, menos de todos los campos de predecodificación se escriben para instrucciones de la segunda longitud.

18. El procedimiento según la reivindicación 16, en el que en la etapa de escribir bits de predecodificación seleccionados en una línea de caché de instrucciones comprende además:

19. El procedimiento según la reivindicación 16, que comprende además:

20. El procedimiento según la reivindicación 19, que comprende además:

Patentes similares o relacionadas:

ALMACENAMIENTO EN MEMORIA CACHÉ EN EL PROCESADO DE DATOS, del 25 de Abril de 2011, de SONY COMPUTER ENTERTAINMENT INC.: Procesador de datos que comprende: una memoria principal ; una memoria caché de instrucciones y una memoria caché de datos dispuestas, cada una […]

ALMACENAMIENTO EN MEMORIA CACHÉ EN EL PROCESADO DE DATOS, del 25 de Abril de 2011, de SONY COMPUTER ENTERTAINMENT INC.: Procesador de datos que comprende: una memoria principal ; una memoria caché de instrucciones y una memoria caché de datos dispuestas, cada una […]

GESTION EFICIENTE DE LA JERARQUIA DE MEMORIAS, del 30 de Septiembre de 2010, de QUALCOMM INCORPORATED: Un procedimiento para hallar una instrucción en una memoria caché de datos que es distinta a una memoria caché de instrucciones, comprendiendo […]

GESTION EFICIENTE DE LA JERARQUIA DE MEMORIAS, del 30 de Septiembre de 2010, de QUALCOMM INCORPORATED: Un procedimiento para hallar una instrucción en una memoria caché de datos que es distinta a una memoria caché de instrucciones, comprendiendo […]

Método y equipo para realizar una reorganización de bits de un vector, del 29 de Julio de 2020, de INTEL CORPORATION: Un procesador que comprende:

un decodificador para decodificar una instrucción de reorganización de bits de un vector, comprendiendo […]

Método y equipo para realizar una reorganización de bits de un vector, del 29 de Julio de 2020, de INTEL CORPORATION: Un procesador que comprende:

un decodificador para decodificar una instrucción de reorganización de bits de un vector, comprendiendo […]

Control de ejecución de hilos en un procesador multihilo, del 24 de Junio de 2020, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para controlar la ejecución de hilos en un entorno informático, comprendiendo dicho método: detener , mediante un hilo […]

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Operaciones SIMD de anchura mixta que tienen operaciones de elementos pares y de elementos impares usando un par de registros para elementos de datos anchos, del 25 de Marzo de 2020, de QUALCOMM INCORPORATED: Un procedimiento para realizar una operación de tipo "una instrucción, múltiples datos" (SIMD) de anchura mixta, comprendiendo el procedimiento: recibir , […]

Transformar especificadores de instrucción no contiguos a especificadores de instrucción contiguos, del 19 de Febrero de 2020, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un producto de programa informático para emular instrucciones en un entorno informático, comprendiendo el producto de programa informático: un medio de almacenamiento […]

Predicados uniformes en sombreadores para unidades de procesamiento de gráficos, del 11 de Diciembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para procesar datos, comprendiendo el procedimiento: recibir una indicación de que todos los subprocesos de una urdimbre […]