DISPOSITIVO DE CONTROL PARA UN ORDENADOR, USO DE UN DISPOSITIVO DE CONTROL, ORDENADOR QUE COMPRENDE UN DISPOSITIVO DE CONTROL, Y METODO PARA CONECTAR Y DESCONECTAR UNIDADES EN UN ORDENADOR.

Un dispositivo de control (1) para su uso con un ordenador (2),

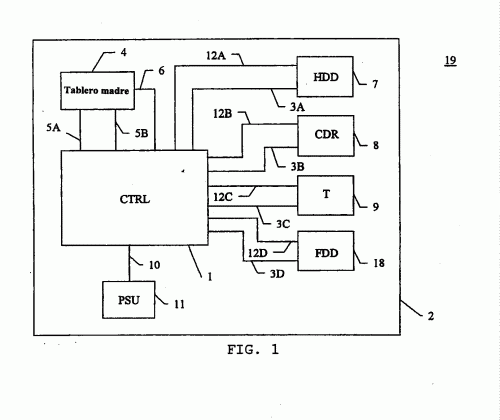

teniendo el ordenador un tablero madre (4) y una o más unidades (7, 8, 9, 18), y una unidad de alimentación de corriente (11) para suministrar corriente eléctrica al tablero madre y a la una o más unidades, e interconexiones eléctricas (3A, 3B, 3C, 3D, 6, 5A, 5B, 12A, 12B, 12C, 12D, 10) para interconectar el tablero madre, la una o más unidades y la unidad de alimentación de corriente, pudiendo funcionar el ordenador en al menos un primer estado, en el que un primer grupo de la una o más unidades es operable, y en un segundo estado, en el que un segundo grupo de la una o más unidades es operable, estando destinado el dispositivo de control, dependiendo del estado en que el ordenador tenga que funcionar, a establecer las seleccionadas de las interconexiones eléctricas a fin de hacer operables unidades correspondientes, y a interrumpir las seleccionadas de las interconexiones eléctricas a fin de hacer inoperables unidades correspondientes, caracterizado porque el dispositivo de control comprende un dispositivo de entrada (20, 21), por medio del cual pueden ser suministrados uno o más códigos al dispositivo de control, y medios (24) que especifican una relación entre los códigos y los estados, y que está destinado, sobre la base de códigos recibidos a través del dispositivo de entrada y de la relación entre códigos y los estados, a seleccionar un estado en el que el ordenador tiene que funcionar y a establecer las interconexiones eléctricas con el grupo de unidades para que sean operables en el estado seleccionado, y a continuación de esto, y antes de que el ordenador sea configurado, establecer la interconexión eléctrica (6) entre la unidad de alimentación de corriente y el tablero madre.

Tipo: Resumen de patente/invención.

Solicitante: REMEDAN APS.

Nacionalidad solicitante: Dinamarca.

Dirección: GYDEVANG 39-41,3450 ALLER D.

Inventor/es: NORTUNG, RENE.

Fecha de Publicación: .

Fecha Solicitud PCT: 7 de Enero de 2000.

Fecha Concesión Europea: 26 de Noviembre de 2003.

Clasificación Internacional de Patentes:

- G06F1/00 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › Detalles no cubiertos en los grupos G06F 3/00 - G06F 13/00 y G06F 21/00 (arquitecturas de computadores con programas almacenados de propósito general G06F 15/76).

- G06F12/14 G06F […] › G06F 12/00 Acceso, direccionamiento o asignación en sistemas o arquitecturas de memoria (entrada digital a partir de, o salida digital hacia soportes de registro, p. ej. hacia unidades de almacenamiento de disco G06F 3/06). › Protección contra la utilización no autorizada de la memoria.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Oficina Europea de Patentes, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania, Armenia, Azerbayán, Bielorusia, Ghana, Gambia, Kenya, Kirguistán, Kazajstán, Lesotho, República del Moldova, Malawi, Federación de Rusia, Sudán, Sierra Leona, Tayikistán, Turkmenistán, República Unida de Tanzania, Uganda, Zimbabwe, Burkina Faso, Benin, República Centroafricana, Congo, Costa de Marfil, Camerún, Gabón, Guinea, Malí, Mauritania, Niger, Senegal, Chad, Togo, Organización Regional Africana de la Propiedad Industrial, Swazilandia, Guinea-Bissau, Organización Africana de la Propiedad Intelectual, Organización Eurasiática de Patentes.

Patentes similares o relacionadas:

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Procedimiento de control sistemático de direcciones de zonas de memoria en el marco de una transferencia por acceso directo, del 1 de Abril de 2020, de THALES: Procedimiento de control sistemático por un dispositivo de control de al menos un mensaje de configuración de transferencia, siendo el mensaje de configuración […]

Servidor de seguridad de soporte lógico, del 19 de Febrero de 2020, de Idemia Identity & Security France: Procedimiento de verificación de ejecución de applets (AA1, AB1) desarrolladas en un lenguaje orientado objeto y compiladas en código intermedio, siendo el procedimiento […]

Múltiples conjuntos de campos de atributos dentro de una única entrada de tabla de páginas, del 25 de Septiembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento que comprende: traducir , por una primera unidad de procesamiento , una dirección de memoria virtual a una […]

Procedimiento para proteger datos relevantes para la seguridad en una memoria caché, del 14 de Agosto de 2019, de SIEMENS AKTIENGESELLSCHAFT: Procedimiento para proteger datos relevantes para la seguridad en una memoria caché, archivándose una copia de los datos relevantes para la seguridad […]

Archivo seguro, del 7 de Agosto de 2019, de Waterfall Security Solutions Ltd: Aparato de almacenamiento, que comprende: una memoria ; un procesador de encriptado , que está configurado para recibir y encriptar datos transmitidos desde uno […]

Sistemas y métodos para proporcionar como salida un resultado de una instrucción de procesador vigente tras su salida de una máquina virtual, del 3 de Abril de 2019, de Bitdefender IPR Management Ltd: Un sistema anfitrión que comprende al menos un procesador hardware configurado para ejecutar una máquina virtual y un programa de seguridad informática, en donde el al menos […]

Sistema y método para la gestión distribuida de ordenadores compartidos, del 20 de Febrero de 2019, de Zhigu Holdings Limited: Método para operar una arquitectura de gestión informática de múltiples niveles, teniendo dicho método los siguientes pasos: operar un ordenador […]