UN CONMUTADOR SEMICONDUCTOR DE ALTA TENSION.

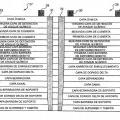

CONMUTADOR SEMICONDUCTOR DE ALTA TENSION. CONSTA DE UNA REGION SEMICONDUCTORA TIPO N QUE PROPORCIONA UN DRENAJE A UN TRANSISTOR MOS Y UNA BASE PARA UN TRANSISTOR PNP,

TENIENDO DICHOS TRANSISTORES MOS Y PNP LA MISMA CORRIENTE DE BASE Y DRENAJE; DE UNA PRIMERA REGION SEMICONDUCTORA TIPO P DISPUESTA EN DICHA REGION N, QUE PROPORCIONA UN COLECTOR Y UN EMISOR PARA DICHO TRANSISTOR PNP; DE UNA SEGUNDA REGION SEMICONDUCTORA TIPO P DISPUESTA EN LA CITADA REGION N, QUE PROPORCIONA EL OTRO COLECTOR Y EMISOR PARA EL TRANSISTOR PNP; DE UNA REGION SEMICONDUCTORA TIPO P DISPUESTA EN LA REGION N, QUE PROPORCIONA UNA PUERTA AL TRANSISTOR MOS; Y DE UNA REGION SEMICONDUCTORA TIPO N DISPUESTA EN LA REGION P, QUE PROPORCIONA UNA FUENTE PARA EL TRANSISTOR MOS.

Tipo: Resumen de patente/invención.

Solicitante: STANDARD ELECTRICA, S.A..

Nacionalidad solicitante: España.

Provincia: MADRID.

Fecha de Solicitud: 24 de Agosto de 1981.

Fecha de Publicación: .

Fecha de Concesión: 14 de Septiembre de 1982.

Clasificación Internacional de Patentes:

- H01L27/06 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 27/00 Dispositivos que consisten en una pluralidad de componentes semiconductores o de otros componentes de estado sólido formados en o sobre un sustrato común (detalles H01L 23/00, H01L 29/00 - H01L 51/00; conjuntos que consisten en una pluralidad de dispositivos de estado sólido individuales H01L 25/00). › con una pluralidad de componentes individuales en una configuración no repetitiva.

Patentes similares o relacionadas:

Sistemas en paquetes, del 19 de Febrero de 2020, de QUALCOMM INCORPORATED: Un sistema en paquete que comprende: un portador ; un primer chip encima de dicho portador , en el que dicho primer chip […]

Dispositivo de PHEMT de enriquecimiento/empobrecimiento y método de fabricación del mismo, del 23 de Julio de 2014, de SELEX ES S.p.A: Estructura epitaxial estratificada para dispositivos (1; 1') de PHEMT de enriquecimiento y empobrecimiento, que comprende:

* una capa de […]

Dispositivo de PHEMT de enriquecimiento/empobrecimiento y método de fabricación del mismo, del 23 de Julio de 2014, de SELEX ES S.p.A: Estructura epitaxial estratificada para dispositivos (1; 1') de PHEMT de enriquecimiento y empobrecimiento, que comprende:

* una capa de […]

CMOS DE CARBURO DE SILICIO Y METODO DE FABRICACION., del 1 de Septiembre de 2004, de CREE RESEARCH, INC.: DISPOSITIVO MONOBLOQUE DE CMOS INTEGRADO, FORMADO EN CARBURO DE SILICIO Y METODO PARA LA FABRICACION DEL MISMO. EL INSTRUMENTO DE CMOS INTEGRADO INCLUYE UNA CAPA DE […]

CIRCUITO LIMITADOR DE POTENCIA-TENSION., del 16 de Noviembre de 1997, de TEMIC TELEFUNKEN MICROELECTRONIC GMBH: SE DESCRIBE UN CIRCUITO TRANSISTORIZADO DE POTENCIA PARA LOGRAR UNA TENSION LIMITADORA, CON: ENTRE LA BASE Y EL EMISOR DEL TRANSISTOR DE POTENCIA; […]

ESTRUCTURA Y CIRCUITO DE PROTECCION QUE COMPRENDE UN RECTIFICADOR DE SILICIO MANDADO CON TENSION DE DISPARO REDUCIDA., del 16 de Octubre de 1997, de SARNOFF CORPORATION SHARP CORPORATION: SE PRESENTA UN DISPOSITIVO DE VOLTAJE DE BAJA RUPTURA PARA PROTEGER UN CIRCUITO INTEGRADO DE UNA ENERGIA TRANSITORIA. ESTE DISPOSITIVO […]

PROCEDIMIENTO PARA LA PRODUCCION DE DISPOSITIVOS TRANSISTORES EN AREAS SELECCIONADAS DE UNA LAMINA SEMICONDUCTORA, del 16 de Enero de 1989, de AMERICAN TELEPHONE AND TELEGRAPH CO.: UN PROCEDIMIENTO PARA FABRICAR TRANSISTORES BIPOLARES Y CMOS SOBRE UN SUSTRATO DE SILICIO DEL TIPO P-. EL SUSTRATO DE SILICIO TIENE LOS POZOS ENTERRADOS […]

DISPOSITIVOS Y CIRCUITOS NANOELECTRICOS, del 16 de Diciembre de 2007, de BTG INTERNATIONAL LIMITED: Componente de circuito electrónico, que comprende un sustrato que soporta portadores de carga móviles, medios […]

DISPOSITIVOS Y CIRCUITOS NANOELECTRICOS, del 16 de Diciembre de 2007, de BTG INTERNATIONAL LIMITED: Componente de circuito electrónico, que comprende un sustrato que soporta portadores de carga móviles, medios […]

CONDENSADOR APILADO Y METODO DE FABRICACION DEL CONDENSADOR APILADO, del 1 de Octubre de 2007, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un condensador Poli-Poli/MOS apilado comprende: un sustrato semiconductor que tiene una región de un primer tipo de conductividad presente en una superficie del mismo; […]

CONDENSADOR APILADO Y METODO DE FABRICACION DEL CONDENSADOR APILADO, del 1 de Octubre de 2007, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un condensador Poli-Poli/MOS apilado comprende: un sustrato semiconductor que tiene una región de un primer tipo de conductividad presente en una superficie del mismo; […]