PROCEDIMIENTO CORRECTOR PARA UN MICRO-PROCESADOR REPROGRAMABLE.

Procedimiento corrector para un micro-procesador reprogramable según la invención prevé los siguientes pasos:

aprontamiento del micro-procesador con una memoria semiconductora reprogramable no volátil; archivado de al menos una rutina aplicativa en la memoria semiconductora reprogramable no volátil; aprontamiento de un código corrector para al menos una rutina aplicativa; aprontamiento de un código de comprobación para al menos una rutina aplicativa; comprobación de la integridad de al menos una rutina aplicativa archivada mediante el código de comprobación; ejecución de una corrección mediante el código corrector, cuando falta la integridad de la rutina aplicativa, en donde la corrección se realiza en la memoria semiconductora reprogramable no volátil; comprobación de la integridad de la rutina aplicativa corregida mediante el código de comprobación; y adopción de una corrección exitosa, cuando se confirma la integridad de la rutina aplicativa corregida

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P200702347.

Solicitante: ROBERT BOSCH GMBH.

Nacionalidad solicitante: Alemania.

Dirección: WERNERSTRASSE,STUTTGART 70469.

Inventor/es: FISLAGE,MARKUS.

Fecha de Solicitud: 29 de Agosto de 2007.

Fecha de Publicación: .

Fecha de Concesión: 22 de Octubre de 2010.

Clasificación PCT:

- G06F11/08 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › Detección o corrección de errores por introducción de redundancia en la representación de los datos, p. ej. utilizando códigos de control.

- G11C29/52 G […] › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 29/00 Verificación del funcionamiento correcto de memorias; Ensayo de memorias durante su funcionamiento fuera de línea (offline")o en espera ("standby"). › Protección de los contenidos de la memoria; Detección de errores en los contenidos de la memoria.

Fragmento de la descripción:

Procedimiento corrector para un micro-procesador reprogramable.

La presente invención se refiere a un procedimiento corrector para un micro-procesador reprogramable y a un micro-procesador reprogramable para llevar a cabo el procedimiento corrector.

Múltiples aparatos de control utilizan un micro-procesador, que ejecuta rutinas aplicativas predeterminadas de forma fija. Estas rutinas aplicativas se almacenan normalmente en el micro-procesador. El microprocesador presenta para esto una región de memoria que puede regrabarse una o varias veces. El micro-procesador carga las diferentes inducciones directamente desde la región de memoria en su registro de ejecución. La región de memoria se materializa normalmente como EEPROM. Mediante aparatos de programación externos pueden archivarse nuevas rutinas aplicativas en bloques en la EEPROM.

En las memorias regrabables pueden modificarse aisladamente diferentes bits a causa de influencias perturbadoras. Estos errores de bits aislados pueden conducir después a que las rutinas de control no se ejecuten o lo hagan de forma defectuosa. En aparatos de control especialmente importantes para la seguridad, como por ejemplo para un sistema de airbag, no es tolerable un comportamiento defectuoso de este tipo. En el caso de aparatos de control de este tipo se comprueba por ello si las rutinas de control y sus datos correspondientes están archivados sin errores, antes de que se ejecuten. Si no es este el caso se bloquea el aparato de control.

Manifiesto de la invención

El procedimiento conforme a la invención con las particularidades de la reivindicación 1 crea ventajosamente una corrección de rutinas aplicativas archivadas, antes de que se ejecuten.

El procedimiento corrector para un micro-procesador reprogramable prevé los pasos siguientes:

- (a) aprontamiento del micro-procesador con una memoria semiconductora reprogramable no volátil;

- (b) archivado de al menos una rutina aplicativa en la memoria semiconductora reprogramable no volátil;

- (c) aprontamiento de un código corrector para al menos una rutina aplicativa;

- (d) aprontamiento de un código de comprobación para al menos una rutina aplicativa;

- (e) comprobación de la integridad de al menos una rutina aplicativa archivada mediante el código de comprobación;

- (f) ejecución de una corrección mediante el código corrector, cuando falta la integridad de la rutina aplicativa, en donde la corrección se realiza en la memoria semiconductora reprogramable no volátil;

- (g) comprobación de la integridad de la rutina aplicativa corregida mediante el código de comprobación; y

- (h) adopción de una corrección exitosa, cuando se confirma la integridad de la rutina aplicativa corregida.

Una medida del procedimiento conforme a la invención consiste en corregir una rutina aplicativa del micro-procesador reprogramable, en el caso de que se reconozca como defectuosa. Por un lado se consigue una elevada seguridad con relación a la integridad de la rutina aplicativa, por medio de que se utilizan diferentes procedimientos para la comprobación y la corrección de la rutina aplicativa.

La complejidad para un micro-procesador o un dispositivo de tratamiento de datos de un aparato de control se mantiene reducida, por medio de que una corrección sólo se produce si previamente se ha determinado una falta de integridad. Aparte de esto la corrección se produce en la memoria regrabable no volátil. Si se carga la rutina aplicativa una próxima vez, presenta de nuevo una integridad y por ello no precisa una nueva corrección.

La comprobación y la corrección se producen sin componentes externos. Por medio de esto puede realizarse también una corrección durante el funcionamiento.

El micro-procesador puede cargar instrucciones de las rutinas aplicativas, en cada caso directamente desde la memoria semiconductora reprogramable no volátil, para su ejecución.

Durante la corrección se regraba un bloque de la memoria semiconductora reprogramable no volátil, que presenta la rutina aplicativa correctora.

Una rutina correctora para ejecutar la corrección se archiva en un bloque propio. Por medio de esto se garantiza que, en el caso de una corrección, no se grabe por descuido encima de la rutina correctora. Con preferencia no es posible una modificación del bloque con la rutina correctora.

La comprobación de la integridad puede realizarse cada vez, antes de que se ejecute la rutina aplicativa.

Una rutina correctora para ejecutar la corrección puede ser ella misma una rutina aplicativa. Una corrección se considera ventajosamente no exitosa, si la rutina correctora archivada no presenta una integridad.

La memoria reprogramable no volátil puede ser una memoria flash.

El aprontamiento de la rutina aplicativa puede realizarse mediante una rutina de carga, que archive la rutina aplicativa en la memoria reprogramable no volátil. La rutina de carga comprueba convenientemente la integridad de la rutina aplicativa archivada, directamente después del archivado, por medio del código de comprobación. Además de esto la propia rutina de carga puede ser una rutina aplicativa. La carga posterior o la modificación de rutinas aplicativas se lleva a cabo en este caso mediante la rutina de carga. De este modo no es necesario un aprontamiento externo de esta rutina de carga. Al mismo tiempo puede modificarse la propia rutina de carga.

El código corrector puede ser un código Reed-Solomon.

Breve descripción de los dibujos

La figura 1 muestra una forma de ejecución del dispositivo para llevar a cabo un procedimiento corrector;

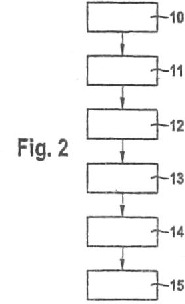

la figura 2 muestra un diagrama de flujo de una forma de ejecución del procedimiento corrector conforme a la invención;

la figura 3 muestra un diagrama de flujo una aplicación de la forma de ejecución de la figura 2; y

la figura 4 muestra una segunda aplicación de la forma de ejecución de la figura 2.

Descripción de las formas de ejecución

En la figura 1 se muestra un diagrama en bloques de un aparato de control 1, que puede ejecutar un procedimiento corrector. El aparato de control 1 presenta una unidad de micro-procesador 2. La unidad de micro-procesador 2 está acoplada con una memoria flash u otra memoria 4 reprogramable no volátil.

El micro-procesador 2 comienza normalmente en la dirección 0, por medio de que carga o ejecuta una primera instrucción en una dirección predeterminada fijamente desde la memoria flash 4. Después de esto el micro-procesador 1 carga una instrucción tras otra desde la memoria flash 4 conforme a un contador de direcciones incremental o conforme a órdenes de salto, que acaba de ejecutar.

No se ha implementado una memoria principal u otra memoria de acceso directo mayor de otro tipo. De este modo tampoco se dispone de una copia de una rutina de ejecución a ejecutar.

Un sistema de diagnóstico 5 o un dispositivo de aprontamiento para nuevas rutinas aplicativas puede acoplarse a través de un interfaz 6 con el micro-procesador 2.

A continuación se explica una forma de ejecución de un procedimiento corrector con base en el diagrama de flujo en la figura 2. En la memoria 4 reprogramable no volátil se archiva (10) una rutina de activación para un airbag. La rutina de activación es un ejemplo para múltiples rutinas aplicativas diferentes tipo flash.

En la rutina de activación se entrelaza (11) un código corrector. Se utiliza ventajosamente un código Reed-Solomon. El código Reed-Solomon hace posible corregir errores de bit aislados en la rutina de activación. El número de bits entrelazados adicionalmente para el código Reed-Solomon se elige según cuántos errores de bit deben corregirse todavía. Los bits adicionales para la corrección mediante el código Reed-Solomon pueden depositarse en una región de memoria separada, en lugar de entrelazarse en la rutina de activación.

Además de esto se calcula (12) un código de comprobación para la rutina de activación y se deposita en la memoria flash. El código de comprobación puede ser una suma de comprobación generada por ejemplo cíclicamente. En el caso de requisitos de seguridad reducidos pueden utilizarse también bits de comprobación de paridad sencillos.

Antes de...

Reivindicaciones:

1. Procedimiento corrector para un micro-procesador reprogramable, con los pasos

- (a) aprontamiento del micro-procesador con una memoria semiconductora reprogramable no volátil;

- (b) archivado de al menos una rutina aplicativa en la memoria semiconductora reprogramable no volátil;

- (c) aprontamiento de un código corrector para al menos una rutina aplicativa;

- (d) aprontamiento de un código de comprobación para al menos una rutina aplicativa;

- (e) comprobación de la integridad de al menos una rutina aplicativa archivada mediante el código de comprobación;

- (f) ejecución de una corrección mediante el código corrector, cuando falta la integridad de la rutina aplicativa, en donde la corrección se realiza en la memoria semiconductora reprogramable no volátil;

- (g) comprobación de la integridad de la rutina aplicativa corregida mediante el código de comprobación; y

- (h) adopción de una corrección exitosa, cuando se confirma la integridad de la rutina aplicativa corregida.

2. Procedimiento corrector según la reivindicación 1, en donde el micro-procesador carga instrucciones de las rutinas aplicativas, en cada caso directamente desde la memoria semiconductora reprogramable no volátil, para su ejecución.

3. Procedimiento corrector según la reivindicación 1 ó 2, en donde durante la corrección se regraba un bloque de la memoria semiconductora reprogramable no volátil.

4. Procedimiento corrector según una de las reivindicaciones anteriores, en donde una rutina correctora para ejecutar la corrección se archiva en un bloque propio.

5. Procedimiento corrector según la reivindicación anterior 4, en donde una corrección se considera no exitosa, si la rutina correctora archivada no presenta una integridad.

6. Procedimiento corrector según una de las reivindicaciones anteriores, en donde la memoria reprogramable no volátil es una memoria flash.

7. Procedimiento corrector según una de las reivindicaciones anteriores, en donde el código corrector es un código Reed-Solomon.

8. Procedimiento corrector según una de las reivindicaciones anteriores, en donde la integridad de la rutina aplicativa archivada se comprueba antes de que se ejecute la rutina aplicativa.

9. Dispositivo corrector, en especial para llevar a cabo uno de los procedimientos correctores según las reivindicaciones 1 a 8, con

una memoria (4) reprogramable no volátil para archivar al menos una rutina aplicativa, en cada caso un código de comprobación y en cada caso un código corrector para al menos una rutina aplicativa y

un dispositivo de tratamiento de datos (2) para llevar a cabo una comprobación de la integridad de la rutina aplicativa con base en el código de comprobación y para llevar a cabo una corrección utilizando el código corrector.

Patentes similares o relacionadas:

Método para hacer copia de seguridad de un contenido cinematográfico digital, del 29 de Abril de 2020, de ONO FILMS: Método para hacer copias de seguridad de un contenido cinematográfico digital, que incluye las etapas que consisten en: - generar, a partir de dicho contenido, un flujo […]

Método para la detección y corrección de errores en memorias volátiles, del 4 de Diciembre de 2015, de UNIVERSIDAD CARLOS III DE MADRID: La invención describe un método para la detección y corrección de múltiples errores en los datos almacenados en la memoria volátil de un sistema electrónico, como los […]

Método para la detección y corrección de errores en memorias volátiles, del 4 de Diciembre de 2015, de UNIVERSIDAD CARLOS III DE MADRID: La invención describe un método para la detección y corrección de múltiples errores en los datos almacenados en la memoria volátil de un sistema electrónico, como los […]

ALINEACION DE BITS DE PARIDAD PARA ELIMINAR ERRORES EN LA CONMUTACION DE UN CIRCUITO DE PROCESAMIENTO ACTIVO A UNO DE RESERVA., del 16 de Abril de 2007, de AT&T IPM CORP.: SE PRESENTA UN METODO DE CONMUTACION ENTRE UN APARATO DE COMUNICACION ACTIVO Y EN ESPERA QUE TENGA BITS DE PARIDAD JERARQUICAMENTE ANIDADOS. SE […]

PROCEDIMIENTO PARA LA TRANSMISION DE DATOS CON SEÑALIZACION SEGURA ENTRE ORDENADORES CON SEÑALIZACION SEGURA, ASI COMO DISPOSITIVO PARA ELLO., del 16 de Julio de 2006, de SIEMENS AKTIENGESELLSCHAFT: Procedimiento para la transmisión de datos útiles con señalización segura entre dos ordenadores (SRQ, SRS) con señalización segura de un sistema informático a través de la generación […]

PROCEDIMIENTO Y SISTEMA QUE PERMITE UTILIZAR DATOS EN FORMA DE COPIA INVERTIDA PARA DETECTAR DATOS ALTERADOS., del 1 de Marzo de 2001, de ABBOTT LABORATORIES: SE DETECTAN LOS ERRORES EN LOS DATOS ALMACENADOS EN LA MEMORIA DE UN ORDENADOR ANTES DE UTILIZAR LOS DATOS. AL ESCRIBIR UN PROGRAMA EN EL […]

PROCEDIMIENTO PARA SEGURIDAD DE DATOS, del 1 de Mayo de 1999, de ALCATEL ALSTHOM COMPAGNIE GENERALE D'ELECTRICITE: SEGURIDAD DE DATOS FIABLE MEDIANTE ADMINISTRACION DE MEMORIA DINAMICA. A PARTIR DE UNA MODIFICACION SE ELABORA PREVIAMENTE UN NUEVO VALOR DE LOS DATOS ACTUALES Y SE AVERIGUA […]

PROCEDIMIENTO DE DETECCION DE ERRORES DE EJECUCION DE UN LOGICIAL., del 1 de Noviembre de 1997, de GEC ALSTHOM TRANSPORT SA: PROCEDIMIENTO DE DETECCION DE ERRORES DE EJECUCION DE UN LOGICIAL, CUYAS VARIAS REPLICAS IDENTICAS SE EJECUTAN EN PARALELO O SECUENCIALMENTE, COMPRENDIENDO ESTE LOGICIAL EN […]

METODO DE AUTODIAGNOSTICO DE UN EQUIPO DE TELEFONO MOVIL PARA SU USO EN UN SISTEMA DE CONMUTACION DE TELEFONO MOVIL Y EQUIPO DE TELEFONO MOVIL APLICADO AL METODO., del 1 de Mayo de 1997, de NEC CORPORATION: EL PRESENTE INVENTO DESCRIBE UN METODO DE AUTODIAGNOSTICO QUE ACORTA EL TIEMPO DE DIAGNOSTICO DE UNA ROM QUE ESTA PROVISTA EN UN EQUIPO DE TELEFONO MOVIL PARA SU USO […]