Sistema de bloqueo y procedimiento del mismo.

Sistema de bloqueo, caracterizado por comprender una unidad de discriminación y conversión de fase digital,

una unidad de filtro del bucle digital y una unidad de oscilación digital controlada por la tensión que están conectados a su vez, de modo que, la unidad de discriminación y conversión de fase digital está configurada para llevar a cabo el procesamiento de discriminación y conversión de fase de una señal de entrada Fi de una fuente estándar externa y de una señal de salida de retroalimentación Fo de un oscilador de cristal termostático local que pasa por una división de frecuencia para generar una señal de reloj clk y una señal sign que se utiliza para indicar una relación de magnitud de la frecuencia entre la señal Fi y la señal Fo;

la unidad de filtro del bucle digital está configurada para llevar a cabo el procesamiento de filtrado de la señal clk y de la señal sign, y generar una señal adelantada que se utiliza para indicar que la frecuencia de la señal Fo es menor que la frecuencia de la señal Fi y una señal retardada que se utiliza para indicar que la frecuencia de la señal Fo es mayor que la frecuencia de la señal Fi;

la unidad de oscilación digital controlada por la tensión está configurada para llevar a cabo el procesamiento de oscilación controlado por la tensión para la señal adelantada y la señal retardada que se generan tras el procesamiento de filtrado de la señal clk y la señal sign, para implementar un bloqueo de la señal Fo y la señal Fi.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/CN2010/078003.

Solicitante: ZTE CORPORATION.

Nacionalidad solicitante: China.

Dirección: ZTE PLAZA, KEJI ROAD SOUTH, HI-TECH INDUSTRIAL PARK, NANSHAN DISTRICT SHENZHEN, GUANGDONG 518057 CHINA.

Inventor/es: LI, JIAN, LIU,YONGBO, ZHANG,HONGWEI, ZHANG,ZHAOLI, FAN,LIANG, LIU,ZHEN, JIA,YUTAO.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03L7/08 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03L CONTROL AUTOMATICO, ARRANQUE, SINCRONIZACION O ESTABILIZACION DE GENERADORES DE OSCILACIONES O DE IMPULSOS ELECTRONICOS (de generadores dinamoeléctricos H02P). › H03L 7/00 Control automático de frecuencia o fase; Sincronización (sintonización de circuitos resonantes en general H03J; sincronización en los sistemas de comunicación digital, ver los grupos apropiados en la clase H04). › Detalles del bucle cerrado en fase.

PDF original: ES-2535497_T3.pdf

Fragmento de la descripción:

Sistema de bloqueo y procedimiento del mismo Sector técnico

La presente invención se refiere a los campos de la comunicación, navegación y medición de espectros, etcétera y, en particular, a un sistema de bloqueo y su procedimiento. Las tecnologías relacionadas son conocidas a partir de los documentos US69746 B2 y US23/86339 A1.

Antecedentes de la técnica relacionada

Con el rápido desarrollo de la tecnología electrónica, los sectores de la comunicación, navegación, astronáutica, medición y control, medición de alta precisión, telefonía móvil y similares tienen cada vez más exigencias en algunos índices, tales como estabilidad a corto plazo, estabilidad a largo plazo y tasa de envejecimiento, etc., de la fuente de frecuencia. En la actualidad, con el rápido desarrollo de la tecnología de comunicaciones por módem, diversos sistemas de comunicación también tienen cada vez más exigencias de sincronización de tiempo y frecuencia. Actualmente, muchas salidas de frecuencia con alta estabilidad, alta precisión y buena tasa de envejecimiento se implementan utilizando un bucle de bloqueo de fase de alta precisión. El bloqueo de alta precisión, rápido, de una frecuencia de salida local y una frecuencia nominal se puede implementar utilizando el bucle de bloqueo de fase de alta precisión. El bloqueo de fase puede hacer que cada índice de frecuencia de la fuente local en la que uno de los índices de frecuencia es menor que el de la fuente estándar obtenga una mejora evidente. La velocidad de bloqueo y la precisión del bucle de bloqueo de fase son la base sobre la que se miden los índices del bucle de bloqueo de fase. En primer lugar, la precisión de bloqueo del bucle de bloqueo de fase debe ser suficientemente elevada, cuanto mayor sea la precisión del bloqueo de fase, menor será la diferencia de frecuencias entre la fuente bloqueada y la fuente estándar durante el bloqueo de la frecuencia y, de esta manera se implementa la sincronización entre sistemas más fácilmente. En segundo lugar, el bucle de bloqueo de fase debe poder implementar el bloqueo rápido, cuanto más rápida sea la velocidad de bloqueo del bucle de bloqueo de fase, más rápida será la implementación del bloqueo entre la fuente bloqueada y la fuente estándar, y cuanto más rápida sea la implementación de la sincronización de frecuencia entre las fuentes de frecuencia del sistema de comunicación, más rápido puede ser el seguimiento de la fuente bloqueada para implementar la sincronización.

El circuito del bucle con bloqueo de fase puede mejorar la estabilidad a corto plazo y la precisión de la salida de frecuencia de la frecuencia de salida de la fuente local, en particular, la mejora de la estabilidad a largo plazo de la misma es especialmente evidente. En los sectores tales como la navegación y similares, el bucle de bloqueo de fase puede hacer que un oscilador de cristal termostátlco local mantenga una buena estabilidad a corto plazo y la estabilidad a largo plazo del oscilador de cristal termostátlco local se puede mantener básicamente al nivel de un reloj atómico en el sistema de navegación debido a que el oscilador de cristal termostátlco local mantiene la sincronización con el reloj atómico en el sistema de navegación durante todo el tiempo. De esta manera, no solo se puede mantener una buena estabilidad a corto plazo del oscilador de cristal termostátlco sino que el oscilador de cristal termostático también puede obtener la mejor estabilidad a largo plazo que es próxima al nivel del reloj atómico debido al bloqueo. Debido al bloqueo con el reloj atómico, también se puede mejorar la estabilidad a corto plazo del oscilador de cristal termostático hasta cierto punto.

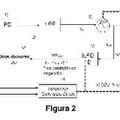

El PLL (bucle con bloqueo de fase) tradicional hace que las señales fin y fout pasen por un circuito de conversión de frecuencia complicado utilizando un divisor de frecuencia, convierte las señales fin y fout en las mismas señales de menor frecuencia y a continuación realiza una discriminación de fase, el principio de la cual se muestra en la figura 1.

El bucle de bloqueo de fase actual se clasifica principalmente en dos tipos: un bucle de bloqueo de fase analógico y un bucle de bloqueo de fase digital. El bucle de bloqueo de fase analógico es el bucle de bloqueo de fase que se aplica ampliamente inicialmente, que tiene la característica de una precisión de bloqueo de fase elevada. El filtro de paso bajo y el oscilador controlado por la tensión del circuito del bucle de bloqueo analógico son todos ellos circuitos analógicos con inconvenientes tales como deriva de carga, componentes propensos al envejecimiento e inestabilidad de los parámetros.

Antes de que apareciera el bucle de bloqueo de fase digital, el bucle de bloqueo de fase analógico se aplicaba ampliamente en diversos sectores debido a su elevada precisión de bloqueo de fase. En la actualidad, con el rápido desarrollo de los circuitos digitales, cada vez más sectores utilizan circuitos digitales y se puede decir que los circuitos digitales se aplican casi en todas partes. En algunos circuitos digitales, se requiere que el circuito analógico realice un proceso de conversión digital correspondiente cuando se utiliza el bucle de bloqueo de fase analógico para bloquear algunas señales digitales, lo que aumentará la complejidad del circuito del bucle de bloqueo de fase analógico, por lo tanto, las aplicaciones del bucle de bloqueo de fase analógico en algunos circuitos digitales son

limitadas.

El bucle de bloqueo de fase digital se puede aplicar directamente en el circuito digital del módem y la señal digital no necesita ser convertida primero en señal analógica y a continuación ser bloqueada utilizando el bucle de bloqueo de fase analógico. No obstante, en el bucle de bloqueo de fase digital tradicional también existen algunos problemas en lo siguiente:

1) Tiempo de bloqueo largo, el bucle de bloqueo de fase digital tradicional controla el oscilador de cristal termostático adoptando una señal que es dividida en frecuencia en primer lugar y a continuación pasa un filtro que utiliza un error de fase; se puede observar a partir de una fórmula de bucle del bucle de bloqueo de fase que, el proceso de bloqueo de fase del bucle de bloqueo de fase tradicional es un proceso de convergencia de la oscilación, y el tiempo de bloqueo es más largo debido a que existe un proceso repetitivo de convergencia;

2) la precisión del bloqueo de fase no es suficientemente elevada; para un bucle de bloqueo de fase digital completo implementado utilizando un DDS (slntetlzador digital directo), la precisión del bloqueo de fase no es suficientemente elevada debido a que la precisión del bloqueo de fase está afectada por la resolución del DDS.

En conclusión, el bucle de bloqueo de fase se aplica cada vez más ampliamente en los sectores tales como en comunicaciones de SDH (jerarquía digital síncrona), navegación y medición de alta precisión, etc. Particularmente, en el caso del sector de las comunicaciones de alta precisión que requieren que la salida de frecuencia de la fuente local sea coherente con la salida de frecuencia de la fuente estándar rápidamente, tales como la comunicación de SDH, no solo requiere poder implementar el bloqueo rápido entre la fuente local y la fuente estándar, sino que también requiere poder Implementar el bloqueo rápido y de elevada precisión.

Características de la Invención

El presente documento da a conocer un sistema de bloqueo y un procedimiento, que aumenta sustancialmente la velocidad de bloqueo del bloqueo de fase y que aumenta de manera significativa la precisión del bloqueo de fase.

Las características del procedimiento y del sistema según la presente invención se definen en las reivindicaciones independientes. En las reivindicaciones dependientes se dan a conocer mejoras y realizaciones adicionales.

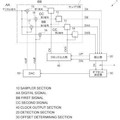

También se da a conocer un sistema de bloqueo, y el sistema comprende una unidad de discriminación y conversión de la fase digital, una unidad de filtro del bucle digital y una unidad de oscilación controlada por la tensión digital que están conectadas a su vez, en el que:

la unidad de discriminación y conversión de fase digital está configurada para llevar a cabo el proceso de discriminación y de conversión de fase de una señal de entrada F¡ de una fuente estándar externa y una señal de salida retroalimentada F de un oscilador de cristal termostático local que pasa por una división de frecuencia, para generar una señal de reloj (clk) y una señal de signo (sign) que se utiliza para indicar una relación de magnitud de frecuencias entre la señal F¡ y la señal F;

la unidad de filtro del bucle digital está configurada para llevar a cabo el proceso... [Seguir leyendo]

Reivindicaciones:

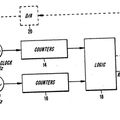

1. Sistema de bloqueo, caracterizado por comprender una unidad de discriminación y conversión de fase digital, una unidad de filtro del bucle digital y una unidad de oscilación digital controlada por la tensión que están conectados a su vez, de modo que, la unidad de discriminación y conversión de fase digital está configurada para llevar a cabo el procesamiento de discriminación y conversión de fase de una señal de entrada F¡ de una fuente estándar externa y de una señal de salida de retroalimentación F de un oscilador de cristal termostático local que pasa por una división de frecuencia para generar una señal de reloj clk y una señal sign que se utiliza para indicar una relación de magnitud de la frecuencia entre la señal F¡ y la señal F;

la unidad de filtro del bucle digital está configurada para llevar a cabo el procesamiento de filtrado de la señal clk y de la señal sign, y generar una señal adelantada que se utiliza para indicar que la frecuencia de la señal F es menor que la frecuencia de la señal F¡ y una señal retardada que se utiliza para indicar que la frecuencia de la señal F es mayor que la frecuencia de la señal F¡;

la unidad de oscilación digital controlada por la tensión está configurada para llevar a cabo el procesamiento de oscilación controlado por la tensión para la señal adelantada y la señal retardada que se generan tras el procesamiento de filtrado de la señal clk y la señal sign, para implementar un bloqueo de la señal F y la señal Fi.

2. Sistema, según la reivindicación 1, en el que la unidad de discriminación y conversión de fase digital comprende un discriminador de fase escalonada digital y un módulo de conversión, en los que,

el discriminador de fase escalonada digital está configurado para llevar a cabo el proceso de discriminación de fase de la señal F¡ y de la señal F y genera un error de señal de Impulsos que se utiliza para Indicar una relación de fase

entre la señal F¡ y la señal F;

el módulo de conversión está configurado para calcular una anchura de Impulso del error de la señal de Impulsos según un contaje de la señal de contaje, y generar la señal sign que Indica la relación de magnitud de frecuencias entre la señal F¡ y la señal F y una señal equ_nequ que Indica si las anchuras de Impulso vecinos son ¡guales y llevar a cabo un procesamiento AND para la señal equ_nequ y la señal F¡ para generar la señal de reloj clk;

en que, el contaje de la señal de contaje se implementa mediante un cálculo del intervalo de tiempos y la señal sign indica la relación de magnitud de frecuencias entre la señal F¡ y la señal F mediante la relación de magnitud de las anchuras de impulso vecinos en el error de la señal de impulsos.

3. Sistema, según la reivindicación 1 ó 2, en el que la unidad de oscilación controlada por la tensión digital comprende un convertidor digital-analógico (DA) y un oscilador controlado por la tensión digital, de modo que,

el convertidor DA está configurado para recibir las señales adelantadas y retardadas emitidas por la unidad de filtro del bucle digital, y tras llevar a cabo la conversión digital-analógica controlando el convertidor DA utilizando las señales recibidas, transmite señales al oscilador controlado por la tensión digital;

el oscilador digital controlado por la tensión está configurado para llevar a cabo el proceso de oscilación controlado por la tensión a las señales transmitidas por el convertidor DA.

4. Sistema, según la reivindicación 1 ó 2, en el que, la unidad de oscilación digital controlada por la tensión comprende un módulo de modulación por anchura de impulso (PWM) y un oscilador digital controlado por la tensión, en el que,

el módulo de PWM está configurado para: generar una onda de PWM con un periodo constante y una anchura de impulso ajustable de alto nivel y para llevar a cabo una modulación de anchura de impulso a la onda de PWM utilizando las señales adelantadas y retardadas emitidas por la unidad de filtro del bucle digital y transmite la señal tras la modulación de anchura de impulso al oscilador digital controlado por la tensión;

el oscilador digital controlado por la tensión está configurado para llevar a cabo el proceso de oscilación controlado por la tensión a la señal transmitida por el módulo de PWM.

5. Sistema, según la reivindicación 4, en el que,

el módulo de PWM está implementado por un procesador de una disposición de puertas programable por campo o un dispositivo lógico programable en el sistema de bloqueo mediante la configuración de tiempos.

6. Procedimiento de bloqueo, caracterizado por comprender:

un sistema de bloqueo que lleva a cabo un proceso de discriminación y conversión de fase de una señal de entrada F¡ de una fuente estándar externa y una señal de salida de retroallmentación F de un oscilador de cristal termostático que pasa por una división de frecuencia para generar una señal de reloj clk y una señal sign que se utiliza para Indicar una relación de magnitud de frecuencias entre la señal F¡ y la señal F y para llevar a cabo el proceso de filtrado de la señal clk y de la señal sign, y llevar a cabo un proceso de oscilación controlada por la tensión de una señal adelantada que se utiliza para Indicar que la frecuencia de la señal F es menor que la frecuencia de la señal F¡ y una señal retardada que se utiliza para indicar que la frecuencia de la señal F es mayor que la frecuencia de la señal F¡ que se generan tras el procesamiento de filtrado para implementar un bloqueo de la señal F y de la señal F¡.

7. Procedimiento, según la reivindicación 6, en el que,

la etapa del sistema de bloqueo que lleva a cabo el procesamiento de discriminación y conversión de fase de la señal F¡ y de la señal F que pasan por la división de frecuencia para generar la señal clk y la señal sign que se utiliza para indicar la relación de magnitud de frecuencias entre la señal F¡ y la señal F comprende;

el sistema de bloqueo que lleva a cabo el proceso de discriminación de fase de la señal F¡ y de la señal F genera en primer lugar, un error de la señal de impulsos que se utiliza para indicar una relación de fase entre la señal F¡ y la señal F, calculando una anchura de impulso del error de la señal de impulsos según el contaje de la señal de contaje, generando la señal sign que indica la relación de magnitud de frecuencias entre la señal F¡ y la señal F y una señal equ_nequ que indica si las anchuras de impulso vecinas son iguales, y llevar a cabo el procesamiento AND de la señal equ_nequ y de la señal F¡ para generar la señal de reloj clk; en que, el contaje de la señal de contaje se implementa mediante un cálculo del intervalo de tiempos, y la señal sign indica la relación de magnitud de frecuencias entre la señal F¡ y la señal F mediante la relación de magnitud de las anchuras de impulso vecinas en el error de la señal de impulsos.

8. Procedimiento, según la reivindicación 6 ó 7, en el que, antes de la etapa de llevar a cabo el procesamiento de oscilación controlado por la tensión de las señales adelantada y retardada, el procedimiento comprende, además:

el sistema de bloqueo que controla una conversión digital-analógica utilizando las señales adelantada y retardada.

9. Procedimiento, según las reivindicaciones 6 ó 7, en el que antes de la etapa de llevar a cabo el procesamiento de oscilación controlado por la tensión de las señales adelantada y retardada, el procedimiento comprende, además:

el sistema de bloqueo que lleva a cabo una modulación de anchura de impulso de una onda de modulación de anchura de impulso (PWM) mediante las señales adelantada y retardada.

1. Procedimiento, según la reivindicación 9, en el que,

la onda de PWM es una onda de PWM con un periodo constante y una anchura de Impulso ajustable de alto nivel, que es generada mediante un procesador con una disposición de puertas programables por campo o un dispositivo lógico programable en el sistema de bloqueo mediante una configuración de tiempos.

Patentes similares o relacionadas:

Linealizador de forma de onda, del 12 de Junio de 2019, de MBDA UK LIMITED: Una fuente de barrido de frecuencia para un radar FMCW que comprende un sintetizador de frecuencia de bucle de bloqueo de fase, incluyendo el bucle bloqueado […]

Circuito de generación de reloj y procedimiento de generación de la señal de reloj, del 12 de Junio de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un circuito de generación de reloj , que comprende una primera fuente de reloj , una segunda fuente de reloj y un circuito de puerta lógica , […]

Potencia programable para una interfaz de memoria, del 21 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para el control de retardo en una interfaz de memoria, que comprende: proporcionar una polarización de voltaje a un circuito […]

Procedimiento, circuito de mando de bus CAN y sistema bus CAN para la recuperación de una frecuencia de pulso de reloj de un bus CAN, del 15 de Enero de 2014, de ROBERT BOSCH GMBH: Procedimiento para la recuperación de una frecuencia de pulso de reloj (T) de un bus CAN con un dispositivomaestro con un generador […]

SINTETIZADOR DE FRECUENCIA Y DIVISOR DE FRECUENCIA POR D BASADO EN LA TOPOLOGÍA DE ENGANCHE POR INYECCIÓN, del 1 de Marzo de 2013, de UNIVERSITAT POLITECNICA DE CATALUNYA: Sintetizador de frecuencia y divisor de frecuencia por D basado en la topología de enganche por inyección.

El sintetizador comprende:

- un […]

SINTETIZADOR DE FRECUENCIA Y DIVISOR DE FRECUENCIA POR D BASADO EN LA TOPOLOGÍA DE ENGANCHE POR INYECCIÓN, del 1 de Marzo de 2013, de UNIVERSITAT POLITECNICA DE CATALUNYA: Sintetizador de frecuencia y divisor de frecuencia por D basado en la topología de enganche por inyección.

El sintetizador comprende:

- un […]

Dispositivo de recuperación de datos de reloj, del 30 de Enero de 2013, de Thine Electronics, Inc: Un dispositivo de recuperación de reloj / datos para recuperar una señal de reloj y datos, en base a una señal digital de entrada, que comprende:

un muestreador […]

Dispositivo de recuperación de datos de reloj, del 30 de Enero de 2013, de Thine Electronics, Inc: Un dispositivo de recuperación de reloj / datos para recuperar una señal de reloj y datos, en base a una señal digital de entrada, que comprende:

un muestreador […]

CALIBRACION DEL ANCHO DE BANDA PARA UN BUCLE BLOQUEADO EN FRECUENCIA., del 16 de Marzo de 2006, de TELEFONAKTIEBOLAGET L M ERICSSON (PUBL): Un método para calibrar un bucle bloqueado o fijado en frecuencia, que está destinado a filtrar una señal de referencia extraída de una red de transporte para utilizarla […]

METODO Y APARATO PARA REDUCIR LA CORRIENTE EN MODO DE ESPERA EN EQUIPOS DE COMUNICACIONES, del 16 de Septiembre de 2007, de TELEFONAKTIEBOLAGET L M ERICSSON (PUBL): ESTA INVENCION SE REFIERE A UN PROCEDIMIENTO Y A UN APARATO QUE SIRVEN PARA REDUCIR EL CONSUMO DE ENERGIA DE UN DISPOSITIVO DE COMUNICACIONES. EN MODO DE VIGILIA, […]

METODO Y APARATO PARA REDUCIR LA CORRIENTE EN MODO DE ESPERA EN EQUIPOS DE COMUNICACIONES, del 16 de Septiembre de 2007, de TELEFONAKTIEBOLAGET L M ERICSSON (PUBL): ESTA INVENCION SE REFIERE A UN PROCEDIMIENTO Y A UN APARATO QUE SIRVEN PARA REDUCIR EL CONSUMO DE ENERGIA DE UN DISPOSITIVO DE COMUNICACIONES. EN MODO DE VIGILIA, […]