Control de energía de un dispositivo externo durante el modo de dormir de baja potencia sin intervención de la unidad de procesamiento central.

Un dispositivo digital de circuito integrado operable para determinar el control y el estado de un dispositivo externo con independencia del momento en el que el dispositivo (202) digital está en un modo de dormir de baja potencia,

que comprende:

un procesador (204) digital que incorpora una entrada de despertar, la entrada de despertar despierta el procesador (204) digital de un modo de dormir a un modo operativo cuando un primer nivel lógico es aplicado a aquél y no despierta el procesador (204) digital cuando un segundo nivel lógico es aplicado a aquél;

un temporizador (224) de energización acoplado con un primer nodo (216), en el que el temporizador (224) de energización proporciona una señal de energización del dispositivo externo en el primer nodo (216) durante un primer periodo de tiempo;

un temporizador (214) de muestras, en el que el temporizador (214) de muestras provoca que una señal de salida del dispositivo externo recibida en un segundo nodo sea aplicada a la entrada de despertar del procesador (204) durante un segundo periodo de tiempo, en el que durante el segundo periodo de tiempo, la señal de salida del dispositivo externo define si el procesador (204) se despierta al modo operativo o permanece en el modo de dormir.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2011/021689.

Solicitante: MICROCHIP TECHNOLOGY INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 2355 WEST CHANDLER BOULEVARD CHANDLER, AZ 85224-6199 ESTADOS UNIDOS DE AMERICA.

Inventor/es: SIMMONS,MICHAEL, CATHERWOOD,MICHAEL.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F1/32 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 1/00 Detalles no cubiertos en los grupos G06F 3/00 - G06F 13/00 y G06F 21/00 (arquitecturas de computadores con programas almacenados de propósito general G06F 15/76). › Medios destinados a economizar energía.

PDF original: ES-2503590_T3.pdf

Fragmento de la descripción:

Control de energía de un dispositivo externo durante el modo de dormir de baja potencia sin intervención de la unidad de procesamiento central

La presente divulgación se refiere a dispositivos de circuitos integrados y, más concretamente, a los ahorros de energía de los dispositivos de circuito integrado en modos dormir de baja potencia.

En los actuales modos de baja potencia (Dormir, Sueño Profundo, etc.), existen diversas formas de despertar un dispositivo de circuito integrado partiendo de un modo de baja potencia. Una de dichas formas consiste en el empleo de una señal de despertar externa (a menudo una entrada de interrumpir con cambio de propósito). Sin embargo, esto requiere que la fuente de la señal de despertar esté activa mientras el dispositivo de circuito integrado está en su modo de baja potencia, lo que se traduce en un consumo de energía global del sistema mayor del requerido.

Un procedimiento y un sistema para reducir el consumo de energía según lo descrito con anterioridad se conoce, por ejemplo, a partir de la Publicación de Solicitud de Patente estadounidense US 29/7744.

Los problemas mencionados con anterioridad pueden ser resueltos, y pueden conseguirse beneficios adicionales, mediante un dispositivo de circuito integrado, un sistema y un procedimiento según lo definido en las reivindicaciones independientes. Otras mejoras se incluyen en las reivindicaciones dependientes. De acuerdo con diversas formas de realización, un(os) dispositivo(s) externo(s) es (son) despertado(s) sin la intervención de circuitos lógicos principales, por ejemplo, un procesador, que puedan estar en un modo de sueño profundo, de baja potencia. Esta posibilidad puede conseguirse con, por ejemplo, sin que ello constituya una limitación, los existentes temporizadores de modo de baja potencia, por ejemplo, un reloj y calendario en tiempo real (RTCC), un temporizador de vigilancia (WDT), un WDT de Sueño Profundo, un tempoñzador de propósito general, etc.) utilizando una función a modo de modulación simplificada de impulsos de dos canales. Dicha energización (despertar) periódica puede incorporarse en un dispositivo externo, por ejemplo un sensor de la temperatura, esperar a que se ponga en marcha y que se estabilice, muestree su señal de salida de despertar y, a continuación, desenergizarlo, todo ello sin que en ningún momento se requiera que la lógica de circuito principal de un dispositivo digital abandone un modo de baja potencia.

De acuerdo con una forma de realización ejemplar especifica de la presente divulgación, un dispositivo digital de circuito integrado determina el control y la determinación de un estado de un dispositivo externo con independencia del momento en el que el dispositivo digital está en un modo de dormir de baja potencia, comprende: un procesador digital que incorpora una entrada de despertar, la entrada de despertar despierta el procesador digital desde un modo de dormir hasta un modo operativo cuando, en un primer nivel lógico, se aplica a aquél y no despierta el procesador digital cuando se aplica a aquél un segundo nivel lógico; un temporizador de energización acoplado a un dispositivo externo, en el que el temporizador de energización provoca que el dispositivo externo lleve a cabo un modo operativo durante un primer periodo de tiempo; un temporizador de muestras, en el que el temporizador de muestras provoca que una salida procedente del dispositivo externo sea aplicada a la entrada de despertar del temporizador durante un segundo periodo de tiempo, en el que durante el segundo periodo de tiempo, si la salida del dispositivo externo está en el primer nivel lógico, entonces el procesador se despierta al modo operativo; y si la salida del dispositivo externo está en el segundo nivel lógico, entonces el procesador permanece en el modo de dormir.

De acuerdo con otra forma de realización ejemplar específica de la presente divulgación, un dispositivo de señal mixta de circuito integrado determina el control y el estado de un dispositivo externo con independencia del momento en el que el dispositivo de señal mixta en un estado de dormir de baja potencia comprende: un procesador digital que incorpora una entrada de despertar, la entrada de despertar despierta el procesador digital desde un modo de dormir a un modo operativo cuando un primer nivel lógico es aplicado a aquél y no despierta el procesador digital cuando un segundo nivel lógico es aplicado a aquél; un comparador que incorpora una primera entrada acoplada a una salida analógica a un dispositivo externo; una referencia de tensión que incorpora una salida de tensión de referencia conectada a una segunda entrada del comparador; un temporizador de energización acoplado al dispositivo externo, en el que el temporizador de energización provoca que el dispositivo externo lleve a cabo un modo operativo durante un primer periodo de tiempo; un temporizador de muestras, en el que el temporizador de muestras provoca que una salida procedente del comparador sea aplicada a la entrada de despertar del procesador durante un segundo periodo de tiempo, en el que durante el segundo periodo de tiempo, si la salida analógica del dispositivo externo es mayor que la salida de la tensión de referencia, entonces el procesador se despierta al modo operativo; y si la salida analógica del dispositivo externo es igual o inferior a la salida de la tensión de referencia, entonces el procesador permanece en el modo de dormir.

De acuerdo con otra forma de realización ejemplar específica adicional de la presente divulgación, un procedimiento para conservar energía y verificar el estado de un dispositivo externo sin tener que despertar circuitos digitales de un dispositivo de circuito integrado a partir de un modo de dormir de baja potencia comprende las etapas de: la aplicación de energía a un dispositivo externo durante un primer periodo de tiempo a partir de un temporizador de energización; la comparación deuna salida procedente del dispositivo externo con un valor de referencia durante un segundo periodo de tiempo a partir de un temporizador de muestreo, comenzando el segundo periodo de tiempo

después de que el primer periodo de tiempo haya comenzado; en el que durante el segundo periodo de tiempo, si la salida del dispositivo externo es mayor que el valor de referencia, entonces los circuitos digitales de un dispositivo de circuito integrado se despiertan a un modo operativo; y si la salida del dispositivo externo es igual o inferior al valor de referencia, entonces los circuitos digitales de un circuito integrado aparecen en un modo de dormir.

Una más completa comprensión de la presente divulgación se puede obtener con referencia a la descripción subsecuente tomada en combinación con los dibujos que se acompañan, en los que:

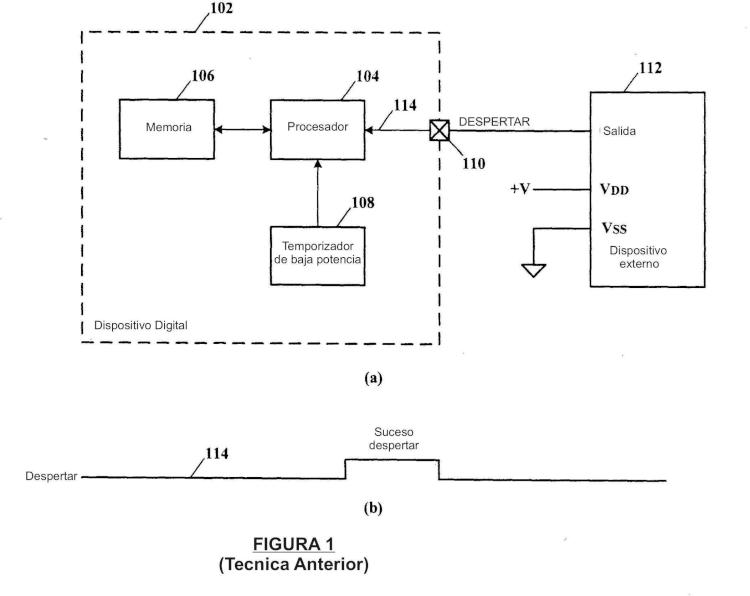

La Figura 1 ilustra un diagrama de bloques esquemático de un dispositivo digital de la técnica anterior que presenta un modo de dormir y un dispositivo externo acoplado a y adaptado para despertar el dispositivo digital, y un diagrama de temporización de la operación del dispositivo externo;

la Figura 2 ilustra un diagrama de bloques esquemático de un dispositivo digital de circuito integrado que incorpora un modo de dormir, unos temporizadores de energización y muestreo, y un dispositivo externo cuya vigilancia de los tiempos de trabajo operativos y de los sucesos es controlada por el dispositivo digital, y un diagrama de temporización de la operación de aquél, de acuerdo con una forma de realización ejemplar específica de la presente divulgación;

la Figura 3 ilustra un diagrama de bloques esquemático de un dispositivo de señal mixta de circuito integrado que incorpora un modo de dormir, unos temporizadores de energización y muestreo, y un dispositivo externo cuya vigilancia de los tiempos de trabajo operativos y de los sucesos es controlada por el dispositivo de señal mixta, y un diagrama de temporización de la operación de aquél de acuerdo con otra forma de realización específica de la presente divulgación;

la Figura 4 ilustra un diagrama de bloques esquemático de los circuitos de las Figuras 2 y 3 que incorpora un relé de potencia interpuesto controlado por el dispositivo de circuito integrado y que suministra energía al dispositivo externo de acuerdo con las formas de realización ejemplares específicas de la presente

divulgación.

Con referencia ahora a los dibujos, se ilustran, de manera esquemática, los detalles de una forma de realización ejemplar. Los mismos elementos de los dibujos se representarán mediante los mismos números, y elementos similares serán representados mediante los mismos números con un sufijo en letras minúsculas diferente.

Con referencia a la Figura 1, en ella se representa un diagrama de bloques... [Seguir leyendo]

Reivindicaciones:

1.- Un dispositivo digital de circuito integrado operable para determinar el control y el estado de un dispositivo externo con independencia del momento en el que el dispositivo (22) digital está en un modo de dormir de baja potencia, que comprende:

un procesador (24) digital que incorpora una entrada de despertar, la entrada de despertar despierta el procesador (24) digital de un modo de dormir a un modo operativo cuando un primer nivel lógico es aplicado a aquél y no despierta el procesador (24) digital cuando un segundo nivel lógico es aplicado a aquél;

un temporizador (224) de energización acoplado con un primer nodo (216), en el que el temporizador (224) de energización proporciona una señal de energización del dispositivo externo en el primer nodo (216) durante un primer periodo de tiempo;

un temporizador (214) de muestras, en el que el temporizador (214) de muestras provoca que una señal de salida del dispositivo externo recibida en un segundo nodo sea aplicada a la entrada de despertar del procesador (24) durante un segundo periodo de tiempo, en el que durante el segundo periodo de tiempo, la señal de salida del dispositivo externo define si el procesador (24) se despierta al modo operativo o permanece en el modo de dormir.

2.- El dispositivo digital de circuito integrado de acuerdo con la reivindicación 1, en el que el segundo periodo de tiempo comienza de forma simultánea con el inicio del primer periodo de tiempo.

3.- El dispositivo digital de circuito integrado de acuerdo con la reivindicación 1, en el que el segundo periodo de tiempo comienza después de que el primer periodo de tiempo haya comenzado.

4.- El dispositivo digital de circuito integrado de acuerdo con la reivindicación 1, en el que la señal de salida del dispositivo externo recibida en el segundo nodo y una salida procedente del temporizador de muestras son conjuntamente sometidas a una operación booleana AND lógica aplicada a la entrada de despertar del procesador (24) digital.

5.- El dispositivo digital de circuito integrado de acuerdo con la reivindicación 1, que comprende además:

un comparador (32) que incorpora una primera entrada acoplada al segundo nodo y una salida acoplada a la entrada de despertar, en el que la salida es habilitada por el temporizador (222) de muestras;

una referencia (322) de la tensión que incorpora una salida de la tensión de referencia conectada a una segunda entrada del comparador (32).

6.- El dispositivo digital de circuito integrado de acuerdo con la reivindicación 5, en el que el temporizador (224) de energización está configurado para activar la referencia (322) de voltaje y / o el comparador (32).

7.- El dispositivo digital de circuito integrado de acuerdo con la reivindicación 1, en el que el temporizador (224) de energización y el temporizador (222) de muestras y, de manera opcional, el comparador (32) y / o la referencia (322) de la tensión, operan con una cantidad mínima de energía y, en particular, en el que el temporizador (224) de energización y / o el temporizador (222) de muestras puede ser un temporizador de propósito general, un reloj y calendario en tiempo real (RTCC), un temporizador de vigilancia (WDT), o un WDT de sueño profundo.

8.- El dispositivo digital de circuito integrado de acuerdo con la reivindicación 1, en el que la señal de salida del dispositivo externo puede ser una señal analógica o digital, en particular una señal de salida generada por un sensor de la temperatura, un sensor de la presión, un sensor de la humedad, un sensor del pH, un sensor de la corriente, o un sensor de la tensión.

9.- Un sistema que comprende un dispositivo de circuito integrado de acuerdo con una de las reivindicaciones precedentes, que comprende además:

un dispositivo (112, 312) externo, el cual, de modo preferente, puede ser un sensor de temperatura, un sensor de la presión, un sensor de la humedad, un sensor del pH, un sensor de la corriente o un sensor de la tensión, que incorpora una entrada de energía acoplada con el primer nodo (216) y una salida digital o analógica acoplada con el segundo nodo.

1.- El sistema de acuerdo con la reivindicación 9, que comprende además un relé (422) de potencia interpuesto, en particular un transistor de potencia, controlado por el temporizador (224) de energización y que suministra energía al dispositivo (112, 312) externo.

11.- Un procedimiento de conservación de energía y de vigilancia del estado de un dispositivo externo sin tener que despertar los circuitos digitales de un dispositivo de circuito integrado, a partir de un modo de dormir de baja potencia, comprendiendo dicho procedimiento las etapas de:

la regulación de un procesador (24) digital del dispositivo (22) de circuito integrado en un modo de dormir;

la aplicación de energía a un dispositivo (112, 312) externo, durante un primer periodo de tiempo por medio de un temporizador (224) de energización del dispositivo (22) de circuito integrado;

la aplicación de una señal de salida procedente del dispositivo (112, 312) externo, durante un segundo

periodo de tiempo definido por un temporizador (222) de muestras del dispositivo (22) de circuito integrado a una entrada de despertar de un procesador (24) digital del dispositivo (22) de circuito integrado,

en el que la señal de salida define si el procesador (24) se despierta en un modo operativo o permanece en el modo de dormir.

12.- El procedimiento de acuerdo con la reivindicación 11, en el que el segundo periodo de tiempo comienza de

manera simultánea con el inicio del primer periodo de tiempo.

13.- El procedimiento de acuerdo con la reivindicación 11, en el que el segundo periodo de tiempo comienza después de que el primer periodo de tiempo haya comenzado.

14.- El procedimiento de acuerdo con una de las reivindicaciones precedentes 11 a 13, que comprende además la 15 puesta en práctica de una operación booleana lógica AND sobre la señal de salida con una salida procedente del

temporizador de muestras y la aplicación de la señal resultante a la entrada de despertar del procesador (24) digital.

15.- El procedimiento de acuerdo con una de las reivindicaciones precedentes 11 a 13, en el que la señal de salida del dispositivo (112, 312) externo es un valor analógico y el procedimiento comprende la etapa de comparación del

valor analógico con un valor de referencia, que puede ser programable, en el que un resultado lógico de la comparación es alimentado a la entrada de despertar del procesador (24) digital.

Patentes similares o relacionadas:

Método de control de terminal, dispositivo y terminal, del 3 de Junio de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de control de terminal, en donde el método comprende: cuando una pantalla de un terminal se conmuta de un estado de pantalla encendida a […]

Técnicas de ahorro de energía para sistemas de memoria, del 22 de Abril de 2020, de QUALCOMM INCORPORATED: Un procesador central , que comprende: una interfaz de capa física, PHY, configurada para acoplarse a una pluralidad de carriles de datos de un […]

Procesamiento de datos a partir de un dispositivo de procesamiento portátil, del 1 de Abril de 2020, de Sensyne Health Group Limited: Un procedimiento implementado por ordenador de procesamiento de datos a partir de un dispositivo de procesamiento portátil para determinar cuándo el dispositivo […]

Sistema y método para el control de múltiples reguladores de tensión, del 25 de Marzo de 2020, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Una unidad de gestión de energía , que comprende: un circuito de control digital operativo para generar primero y segundo valores de tensión (logic_vsel, […]

Procedimiento para el funcionamiento temporal de un dispositivo de análisis automático en un modo de espera, del 8 de Enero de 2020, de SIEMENS HEALTHCARE DIAGNOSTICS PRODUCTS GMBH: Procedimiento para el funcionamiento de un dispositivo de análisis automático en un modo de espera; en donde el dispositivo de análisis automático comprende una […]

Mejoras a los patrones IEC 61968-9:2013 para las comunicaciones de un sistema de servicios públicos, del 22 de Octubre de 2019, de Aclara Technologies LLC: Mejoras en los patrones de lectura de contadores IEC 61968-9:2013. Estos incluyen la compresión significativa de los mensajes en un solo número entero que, cuando se transmite […]

Procedimiento y aparato de control de una interfaz periférica serie de sensor de huellas dactilares, y terminal móvil, del 16 de Octubre de 2019, de Guangdong OPPO Mobile Telecommunications Corp., Ltd: Un procedimiento de control de una interfaz periférica serie de un sensor de huellas dactilares, en donde el sensor de huellas dactilares es uno de un sensor óptico […]

Procedimiento de prueba de pulsera inteligente y sistema de prueba para la misma, del 2 de Octubre de 2019, de Huizhou Tcl Mobile Communication Co., Ltd: Procedimiento de prueba para una pulsera inteligente, la función Bluetooth de la pulsera inteligente se pone en estado de reposo mediante la configuración […]