Circuito de autotest integrado de TSVs.

La invención presenta un sistema autotest integrado para la detección de defectos en TSVs (Through Silicon Vias o vías a través de silicio) durante la fase pre-bond,

durante la cual solo uno de los terminales de la TSV es accesible. En ausencia de un defecto, el sistema evoluciona siempre hacia un mismo estado predefinido. En presencia de un defecto, el sistema evoluciona hacia otro estado diferente del establecido en ausencia de defecto. Esta invención permite a su vez que la misma estructura se utilice para la reconfiguración del circuito al final del proceso de fabricación si el resultado del test determina la presencia de una TSV defectuosa.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P201231554.

Solicitante: UNIVERSITAT POLITECNICA DE CATALUNYA.

Nacionalidad solicitante: España.

Inventor/es: FIGUERAS PAMIES,JOAN, ARUMI DELGADO,Daniel, RODRÍGUEZ MONTAÑÉS,Rosa.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G01R31/3187 FISICA. › G01 METROLOGIA; ENSAYOS. › G01R MEDIDA DE VARIABLES ELECTRICAS; MEDIDA DE VARIABLES MAGNETICAS (indicación de la sintonización de circuitos resonantes H03J 3/12). › G01R 31/00 Dispositivos para ensayo de propiedades eléctricas; Dispositivos para la localización de fallos eléctricos; Disposiciones para el ensayo eléctrico caracterizadas por lo que se está ensayando, no previstos en otro lugar (ensayo o medida de dispositivos semiconductores o de estado sólido, durante la fabricación H01L 21/66; ensayo de los sistemas de transmisión por líneas H04B 3/46). › Ensayos integrados.

- H05K1/14 ELECTRICIDAD. › H05 TECNICAS ELECTRICAS NO PREVISTAS EN OTRO LUGAR. › H05K CIRCUITOS IMPRESOS; ENCAPSULADOS O DETALLES DE LA CONSTRUCCIÓN DE APARATOS ELECTRICOS; FABRICACION DE CONJUNTOS DE COMPONENTES ELECTRICOS. › H05K 1/00 Circuitos impresos. › Asociación estructural de varios circuitos impresos (medios de conexión eléctrica de circuitos con o entre circuitos impresos H05K 1/11, H01R 12/00).

- H05K3/42 H05K […] › H05K 3/00 Aparatos o procedimientos para la fabricación de circuitos impresos. › Agujeros de paso metalizados.

Fragmento de la descripción:

Circuito de autotest integrado de TSVs.

SECTOR DE LA TÉCNICA:

La invención se refiere a un circuito electrónico y al método para el autotest integrado de TSVs (Through Silicon Vias o vías a través de silicio) durante la etapa pre-bond (antes de la interconexión de los diferentes circuitos apilados) y la reconfiguración del circuito una vez finalizado el proceso de fabricación si el resultado del test determina la presencia de una TSV defectuosa.

ESTADO DE LA TÉCNICA:

Los circuitos 3D son una tecnología prometedora para cumplir las exigencias de la industria semiconductora en relación a integración, prestaciones i consumo de circuitos integrados. Los circuitos 3D se caracterizan por integrar en un único encapsulado una serie de circuitos 2D apilados e interconectados entre sí. La forma más común de interconectar los circuitos 2D es mediante Through Silicon Vias (vías a través de silicio o TSVs) . Una TSV es una vía vertical que conecta dos circuitos a través de silicio o capas de óxido. Las principales ventajas de las TSV respecto otras alternativas (wire-bonds o micro-bumps) son sus altas prestaciones y su mayor densidad de integración, que puede llegar hasta los 10k/mm2.

Como cualquier otro circuito, los circuitos 3D se deben verificar antes de enviarse al cliente. Considerando la inmadurez de la tecnología 3D i la densidad de TSVs, estas estructuras son susceptibles de sufrir defectos durante el proceso de fabricación así como durante su vida útil. Los defectos más comunes que afectan las TSVs son defectos del tipo cortocircuitos y abiertos. Los cortocircuitos más comunes se generan por la degradación o perforación de la capa de aislante entre el metal y el sustrato, provocando una conexión no deseada entre estos dos materiales. Por otro lado, un abierto es la desconexión (parcial o total) de dos puntos de la TSV que deberían estar conectados. Un ejemplo típico son los huecos generados por un relleno defectuoso de metal. Por todos estos motivos, el test específico de TSVs es de vital importancia para asegurar la calidad de los circuitos 3D. El test de TSVs se realiza principalmente durante dos etapas del proceso de fabricación: antes de apilar los circuitos 2D, prebond test, y después de apilarse, post-bond test. El pre-bond test es necesario para detectar circuitos defectuosos en una etapa temprana del proceso de producción y no malgastar así recursos en acabar la fabricación de circuitos que serán finalmente descartados. Por otro lado, el post-bond test es necesario para asegurar la calidad del producto final.

Como la probabilidad de encontrar una TSV defectuosa es elevada, es frecuente añadir técnicas de redundancia y reconfiguración para poder reutilizar parte de estos circuitos. De esta manera se aumenta el rendimiento del proceso de fabricación en aquellos casos donde el número de TSVs defectuosas así lo permita. En el documento de patente US20100060310 se presentan diferentes sistemas y metodologías para proporcionar redundancia y reconfiguración al circuito en presencia de defectos.

Durante la etapa pre-bond, la TSV queda enterrada parcialmente en el sustrato. El aislamiento entre la TSV i el sustrato se realiza intercalando una capa de óxido. Este proceso se puede realizar de dos maneras. La primera consiste en aislar únicamente la superficie lateral de la TSV, quedando un terminal conectado directamente a sustrato. En el documento de patente US20120153280A1 se propone un circuito para detectar defectos en TSVs en estas condiciones mediante un test de corriente. El segundo proceso consiste en aislar la TSV del sustrato en su totalidad. Para la presente invención se considera que la TSV está aislada completamente del sustrato.

El pre-bond test es un proceso complejo, ya que las TSVs son demasiado pequeñas y numerosas para poder realizar el test con puntas. Por este motivo, se han desarrollado metodologías y circuitos basados en el autotest integrado (BIST o Built-in Self-Test) para detectar defectos durante el pre-bond test. La complejidad del autotest en la etapa pre-bond aparece cuando solo uno de los terminales de la TSV es accesible. En el documento de patente US2011080185A1 se propone un método que consiste en poner una cierta carga en la TSV i posteriormente descargarla. La presencia del defecto se comprueba midiendo la constante de tiempo de la descarga y comparándola con unos umbrales preestablecidos. Las principales limitaciones de esta propuesta son que solo detecta defectos que modifiquen sustancialmente la capacidad asociada a la TSV y que las variaciones de proceso modifican la constante de tiempo, con la consiguiente influencia en el resultado del test. Otro método propuesto se encuentra en el documento “Through silicon via (TSV) defect/pinhole self test circuit for 3D-IC”, M. Tsai et al, IEEE International Conference on 3D System Integration, pp. 1-8, 2009”. Esta propuesta se basa en medir la corriente de fugas (leakage current) de la TSV. Idealmente, como la TSV está aislada esta corriente es nula, pero en presencia de un defecto que deteriore el óxido (aislante) , la resistencia entre la TSV i el sustrato se reduce, aumentando la corriente de fugas. Las principales limitaciones de esta propuesta son que solo detecta defectos que generen un aumento importante de corriente i que el tiempo necesario para realizar el test es elevado, en el orden de microsegundos.

Por lo presentado en el párrafo anterior, se pone de manifiesto la necesidad de desarrollar un circuito de autotest para la detección de defectos en TSVs, incluidos defectos suaves (“weak defects”) , es decir, aquellos que generan conexiones o desconexiones parciales no deseadas, los cuales no son detectados de manera eficiente por el estado actual de la técnica. Además, se requiere que el circuito de autotest realice el test en poco tiempo, que ocupe poca área y pueda reutilizarse, en caso necesario, para la posterior reconfiguración del circuito, minimizando así el área extra ocupada por el circuito.

DESCRIPCIÓN

La presente invención se refiere a un sistema autotest integrado para la detección de defectos en estructuras TSVs durante la fase pre-bond, durante la cual solo uno de los terminales de la TSV es accesible. Esta invención permite a su vez que la misma estructura se utilice posteriormente para la reconfiguración del circuito al final del proceso de fabricación si el resultado del test determina la presencia de una TSV defectuosa.

La presente invención consiste en utilizar un elemento con al menos dos estados estables (elemento multiestable) , como mínimo una TSV, un elemento de referencia y dos circuitos de carga. Un terminal del elemento multiestable y un circuito de carga están conectados al terminal accesible de una TSV. El otro terminal del elemento multiestable y el otro circuito de carga están conectados al elemento de referencia. El elemento de referencia deber tener un comportamiento eléctrico similar al de una TSV. Por tanto, este elemento puede ser a su vez otra TSV.

La metodología para el autotest consiste primero en deshabilitar el elemento multiestable. Segundo, precargar los dos terminales del elemento multiestable a un mismo estado conocido. Tercero, dejar el sistema en alta impedancia. Cuarto, habilitar el elemento multiestable para que evolucione hasta alcanzar la estabilidad y quinto, observar el estado del sistema para determinar el resultado del test. En presencia de una TSV no defectuosa, el elemento multiestable evoluciona hacia un mismo estado estable predefinido. En presencia de un defecto, este elemento bascula hacia otro estado. El resultado del test se puede observar a través de cualquiera de los terminales del elemento multiestable.

En presencia de un defecto, la implementación de la invención permite la reconfiguración del sistema. El elemento multiestable, con señales de habilitación, permite transmitir la señal a través del elemento de referencia y no a través de la TSV defectuosa.

BREVE DESCRIPCIÓN DE LOS DIBUJOS

La Figura 1 muestra la sección de una TSV típica así como su modelo eléctrico equivalente. Como la TSV es metálica, su resistencia es muy pequeña. Por este motivo su comportamiento eléctrico se modela como una capacidad entre la TSV i el sustrato.

La Figura 2 muestra la estructura de una TSV defectuosa afectada por la perforación del aislante que cortocircuita el metal y el sustrato. Al perforarse el material que aísla la TSV del sustrato, aparece una conexión entre estas dos capas.

La Figura 3 muestra la estructura de una TSV afectada por un hueco que debería estar relleno de metal. La aparición del hueco provoca que la resistencia de la TSV no sea despreciable.

La Figura 4 describe los elementos...

Reivindicaciones:

Circuito de autotest integrado de TSVs (Through Silicon Vias) que comprende:

• al menos una TSV (Through-Silicon Via o vía a través de silicio) , con uno de sus terminales aislado,

• un elemento de referencia capacitivo con un comportamiento eléctrico similar al de una TSV,

• un elemento multiestable con sus terminales conectados entre el elemento de referencia y el terminal de la TSV que no está aislado,

• dos circuitos de carga, uno para precargar la TSV y el otro para precargar el elemento de referencia.

2. Circuito de autotest integrado según la reivindicación 1 caracterizado porque el elemento multiestable es un biestable formado por dos inversores realimentados.

3. Circuito de autotest integrado según la reivindicación 1 caracterizado porque el elemento multiestable es un biestable formado por dos inversores realimentados con control de alta impedancia.

4. Circuito de autotest integrado según reivindicación 1 caracterizado porque el circuito de carga es un inversor.

5. Circuito de autotest integrado según reivindicación 1 caracterizado porque el circuito de carga es un inversor con control de alta impedancia.

6. Circuito de autotest integrado según reivindicación 1 caracterizado porque el elemento de referencia es una TSV.

7. Circuito para el autotest integrado según la reivindicación 1 que contiene un elemento selector para poder diferenciar entre el modo de funcionamiento normal y el modo de test, el elemento selector puede consistir en un multiplexor.

9. Circuito para el autotest integrado según las reivindicaciones 1, 3 y 5 caracterizado porque comprende:

• al menos dos TSVs,

• al menos tantos elementos biestables como TSVs,

• un elemento de referencia capacitivo con un comportamiento eléctrico similar al de una TSV,

• al menos el mismo número más uno de circuitos de carga que de TSVs, de manera que un único elemento de referencia se utiliza para realizar el test de todas las TSVs.

10. Circuito para el autotest integrado y reconfiguración de TSVs según las reivindicaciones 1, 3, 6 y 9 caracterizado porque comprende al menos dos elementos biestables con señales independientes de control de alta impedancia para cada inversor, deshabilitadas dichas señales durante el funcionamiento normal en el caso de que las TSVs no sean defectuosas, y habilitada una de ellas para un biestable en presencia de la correspondiente TSV defectuosa, de manera que se propaga los datos a través de la TSV que actúa como elemento de referencia y no a través de la TSV defectuosa.

11. Método de autotest integrado de TSVs caracterizado porque comprende las siguientes etapas:

• deshabilitarel elemento multiestable,

• precargar, mediante los circuitos de carga, los dos terminales del elemento multiestable a un estado conocido,

• aislar el sistema,

• habilitar el elemento multiestable para que el sistema evolucione hasta llegar al estado estable, • observar el estado final alcanzado por el elemento multiestable para determinar el resultado del test.

Figura 1

Figura 2

Figura 3

42b 42a Figura 4

51

55

Figura 5

Figura 6

t

Figura 7

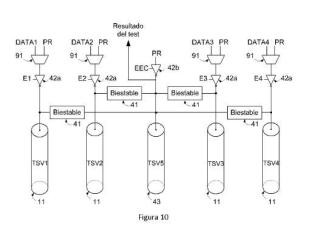

Resultado del test

PR DATA

Resultado del test

Resultado del test

42a Figura 10

PR

DATA 91

PR

DATA

PR

42b 43 Figura 12

Patentes similares o relacionadas:

Dispositivo para la puesta en contacto de potencia, del 8 de Abril de 2020, de Leukert GmbH: Dispositivo para la puesta en contacto de potencia, que presenta una espiga de contacto y al menos un alojamiento de espiga de contacto atravesado por esta en el […]

Relé de protección digital, del 20 de Noviembre de 2019, de LSIS Co., Ltd: Un relé de protección digital, que comprende: al menos una placa de circuito impreso hija que tiene un circuito electrónico que genera […]

Dispositivo de interconexión para circuitos electrónicos, en particular circuitos electrónicos de hiperfrecuencia, del 16 de Octubre de 2019, de THALES: Dispositivo de interconexión de elementos a interconectar tales como módulos o circuitos electrónicos, que comprende al menos una línea de transmisión […]

Disposición de circuitos para automóviles y uso de una disposición de circuitos, del 3 de Julio de 2019, de AUTO-KABEL MANAGEMENT GMBH: Disposición de circuitos para automóviles con - al menos dos componentes semiconductores y - al menos una primera placa de soporte metálica […]

Aparato electrónico, del 29 de Mayo de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un aparato electrónico, en donde el aparato electrónico comprende un cuerpo principal , un módulo de pantalla de visualización , una batería […]

Aparato electrónico, del 29 de Mayo de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un aparato electrónico, en donde el aparato electrónico comprende un cuerpo principal , un módulo de pantalla de visualización , una batería […]

Dispositivo de protección de un componente electrónico, del 4 de Marzo de 2019, de Ingenico Group: Sistema electrónico que comprende: un circuito impreso que incluye unas caras opuestas , primera y segunda, y al menos […]

Dispositivo de representación con diodo orgánico emisor de luz de matriz activa de panel de pantalla táctil con placa de circuito impreso flexible, del 30 de Enero de 2019, de SAMSUNG ELECTRONICS CO., LTD.: Un dispositivo de representación con Diodo Orgánico Emisor de Luz de Matriz Activa, AMOLED, de panel de pantalla táctil, comprendiendo el dispositivo: Una pantalla […]

Placa de circuitos impresos, circuito impreso y procedimiento para la fabricación de un circuito impreso, del 28 de Noviembre de 2018, de AUTO-KABEL MANAGEMENT GMBH: Placa de circuito impreso (2a) con - una placa de soporte metálica , - una capa aislante que aísla eléctricamente la placa de soporte metálica […]