Sistema de transmisión de múltiples frecuencias para datos de entrada paralelos.

Método para enviar y recibir datos que comprende:

- almacenar temporalmente datos paralelos en una primera memoria intermedia basándose en un reloj dedatos paralelos recibidos;

- leer dichos datos paralelos de dicha primera memoria intermedia a una frecuencia que impide undesbordamiento y subdesbordamiento de dicha primera memoria intermedia;

- generar información relacionada con dicho reloj de datos paralelos y generar caracteres de controlcuando los datos no se leen desde dicha memoria intermedia;

- almacenar dicha información relacionada con dicho reloj de datos paralelos y dichos caracteres decontrol; y

- serializar dichos datos paralelos leídos, dicha información relacionada con dicho reloj de datos paralelosy dichos caracteres de control en un flujo de datos en serie;

- transmitir dichos datos serializados;

- recibir y deserializar dichos datos serializados;

- determinar al menos una aproximación de dicho reloj de datos paralelos a partir de la informaciónrelacionada con dicho reloj de datos paralelos;

- almacenar dichos datos deserializados en forma paralela en una segunda memoria intermediabasándose en dicha aproximación determinada de dicho reloj de datos paralelos; y

- leer dichos datos paralelos de dicha segunda memoria intermedia en dicha aproximación de dicho relojde datos paralelos para impedir un desbordamiento y subdesbordamiento de dicha segunda memoriaintermedia.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/IB2009/000393.

Solicitante: Thinklogical, LLC.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 100 Washington Street Milford, CT 06460 ESTADOS UNIDOS DE AMERICA.

Inventor/es: REMLIN,MARK, ENGLER,MICHAEL.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F13/40 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 13/00 Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16). › Estructura del bus.

- G06F13/42 G06F 13/00 […] › Protocolo de transferencia para bus, p. ej. interbloqueo; Sincronización.

PDF original: ES-2430387_T3.pdf

Fragmento de la descripción:

Sistema de transmisión de múltiples frecuencias para datos de entrada paralelos Sector de la técnica La presente invención se refiere a sistemas de transmisión de datos, en particular, a sistemas de transmisión para transferir datos paralelos que proceden de una ubicación a una segunda ubicación remota, para replicar dichos datos paralelos en la ubicación remota.

Estado de la técnica

Se han usado sistemas de transmisión para transferir datos paralelos de una ubicación a una segunda ubicación remota en lo que a veces se denominan extensores de vídeo en los que los datos que proceden de un puerto de salida de vídeo en un ordenador o similar se transfieren a una ubicación remota para presentarse visualmente en un monitor remoto. Ha habido la necesidad de permitir que tales datos paralelos se transfieran independientemente de la frecuencia de reloj de datos paralelos (por ejemplo asociado con diferentes resoluciones de vídeo y frecuencias de actualización) de una manera que se facilite de manera sencilla.

La presente invención se refiere a un sistema de transmisión mejorado de este tipo y se refiere específicamente a un sistema de transmisión de múltiples frecuencias, en el que la frecuencia de reloj de datos paralelos se transfiere en el mismo flujo de datos en serie que los datos paralelos serializados.

El documento US 2003/0091039 da a conocer un aparato para permitir la transmisión de datos paralelos desde un primer bus paralelo a un segundo bus paralelo a través de un canal de datos en serie que incluye un primer elemento lógico que genera un carácter de sincronización usado en un protocolo de transmisión de datos en serie tras la detección de un paquete de sincronización paralelo. Un serializador convierte los datos del primer elemento lógico en un flujo de datos en serie. Un deserializador convierte el flujo de datos en serie en una pluralidad de paquetes de datos paralelos. Un segundo elemento lógico detecta el carácter de sincronización y convierte el carácter de sincronización en un paquete de sincronización paralelo.

Objeto de la invención En una realización de la presente invención, un sistema de transmisión de múltiples frecuencias envía datos desde una primera ubicación a una segunda ubicación mientras que puede ajustarse a diferentes frecuencias de reloj de datos paralelos de los datos paralelos entrantes. En un método y un sistema de este tipo, los datos paralelos se reciben con un reloj de datos paralelos asociado y se almacenan temporalmente en una memoria intermedia. Los datos se escriben en la memoria intermedia a la frecuencia del reloj de datos paralelos. En esta realización, los datos se extraen mediante lectura de la memoria intermedia a una frecuencia de salida para impedir que la memoria intermedia se desborde o subdesborde. Normalmente, la frecuencia de reloj de lectura es mayor que la frecuencia de reloj de escritura y por tanto durante periodos de tiempo en los que no van a leerse los datos, se generan caracteres de control para tales ciclos de reloj. Los datos paralelos y caracteres de control globales se transfieren a un serializador para generar un flujo de datos de salida en serie que puede transmitirse a una ubicación remota mediante diversos medios, tal como a través de un medio óptico. Los datos serializados contienen además información relacionada con la frecuencia de reloj de datos paralelos. En la ubicación remota, los datos serializados se deserializan y se convierten de vuelta a la forma paralela y se almacenan en una memoria intermedia. Los datos en la memoria intermedia se extraen mediante lectura para impedir un desbordamiento y subdesbordamiento. Los datos paralelos se extraen mediante lectura de la memoria intermedia a una frecuencia de reloj de datos paralelos basándose en la frecuencia de reloj de datos paralelos recibida en el flujo de datos en serie. La salida de la memoria intermedia corresponde de ese modo a los datos paralelos recibidos en la parte de transmisor del sistema de transmisión de múltiples frecuencias. El sistema de transmisión de múltiples frecuencias además puede codificar y decodificar los datos paralelos y caracteres de control antes de enviar los datos en el flujo de datos en serie con decodificación en el momento de deserialización.

Una realización de la invención está adaptada específicamente para transmitir vídeo según la norma de entrada de vídeo digital (DVI) .

En una realización de la presente invención, se genera un carácter de control particular mediante la parte de transmisor para indicar los límites de los datos paralelos que van a serializarse y este carácter de control se usa para recuperar los datos paralelos en la parte de receptor del sistema de transmisión.

Una realización del sistema de transmisión de múltiples frecuencias puede transmitir y recibir datos paralelos de DVI que oscilan entre 25 MHz y 165 MHz.

Una realización del sistema de transmisión determina el número de palabras de datos paralelos (es decir, ciclos de reloj de datos paralelos) que se reciben por el transmisor durante un periodo de tiempo predeterminado, en el que la información con respecto a esta recuento se incluye en los datos serializados enviados a la parte de receptor del sistema de transmisión de múltiples frecuencias para determinar la frecuencia de reloj de datos paralelos en la parte de receptor. La invención es según se define en la reivindicación 1 independiente adjunta del método y las reivindicaciones 9 y 10 del aparato.

Descripción de las figuras Para un mayor entendimiento de la naturaleza y los objetos de la presente invención, se hará referencia a la siguiente descripción detallada tomada en conjunto con los siguientes dibujos en los que:

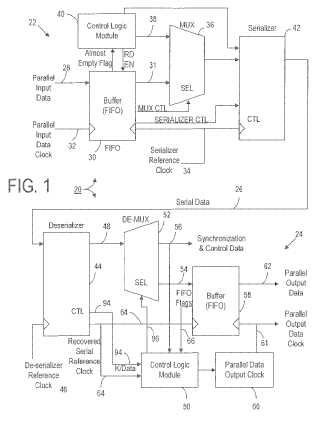

La figura 1 es un diagrama de bloques simplificado global de un sistema de transmisión de múltiples frecuencias según la presente invención.

La figura 2 es un diagrama de bloques de la transmisión de la parte de transmisor del sistema de transmisión de múltiples frecuencias.

La figura 3 es un diagrama de bloques de la parte de receptor del sistema de transmisión de múltiples frecuencias.

Descripción detallada de la invención Tal como se observa en la figura 1, un sistema (20) de transmisión de múltiples frecuencias comprende una parte (22) de transmisor y una parte (24) de receptor enlazadas entre sí mediante un enlace (26) de datos en serie, tal como una fibra óptica, cable coaxial, enlace de radio, etc. La parte (22) de transmisor recibe datos (28) de entrada paralelos entrantes que están almacenados temporalmente en una memoria intermedia (30) , tal como una memoria intermedia primero en entrar/primero en salir (FIFO) . La memoria intermedia puede implementare de diversas maneras, incluyendo el uso de una memoria de acceso aleatorio, registros y similares. Los datos paralelos entrantes se registran en la memoria intermedia (FIFO) (30) por medio de un reloj (32) de datos paralelos.

Los datos en la FIFO se extraen mediante lectura de la FIFO en el bus (31) por medio de un reloj (34) de referencia de serializador que tiene una frecuencia mayor que el reloj (32) de datos paralelos. El multiplexor (36) recibe datos de sincronización y control en el bus (38) generados por un módulo (40) de control junto con datos paralelos en el bus (31) extraídos mediante lectura de la memoria intermedia (30) . El módulo de control también se interconecta con la FIFO (30) y el serializador (42) .

Los datos de sincronización y control se reciben durante periodos de tiempo en los que los datos paralelos no se leen desde la FIFO (30) . Por tanto, los datos de entrada globales al multiplexor se registran en el multiplexor a la frecuencia de reloj de referencia de serializador siendo los datos o bien los datos paralelos desde la FIFO (30) o bien los datos de sincronización y control desde el módulo (40) de control. El multiplexor (36) determina si los datos desde el bus (31) ó (38) se transfieren al serializador (42) .

Por tanto, la salida del multiplexor se proporciona al serializador (42) bajo el control del módulo (40) de control en conjunto con el reloj (34) de referencia de serializador para generar un flujo de datos en serie para su presentación en el enlace (26) en serie. El enlace en serie puede ser de cualquier longitud que sea necesaria para comunicarse en un extremo remoto en el que está ubicada la parte (24) de receptor del sistema (20) de transmisión de múltiples frecuencias. La frecuencia de reloj de serializador se selecciona para poder transmitir los datos de salida en serie recibidos del multiplexor (36) .

La parte (24) de receptor del sistema (20) de transmisión de múltiples frecuencias realiza eficazmente la operación inversa de la parte de transmisor.... [Seguir leyendo]

Reivindicaciones:

1. Método para enviar y recibir datos que comprende:

- almacenar temporalmente datos paralelos en una primera memoria intermedia basándose en un reloj de datos paralelos recibidos;

- leer dichos datos paralelos de dicha primera memoria intermedia a una frecuencia que impide un desbordamiento y subdesbordamiento de dicha primera memoria intermedia;

- generar información relacionada con dicho reloj de datos paralelos y generar caracteres de control cuando los datos no se leen desde dicha memoria intermedia;

- almacenar dicha información relacionada con dicho reloj de datos paralelos y dichos caracteres de 10 control; y

- serializar dichos datos paralelos leídos, dicha información relacionada con dicho reloj de datos paralelos y dichos caracteres de control en un flujo de datos en serie;

- transmitir dichos datos serializados;

- recibir y deserializar dichos datos serializados;

- determinar al menos una aproximación de dicho reloj de datos paralelos a partir de la información relacionada con dicho reloj de datos paralelos;

- almacenar dichos datos deserializados en forma paralela en una segunda memoria intermedia basándose en dicha aproximación determinada de dicho reloj de datos paralelos; y

- leer dichos datos paralelos de dicha segunda memoria intermedia en dicha aproximación de dicho reloj

de datos paralelos para impedir un desbordamiento y subdesbordamiento de dicha segunda memoria intermedia.

2. Método según la reivindicación 1, caracterizado porque un reloj de referencia de serializador opera a una frecuencia de serializador mayor que la frecuencia del reloj de datos paralelos y, porque se generan caracteres de control en dicha frecuencia de serializador siempre que no se lean datos paralelos de dicha primera memoria intermedia.

3. Método según la reivindicación 1 ó 2, caracterizado porque la información relacionada con dicho reloj de datos paralelos se basa en la relación de dichos caracteres de control con dichos datos paralelos.

4. Método según la reivindicación 2, caracterizado porque la información relacionada con dicho reloj de datos

paralelos se basa en varias palabras de datos paralelos recibidas durante una duración de tiempo 30 predeterminada.

5. Método según la reivindicación 4, caracterizado porque la determinación de una aproximación del reloj de datos paralelos se realiza recuperando dicho número de palabras de datos paralelos recibidas durante una duración de tiempo predeterminada a partir de datos deserializados, y comparando una frecuencia de reloj derivada con un reloj generado localmente, y ajustando dicho reloj generado localmente basándose en dicha comparación.

6. Método según la reivindicación 5, caracterizado porque el ajuste se realiza en aumentos ajustables basándose en un tamaño de dicha comparación.

7. Método según la reivindicación 1 ó 2, caracterizado porque comprende además:

codificar dichos datos paralelos, dicha información relacionada con dicho reloj de datos paralelos y

caracteres de control basándose en un esquema de codificación, y serializar dichos datos paralelos codificados, dicha información relacionada con dicho reloj de datos paralelos y dichos caracteres de control codificados, y que comprende además deserializar dichos datos paralelos codificados, dicha información relacionada con dicho reloj de datos paralelos y dichos caracteres de control codificados y decodificar dichos datos paralelos codificados deserializados, dicha información relacionada con dicho 45 reloj de datos paralelos y dichos caracteres de control codificados deserializados basándose en un esquema de decodificación que corresponde a dicho esquema de codificación.

8. Método según la reivindicación 2, caracterizado porque al menos algunos de los caracteres de control se usan para determinar la ubicación de los datos paralelos en relación con otros datos deserializados.

9. Aparato para enviar datos que comprende:

una memoria intermedia para recibir datos paralelos basándose en un reloj de datos paralelos;

un módulo de control para controlar la lectura de datos desde la memoria intermedia para impedir un desbordamiento y subdesbordamiento, para generar información relacionada con dicho reloj de datos paralelos y para generar caracteres de control cuando los datos no se leen desde la memoria intermedia;

un multiplexor para almacenar la información de datos paralelos relacionada con dicho reloj de datos paralelos y dichos caracteres de control;

un serializador, en participación conjunta con dicho multiplexor, para convertir los datos paralelos, la información relacionada con dicho reloj de datos paralelos y los caracteres de control en un flujo de datos en serie para su transmisión; y

un transmisor de datos en serie para transmitir dicho flujo de datos en serie.

10. Aparato para recibir datos que comprende:

un receptor de datos en serie para recibir un flujo de datos en serie;

un deserializador para convertir dicho flujo de datos en datos paralelos, caracteres de control e información relacionada con un reloj de datos paralelos;

un demultiplexor para recibir los datos paralelos e información relacionada con dicho reloj de datos paralelos;

una memoria intermedia para recibir los datos paralelos del demultiplexor; y

un módulo de control para recibir los caracteres de control del deserializador, para controlar la transferencia de datos paralelos al demultiplexor, para controlar la escritura de datos paralelos en la memoria intermedia y para controlar la generación de al menos una aproximación de dicho reloj de datos paralelos basándose en dicha información relacionada con dicho reloj de datos paralelos de modo que los datos paralelos se leen desde la memoria intermedia en dicha aproximación de dicho reloj de datos paralelos para impedir un desbordamiento y subdesbordamiento de dicha memoria intermedia.

11. Sistema para enviar y recibir datos que comprende:

el aparato para enviar datos según la reivindicación 9; y

una parte de receptor que tiene:

un receptor de datos en serie para recibir dicho flujo de datos en serie;

un deserializador para convertir dicho flujo de datos en dichos datos paralelos, dichos caracteres de control y dicha información relacionada con dicho reloj de datos paralelos;

un demultiplexor para recibir los datos paralelos e información relacionada con dicho reloj de datos paralelos;

una segunda memoria intermedia para recibir los datos paralelos del demultiplexor; y

un módulo de control para recibir los caracteres de control del deserializador, para controlar la transferencia de datos paralelos al demultiplexor, para controlar la escritura de datos paralelos en la segunda memoria intermedia y para controlar la generación de al menos una aproximación de dicho reloj de datos paralelos basándose en dicha información relacionada con dicho reloj de datos paralelos de modo que los datos paralelos se leen de la segunda memoria intermedia en dicha aproximación de dicho reloj de datos paralelos para impedir un desbordamiento y subdesbordamiento de dicha segunda memoria intermedia.

12. Sistema según la reivindicación 11, caracterizado porque dicha información relacionada con dicho reloj de datos paralelos se determina contando varios ciclos de reloj de datos paralelos recibidos por la memoria intermedia durante una duración de tiempo predeterminada y transfiriendo esta información al serializador para su transmisión en el flujo de datos en serie.

13. Sistema según la reivindicación 12, caracterizado porque el serializador codifica los datos paralelos, la 45 información relacionada con dicho reloj de datos paralelos y los caracteres de control antes de serializar dichos datos paralelos, dicha información relacionada con dicho reloj de datos paralelos y dichos caracteres de control.

14. Sistema según la reivindicación 11, caracterizado porque la información relacionada con dicho reloj de datos paralelos se determina basándose en una relación de los datos paralelos con caracteres de control.

15. Sistema según la reivindicación 11, caracterizado porque el transmisor de datos en serie y dicho receptor de datos en serie son respectivamente un transmisor óptico y un receptor óptico.

16. Sistema según la reivindicación 11, caracterizado porque un reloj de referencia de envío está configurado para operar a una frecuencia de serializador mayor que la frecuencia del reloj de datos paralelos, y en el que se generan caracteres de control en dicha frecuencia de serializador siempre que no se lean datos paralelos de dicha primera memoria intermedia.

Patentes similares o relacionadas:

Aparato para establecer la dirección de un módulo utilizando un reloj, del 17 de Junio de 2020, de LEXMARK INTERNATIONAL, INC.: Un circuito integrado específico de la aplicación (ASIC) que comprende: un pin de alimentación; un pin de masa; un pin de reloj I2C; un pin […]

Método para implementar un bus industrial de banda ancha de campo de internet, del 17 de Junio de 2020, de Kyland Technology Co., Ltd: Un método para implementar un bus industrial de banda ancha de campo de internet, caracterizado por que, el método es aplicable a un sistema de arquitectura […]

Sistema de arquitectura de bus de banda ancha de campo de internet de la industria, del 3 de Junio de 2020, de Kyland Technology Co., Ltd: Un sistema de arquitectura de bus de banda ancha de campo de Internet de la industria, caracterizado por que, el sistema comprende un controlador de bus […]

Método para gestionar la configuración del bus de banda ancha del campo de internet industrial, del 3 de Junio de 2020, de Kyland Technology Co., Ltd: Un método para gestionar la configuración de un bus de banda ancha del campo de internet industrial, caracterizado por que, el método es aplicable a […]

Método para implementar un bus de campo en tiempo real de banda ancha de Internet industrial, del 29 de Abril de 2020, de Kyland Technology Co., Ltd: Un método para implementar un bus de campo en tiempo real de banda ancha de Internet industrial, en donde el método puede aplicarse a una red de transferencia […]

Procedimiento para hacer funcionar un sistema de transmisión de datos y sistema de transmisión de datos, del 29 de Abril de 2020, de Siemens Mobility GmbH: Procedimiento para hacer funcionar un sistema de transmisión de datos en el que - un primer equipo de transmisión de datos está conectado […]

Método y aparato para detectar contrapresión de mensajes, del 8 de Abril de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de detección de contrapresión de paquetes, en donde el método se aplica a un dispositivo que tiene un puerto de Interconexión de […]

Sistema de autenticación e información para instrumentos quirúrgicos reutilizables, del 8 de Abril de 2020, de Covidien LP (100.0%): Un método para comunicar datos a través de un bus, el método que comprende: autenticar un componente quirúrgico utilizando un microchip […]