Dispositivo de restauración de datos de reloj.

Un dispositivo (1) de restauración de datos de reloj, que restaura la señal y los datos de reloj sobre la base de una señal digital introducida,

que comprende:

una sección (10) de ecualizador que ajusta un nivel de la señal digital introducida y emite la señal digital ajustada;

una sección (20) de muestreador que recibe una entrada de una señal CK de reloj y una señal CKX de reloj que tienen un mismo ciclo T, así como una entrada de señal digital emitida por la sección (10) de ecualizador, y que muestrea, mantiene y emite, en cada período enésimo T(n) del ciclo, un valor D(n) de la señal digital en un tiempo tC, indicado por la señal CK de reloj, y un valor DX(n) de la señal digital en un tiempo tX, indicado por la señal CKX de reloj (donde tC

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/JP2007/067397.

Solicitante: Thine Electronics, Inc.

Nacionalidad solicitante: Japón.

Dirección: 9-1 Kanda-mitoshiro-cho 101-0053 Chiyoda-ku, Tokyo JAPON.

Inventor/es: OZAWA,SEIICHI.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03L7/00 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03L CONTROL AUTOMATICO, ARRANQUE, SINCRONIZACION O ESTABILIZACION DE GENERADORES DE OSCILACIONES O DE IMPULSOS ELECTRONICOS (de generadores dinamoeléctricos H02P). › Control automático de frecuencia o fase; Sincronización (sintonización de circuitos resonantes en general H03J; sincronización en los sistemas de comunicación digital, ver los grupos apropiados en la clase H04).

- H04B3/06 H […] › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04B TRANSMISION. › H04B 3/00 Sistemas de líneas de transmisión (combinados con sistemas de transmisión de campo cercano H04B 5/00). › por señal transmitida.

- H04L25/03 H04 […] › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › H04L 25/00 Sistemas de banda base. › Redes de formación para emisor o receptor, p. ej. redes de formación adaptables.

- H04L7/033 H04L […] › H04L 7/00 Disposiciones para sincronizar el receptor con el emisor. › utilizando las transiciones de la señal recibida para controlar la fase de medios generadores de la señal de sincronización, p. ej. utilizando un bucle con enclavamiento de fase.

PDF original: ES-2529145_T3.pdf

Fragmento de la descripción:

Dispositivo de restauración de datos de reloj

Campo técnico

La presente invención se refiere a un dispositivo para restaurar unos datos y una señal de reloj sobre la base de una señal digital que es introducida.

Antecedentes de la técnica

La forma de onda de una señal digital que es emitida por un transmisor se deteriora mientras que se transmite desde el transmisor a un receptor mediante una trayectoria de transmisión. Por lo tanto, se requiere que unos datos y una señal de reloj sean restaurados en el lado de receptor. Un dispositivo de restauración de datos de reloj para realizar dicha restauración se describe en los documentos de patente 1, 2 y 3, por ejemplo, y en la patente DE 10 2005 022 684 A1.

Un dispositivo general de la restauración de datos de reloj detecta los datos de una señal digital introducida cuya forma de onda se deterioró en el tiempo central de cada período de bitios (el valor detectado se denota D (n) ) y en un tiempo de transición desde un cierto bitio hasta el siguiente bitio (el valor detectado se denota DX (n) ) . Además, el dispositivo de restauración de datos de reloj es capaz de obtener la señal y los datos restaurados de reloj mediante el ajuste, basado en los valores D (n) y en el valor DX (n) , del ciclo o fase de la señal de reloj, de manera que la diferencia de fase entre la señal digital introducida y la señal de reloj que indica la disposición temporal en la que estos valores son detectados se reduce.

Además, se conoce un dispositivo de restauración de datos de reloj que comprende una sección de ecualizador que ajusta el nivel de la señal digital introducida antes de la emisión misma. La sección de ecualizador compensa la pérdida a la que es sometida la señal digital introducida mientras que es transmitida desde el transmisor al receptor mediante la trayectoria de transmisión al ajustar el nivel de la señal digital introducida. El dispositivo de restauración de datos de reloj detecta el valor D (n) y el valor DX (n) de la señal digital cuyo nivel se ajusta por la sección de ecualizador.

El documento 4 de patente describe un receptor que comprende una sección de ecualizador que es activado y desactivado sobre la base de una métrica de correlación de señal.

[Documento 1 de patente] Solicitud japonesa de patente, abierta, nº H7-221800 [Documento 2 de patente] Traducción japonesa publicada nº 2004-507963 de la Publicación Internacional PCT [Documento 3 de patente] Traducción japonesa publicada nº 2005-341582 de la Publicación Internacional PCT [Documento 4 de patente] Documento US 2004/240531 A1

Divulgación de la invención

Problema a resolver por la invención 45 Un dispositivo de restauración de datos de reloj que comprende una sección de ecualizador tal de esta clase restaura una señal de reloj por medio de control de fase y de frecuencia sobre la base de una señal de entrada y corrige la forma de onda de señal de entrada por medio de una sección de ecualizador. La intensidad de corrección de la forma de onda de señal de entrada de la sección de ecualizador se ajusta a un nivel óptimo para los casos en que la pérdida que sufre la señal durante la transmisión varía, sobre la base del valor de datos detectado. En otras palabras, el requisito previo para la corrección adecuada de la forma de onda de señal de entrada es la detección precisa de los datos.

Sin embargo, en los casos en que la fase y la frecuencia de la señal de reloj que indica el tiempo de datos de muestreo son desplazadas una cantidad grande con respecto a la señal digital introducida, los datos no pueden ser 55 detectados de manera precisa, y la corrección de la forma de onda con una intensidad adecuada por la sección de ecualizador es problemática. Por lo tanto, los casos en que la corrección de la forma de onda no se realiza con una intensidad adecuada incluyen los casos en que la restauración de la fase y la frecuencia de la señal de reloj se vuelve fácilmente imprecisa.

La presente invención se concibió con el fin de resolver el problema anterior, y un objeto de la presente invención es proporcionar un dispositivo de restauración de datos de reloj que sea capaz de restaurar la señal y los datos de reloj de una manera más precisa.

Medios para resolver el problema 65 El dispositivo de restauración de datos de reloj de acuerdo con la presente invención es un dispositivo que restaura

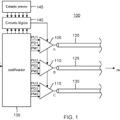

la señal y los datos de reloj sobre la base de una señal digital introducida, que comprende una sección de ecualizador, una sección de muestreador, una sección de generación de reloj, una sección de control de ecualizador, y una sección de monitor de fase.

La sección de ecualizador ajusta el nivel de la señal digital introducida y emite la señal digital ajustada. La sección de muestreador recibe la entrada de una señal CK de reloj y una señal CKX de reloj que tienen el mismo ciclo T, así como la emisión de señal digital por la sección de ecualizador. En cada período enésimo T (n) del ciclo, la sección de muestreador muestrea, mantiene y emite un valor D (n) de la señal digital en un tiempo tC indicado por la señal CK de reloj, y muestrea, mantiene y emite un valor DX (n) de la señal digital en un momento tX indicado por la señal CKX de reloj, donde tC<tX y n es un número entero.

En cada periodo T (n) , la sección de generación de reloj ajusta el ciclo T o la fase de manera que la diferencia de fase entre la señal CK de reloj y la señal digital disminuye sobre la base del valor D (n) y el valor DX (n) , que son emitidos por la sección de muestreador, y emite la señal CK de reloj y la señal CKX de reloj, que satisfacen la relación ' tX-tC = T/2', a la sección de muestreador.

En cada periodo T (n) , la sección de control de ecualizador realiza el control de la cantidad de ajuste de nivel de la señal digital mediante la sección de ecualizador sobre la base del nivel de la señal digital es emitida por la sección de ecualizador, o sobre la base del valor D (n) y del valor DX (n) , que son emitidos por la sección de muestreador el dispositivo de restauración de datos de reloj se caracteriza porque, en cada período T (n) , la sección de monitor de fase detecta la relación de fase entre la señal CK de reloj y la señal digital sobre la base del valor D (n) y del valor DX (n) , que son emitidos por la sección de muestreador y, cuando la diferencia de fase es mayor que un valor predeterminado, detiene el control de la cantidad de ajuste de nivel de la señal digital mediante la sección de control de ecualizador.

La entrada de señal digital al dispositivo de restauración de datos de reloj es ajustada a un primer nivel por la sección de ecualizador e introducida a la sección de muestreador. La señal CK de reloj y la señal CKX de reloj que tienen el mismo ciclo de T son también introducidas en la sección de muestreador. Además, en cada uno de los períodos enésimos T (n) del ciclo, la sección de muestreador muestrea, mantiene y emite el valor D (n) de la señal digital en el tiempo indicado por la señal CK de reloj y muestrea, mantiene y emite el valor DX (n) de la señal digital en el tiempo indicado por la señal CKX de reloj. El valor D (n) y el valor DX (n) que son emitidos por la sección de muestreador son cada uno introducidos en la sección de generación de reloj y la sección de monitor de fase.

La sección de generación de reloj ajusta el ciclo T o la fase sobre la base del valor D (n) y del valor DX (n) emitidos por la sección de muestreador de manera que la diferencia de fase entre la señal CK de reloj y la señal digital disminuye, y emite la señal CK de reloj y la señal CKX de reloj que satisfacen la relación 'tx-tC = T/2' a la sección de muestreador. Como resultado del procesamiento de bucle de la sección de muestreador y la sección de generación de reloj, la señal CK o CKX de reloj se genera como una señal de reloj que se restaura sobre la base de la señal digital introducida.

La sección de control de ecualizador realiza el control de la cantidad de ajuste de nivel de la señal digital mediante la sección de ecualizador sobre la base del nivel de emisión de señal digital emitida por la sección de ecualizador o el valor D (n) y el valor DX (n) que son emitidos por la sección de muestreador. Sin embargo, el control por la sección de control de ecualizador se permite o se detiene sobre la base del resultado de detección de la relación de fase de la 45 sección de monitor de fase. En otras palabras, la sección de monitor de fase detecta la relación de fase entre la señal CK de reloj y la señal digital sobre la base del valor D (n) y del valor DX (n) , que son emitidos por la sección de muestreador.... [Seguir leyendo]

Reivindicaciones:

1. Un dispositivo (1) de restauración de datos de reloj, que restaura la señal y los datos de reloj sobre la base de una señal digital introducida, que comprende:

una sección (10) de ecualizador que ajusta un nivel de la señal digital introducida y emite la señal digital ajustada;

una sección (20) de muestreador que recibe una entrada de una señal CK de reloj y una señal CKX de reloj que tienen un mismo ciclo T, así como una entrada de señal digital emitida por la sección (10) de ecualizador, y que muestrea, mantiene y emite, en cada período enésimo T (n) del ciclo, un valor D (n) de la señal digital en un tiempo tC, indicado por la señal CK de reloj, y un valor DX (n) de la señal digital en un tiempo tX, indicado por la señal CKX de reloj (donde tC<tX y n es un número entero) ;

una sección (30) de generación de reloj que, en cada período T (n) , ajusta el ciclo T o la fase de modo que disminuye la diferencia de fase entre la señal CK de reloj y la señal digital sobre la base del valor D (n) y el valor DX (n) que son emitidos por la sección (20) de muestreador, y que envía la señal CK de reloj y la señal CKX de reloj que satisfacen la relación 'tx-tC = T/2' para la sección (20) de muestreador; y una sección (40) de control de ecualizador que, en cada período T (n) , realiza el control de una cantidad de ajuste de nivel de la señal digital por la sección (10) de ecualizador sobre la base del nivel de la señal digital que es emitida por la sección (10) de ecualizador, o sobre la base del valor D (n) y el valor DX (n) que son emitidos por la sección (20) de muestreador;

caracterizado porque el dispositivo (1) de restauración del reloj comprende adicionalmente:

una sección (50) de monitor de fase que, en cada período T (n) , detecta una diferencia de fase entre la señal CK de reloj y la señal digital sobre la base del valor D (n) y el valor DX (n) , que son emitidos por la sección (20) de muestreador, y que, cuando la diferencia de fase es mayor que un valor predeterminado, detiene el control de la cantidad de ajuste de nivel de la señal digital por la sección (40) de control de ecualizador.

2. El dispositivo (1) de restauración de datos de reloj de acuerdo con la reivindicación 1, en el que la sección (30) de generación de reloj ajusta el ciclo T o la fase sobre la base de una señal UP, que es un valor significativo cuando 'D (n-1) â DX (n-1) = D (n) â? y una señal DN que es un valor significativo cuando â?D (n-1) = DX (n-1) â D (n) ', y emite la señal CK de reloj y la señal CKX de reloj.

3. El dispositivo (1) de restauración de datos de reloj de acuerdo con la reivindicación 1, en el que la sección (50) de monitor de fase detecta la relación de fase entre la señal CK de reloj y la señal digital sobre la base de una señal UP, que es un valor significativo cuando 'D (n-1) â DX (n-1) = D (n) â? y una señal DN que es un valor significativo cuando â?D (n-1) = DX (n-1) â D (n) '.

4. El dispositivo (1) de restauración de datos de reloj de acuerdo con la reivindicación 3, en el que, en cada período T (n) , la sección (50) de monitor de fase considera que la diferencia de fase es mayor que un valor predeterminado cuando ya sea la señal UP o la señal DN no es un valor significativo en diez períodos anteriores consecutivos (T (n9) a T (n) ) que incluyen el período, y detiene el control de la cantidad de ajuste de nivel de la señal digital por la 45 sección de control de ecualizador.

Patentes similares o relacionadas:

Ecualización inteligente para un sistema multifásico de tres transmisores, del 29 de Julio de 2020, de QUALCOMM INCORPORATED: Un sistema de tres transmisores para transmitir símbolos multifásicos sucesivos, que comprende:

un codificador configurado para codificar […]

Ecualización inteligente para un sistema multifásico de tres transmisores, del 29 de Julio de 2020, de QUALCOMM INCORPORATED: Un sistema de tres transmisores para transmitir símbolos multifásicos sucesivos, que comprende:

un codificador configurado para codificar […]

Información de control en un sistema de comunicación inalámbrica, del 15 de Julio de 2020, de QUALCOMM INCORPORATED: Un procedimiento para enviar datos de tráfico e información de control en un sistema de comunicación inalámbrica, que comprende: realizar conformación de haces […]

Asignación dinámica de recursos ACK en un sistema de comunicación inalámbrica, del 15 de Abril de 2020, de QUALCOMM INCORPORATED: Un procedimiento para comunicación inalámbrica, que comprende: recibir una asignación semipersistente para un recurso de acuse de recibo, ACK, para un equipo de usuario, […]

Asignación dinámica de recursos ack en un sistema de comunicación inalámbrica, del 15 de Abril de 2020, de QUALCOMM INCORPORATED: Un procedimiento para comunicación inalámbrica, que comprende: recibir una asignación semipersistente para un equipo de usuario, UE, siendo válida […]

Señal de sincronización extendida para la detección de índice de símbolos, del 15 de Abril de 2020, de QUALCOMM INCORPORATED: Un procedimiento de comunicación inalámbrica, que comprende: determinar una primera secuencia de señal de sincronización extendida, […]

Método y dispositivo para cuantificar y retroalimentar la información de canal y precodificar datos, del 8 de Abril de 2020, de ZTE CORPORATION: Un método para cuantificar y retroalimentar la información de canal en un sistema polarizado doble, caracterizado porque comprende: recibir una señal piloto de […]

Transmisor con equilibrio de polarización, del 1 de Abril de 2020, de Tianma Micro-Electronics Co., Ltd: Un transmisor que comprende: un generador de datos de señalización L1 (Capa 1), configurado para generar datos de señalización […]

Asignación dinámica de recursos ACK en un sistema de comunicación inalámbrica, del 25 de Marzo de 2020, de QUALCOMM INCORPORATED: Un procedimiento para comunicación inalámbrica, que comprende: recibir un primer mensaje de programación que lleve información de programación […]