Componente dotado de un circuito integrado que incluye un criptoprocesador y procedimiento de instalación.

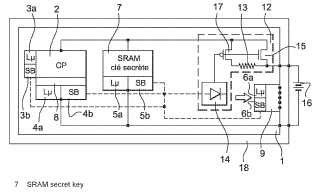

Componente (1) en circuito integrado que incluye un criptoprocesador (2),

caracterizado por incluir una o variasestructuras internas (3a-6b) de activación parásita de tipo activación de un tiristor parásito y/o activación de untransistor bipolar parásito y porque un umbral de energía de activación (10) de las estructuras parásitas, tiristoresparásitos y/o transistores bipolares parásitos, es inferior a una cantidad de energía (11) necesaria para hacercambiar de estado una báscula del componente.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/FR2007/051185.

Solicitante: EUROPEAN AERONAUTIC DEFENCE AND SPACE COMPANY EADS FRANCE.

Nacionalidad solicitante: Francia.

Dirección: 37, BOULEVARD DE MONTMORENCY 75781 PARIS CEDEX 16 FRANCIA.

Inventor/es: MILLER,Florent, BUARD,Nadine, LAHOUD,IMAD, RUBY,CÉDRIC.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03K3/037 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 3/00 Circuitos para la generación de impulsos eléctricos; Circuitos monoestables, biestables o multiestables (H03K 4/00 tiene prioridad; para generadores de funciones digitales en ordenadores G06F 1/02). › Circuitos biestables.

PDF original: ES-2405361_T3.pdf

Fragmento de la descripción:

Componente dotado de un circuito integrado que incluye un criptoprocesador y procedimiento de instalación.

La presente invención tiene por objeto un componente realizado en su totalidad o en parte en forma de un circuito integrado y que dispone de un criptoprocesador, así como su procedimiento de instalación. El componente de la invención está dotado de medios para prevenir la revelación de sus secretos de encriptación. La invención se encamina más en particular a los componentes criptoprocesadores, pero también podría concernir a los circuitos integrados de todo tipo, en los que se pretende impedir que puedan funcionar de una manera inadecuada, ya resulte ese funcionamiento inadecuado de una tentativa deliberada de pervertir su funcionamiento, o bien de la incidencia imprevista de una agresión exterior (eléctrica, electromagnética, térmica, partícula u otro) .

La protección de los datos memorizados en un componente electrónico se lleva a cabo desde siempre mediante cifrado con ayuda de una clave. La clave debe permanecer secreta imperativamente.

En un componente electrónico, un criptoprocesador es un procesador especializado para las operaciones de criptografía. Éste contiene en su parte de memoria una o unas claves que deben mantenerse secretas y que le sirven para cifrar y/o descifrar la información que recibe. Se compone entre otras cosas de una memoria no volátil que almacena la clave de manera permanente cuando se halla sin tensión, de una memoria intermedia volátil (por ejemplo de tipo SRAM o báscula D) dentro de la cual se carga la clave mediante el sistema operativo (si lo hay) en la puesta en tensión y de un circuito lógico de tipo microcontrolador o microprocesador capaz de efectuar las operaciones de cifrado y descifrado de los mensajes con ayuda de la clave secreta.

En los componentes electrónicos, la información se almacena y transita en forma de cargas, que son atrapadas o dirigidas en el seno del material semiconductor, silicio, en virtud de la acción de los campos eléctricos. Un transistor MOS, en el cual se fundamenta la mayoría de los circuitos lógicos y digitales, es de hecho un interruptor que deja transitar o no unas cargas entre su fuente y su drenador, en función de la tensión aplicada en su puerta.

Recientemente ha aparecido una nueva clase de amenaza, encaminada a extraer información contenida en un componente criptoprocesador inyectando en él fallos al propio tiempo que analiza el comportamiento obtenido. Son diversos los métodos utilizables de inyección de fallos (elevación de la temperatura del componente, elevación de la tensión de alimentación del componente, pulsos transitorios, partículas...) . Los métodos que a día de hoy son analizados como los más peligrosos son aquellos que permiten inyectar fallos en los componentes en ubicaciones controladas, por ejemplo en una parte de memoria estática de acceso aleatorio, SRAM, donde se almacena una clave de cifrado. Tal es el caso de los ataques mediante láser o mediante microhaces de iones.

El ataque de un criptoprocesador mediante inyección de fallos consiste en inyectar localmente unas cargas con objeto de modificar u ocultar la información almacenada o en tránsito. El análisis de la respuesta del criptoprocesador como consecuencia de la inyección de fallos proporciona a los piratas indicaciones que les permiten reducir el número de combinaciones e identificar más rápidamente la clave. Tal análisis es tanto más sencillo cuanto más preciso es el ataque, tanto espacial como temporalmente. Existen pues diferentes técnicas de inyección de fallos, con dificultades variables de puesta en práctica, siendo las más eficaces afortunadamente las más difíciles de llevar a la práctica. A título de indicación, las posibles agresiones contra los circuitos integrados están reseñadas en el documento "Memories: a survey of their secure uses in smart cards" a cargo de Michael Neve, Eric Peeters, David Samy de y Jean-Jacques Quisquater; http://www.dice.ucl.ac.be/cr y pto y editado por Second International IEEE Security in Storage, Workshop - Proceedings of SISW 2003.

Las técnicas más simples inyectan fallos de manera aleatoria en el componente: tal es el caso de un ataque mediante elevación de temperatura, u ondas electromagnéticas (radar, microondas, radio) , o mediante partículas (iones, neutrones o protones) . En estos tres casos, el ataque perturba el componente en su conjunto y, si bien es posible determinar un área, no es posible apuntar a un bit ni incluso a varios bits. No obstante, con un tratamiento con soporte lógico y matemático muy avanzado, parece que sea posible explotar los resultados del ataque. El ataque es muy fácil de poner en práctica ya que no precisa de ningún acceso particular y se puede dirigir a distancia.

Luego están los ataques por mediación de las entradas/salidas del circuito, perturbando las tensiones nominales por medio de un generador de tensión. Estos ataques se pueden dirigir en fase (temporalmente) con relación a los ciclos de funcionamiento del reloj del circuito. La consecuencia del ataque sigue siendo bastante aleatoria, lo cual significa que el número de combinaciones que hay que probar para extraer la clave se mantiene elevado, pero esta técnica es bastante fácil de llevar a la práctica si se tiene acceso al circuito.

Finalmente, unas técnicas permiten inyectar fallos en momentos elegidos y en ubicaciones perfectamente controladas (en teoría con una precisión del orden del bit) , lo cual significa que entonces se es capaz por ejemplo de acabar modificando uno a uno los bits que contienen la clave, luego el siguiente y así sucesivamente, o incluso de interrumpir una operación de descifrado. Tal es el caso de los ataques mediante láser o mediante microhaces de iones. Estas técnicas son difíciles de llevar a la práctica, ya que precisan de un acceso al componente, es decir, de

la apertura del encapsulado del componente y la puesta al descubierto del circuito integrado, del chip. Para defenderse de estos ataques, los fabricantes implantan contramedidas más o menos eficaces para impedir el desencapsulado.

Es el propósito de la invención proteger los componentes contra tales ataques.

La activación de un tiristor parásito, llamada latchup, y respectivamente la activación de un transistor bipolar parásito, llamada snapback, son mecanismos que existen de manera inherente en todo componente en circuito integrado de tipo de implantación complementaria, CMOS, o respectivamente no complementaria. Son el resultado de la entrada en conducción de un tiristor, o respectivamente de un transistor bipolar horizontal, parásitos, en respuesta a una introducción local de cargas en el componente. La corriente de alimentación del componente aumenta entonces bruscamente y, debido a la corriente que lo recorre y/o a la caída de tensión de alimentación resultante, el componente deja de ser funcional. En ausencia de limitación de corriente, puede haber una destrucción del circuito por efecto térmico, y es preferible prever una limitación de corriente en la alimentación del circuito. De todas formas, el circuito tan sólo vuelve a ser funcional después de la desconexión de la alimentación y su posterior nueva puesta en tensión. En la continuación de la memoria descriptiva, hablaremos de activación parásita cuando se aluda a la activación de uno u otro de estos fenómenos: activación de un tiristor parásito: latchup y activación de un transistor bipolar parásito: snapback. Estos dos fenómenos están descritos en el documento publicado en 1999 por la Fairchild Semiconductor Corporation y titulado Understanding Latch-up in Advanced CMOS Logic. Un ejemplo para un circuito de protección contra el latchup se da en el documento US6.064.555.

Según la posición de contactos en el componente, el nivel de carga que activa las estructuras parásitas (denominado umbral de latchup o umbral de snapback) puede ser muy variable. Por lo tanto, los fabricantes de componentes intentan en general elevar al máximo este nivel, por cuanto que el mecanismo puede ser activado por un entorno radiativo natural (partículas) , por descargas electrostáticas o incluso por ruido en las entradas o salidas. No obstante, parece más fácil para un fabricante (fabricante de componentes) proyectar una tecnología sensible al latchup/snapback que una tecnología insensible.

Por regla general, se observa que con cada salto de generación, los primeros lotes que se fabrican son sensibles al latchup. A continuación los fabricantes corrigen los procedimientos de fabricación o la arquitectura de los circuitos de los componentes para que esos componentes tengan umbrales de activación más elevados. Así es como se encuentran disponibles... [Seguir leyendo]

Reivindicaciones:

1. Componente (1) en circuito integrado que incluye un criptoprocesador (2) , caracterizado por incluir una o varias estructuras internas (3a-6b) de activación parásita de tipo activación de un tiristor parásito y/o activación de un transistor bipolar parásito y porque un umbral de energía de activación (10) de las estructuras parásitas, tiristores parásitos y/o transistores bipolares parásitos, es inferior a una cantidad de energía (11) necesaria para hacer cambiar de estado una báscula del componente.

2. Componente según la reivindicación 1, caracterizado por incluir un circuito limitador de corriente de alimentación

(12) acoplado al circuito de activación de los tiristores parásitos y/o de activación de los transistores bipolares parásitos de tal manera que, una vez activado este circuito, el componente deja de ser funcional y su alimentación debe ser reinicializada para que funcione de nuevo.

3. Componente según una de las reivindicaciones 1 a 2, caracterizado porque las estructuras de activación de los tiristores parásitos y/o de activación de los transistores bipolares parásitos se hallan situadas en un área de memoria SRAM (7) del componente.

4. Componente según una de las reivindicaciones 1 a 3, caracterizado porque las estructuras de activación de los tiristores parásitos y/o de activación de los transistores bipolares parásitos se hallan situadas en un área de memoria intermedia (8) del componente.

5. Componente según una de las reivindicaciones 1 a 4, caracterizado porque las estructuras de activación de los tiristores parásitos y/o de activación de los transistores bipolares parásitos se hallan situadas en un área combinatoria (2) del componente.

6. Componente según una de las reivindicaciones 1 a 5, caracterizado porque las estructuras de activación de los tiristores parásitos y/o de activación de los transistores bipolares parásitos se hallan situadas en un área (9) de circuitos de entradas y/o de salidas del componente.

7. Procedimiento de instalación de un componente (1) en circuito integrado con criptoprocesador (2) , caracterizado por incluir una operación de selección del componente de un lote de componentes y/o un ajuste de sus parámetros de funcionamiento, en particular su tensión de polarización, siendo el criterio de esta selección y/o ajuste una susceptibilidad del componente a la activación de tiristores parásitos y/o a la activación de transistores bipolares parásitos, siendo esta susceptibilidad superior a un umbral (10) , por incluir en la fabricación una elección de parámetros susceptibles de propiciar la sensibilidad del componente a la activación de un tiristor parásito y/o activación de un transistor bipolar parásito y porque esta elección es tal que un umbral de energía de activación (10) de un tiristor parásito y/o activación de un transistor bipolar parásito es inferior a una cantidad de energía (11) necesaria para hacer cambiar de estado una báscula del componente.

Patentes similares o relacionadas:

Sistema y procedimiento de control condicional de dispositivos de circuito de retención, del 23 de Octubre de 2019, de QUALCOMM INCORPORATED: Un dispositivo de circuito de retención que comprende: una primera entrada para recibir una señal de control de reinicio ; una segunda entrada […]

Dispositivo de memoria que corrige el efecto de colisiones de partículas de alta energía, del 28 de Agosto de 2019, de THALES: Dispositivo de memoria que corrige automáticamente el efecto de colisiones de partículas de alta energía, que comprende una célula (CM) de memoria; […]

Arquitecturas de baja potencia, del 29 de Marzo de 2019, de QUALCOMM INCORPORATED: Un dispositivo de baja potencia, que comprende: una ruta de reloj para propagar una señal de reloj, en el que la ruta de reloj incluye una pluralidad de transistores; […]

Divisor de reloj programable de alta velocidad, del 9 de Enero de 2019, de QUALCOMM INCORPORATED: Un procedimiento para dividir una señal de reloj de entrada por una proporción de división programable, el procedimiento que comprende: contar , en los bordes […]

Dispositivo y procedimiento para la identificación unívoca de un circuito integrado, del 4 de Octubre de 2018, de UNIVERSIDAD CARLOS III DE MADRID: La invención describe un dispositivo que comprende: un primer circuito generador de pulsos transitorios que tiene una entrada (2e) y una […]

Método para reducir la aparición de quemado debido a inestabilidad de temperatura en polarización negativa, del 11 de Mayo de 2016, de INTRINSIC ID B.V: Un método para atenuar el efecto de quemado y permitir la realización de un proceso de inicio con respecto a un dispositivo que comprende una pluralidad de elementos […]

CIRCUITO COMPARADOR DE GRAN PRECISION., del 16 de Noviembre de 1995, de ADVANCED MICRO DEVICES INC.: SE PRESENTA COMO CARACTERISTICA UN CIRCUITO COMPARADOR DE ENGANCHE. UNA FASE DE ENGANCHE, QUE COMPRENDE UN PRIMERO Y SEGUNDO CONMUTADORES, ALIMENTA SEÑALES […]