SISTEMA VOTADOR.

Sistema votador implementado mediante un sumador aritmético, que en el caso de redundancia triple,

permite además identificar una señal de entrada errónea.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P201031492.

Solicitante: UNIVERSIDAD DEL PAIS VASCO-EUSKAL HERRIKO UNIBERTSITATEA.

Nacionalidad solicitante: España.

Inventor/es: BIDARTE PERAITA,UNAI, ASTARLOA CUELLAR,ARMANDO, LAZARO ARROTEGUI,JESUS, ZULAGA IZAGUIRRE,Aitzol.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F11/18 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › utilizando un enmascaramiento pasivo del defecto de los circuitos redundantes, p. ej. por lógica combinatoria de los circuitos redundantes, por circuitos de decisión mayoritaria.

Fragmento de la descripción:

SISTEMA VOTADOR

CAMPO DE LA INVENCIÓN

La presente invención se aplica al campo de los sistemas de redundancia para la corrección de errores en circuitos digitales, y más específicamente, a los votadores utilizados en dichos sistemas.

ANTECEDENTES DE LA INVENCIÓN

Es conocido el uso de redundancia en aplicaciones electrónicas con altos requisitos de seguridad ante fallos. Las técnicas de redundancia implican utilizar una pluralidad de circuitos independientes para obtener un solo resultado. Cada uno de los circuitos genera una señal de salida, por lo que es necesario un sistema votador ("voter" en inglés) , que indica cual es el valor de salida más repetido. Dicho valor más repetido pasa a considerarse el resultado de salida del sistema de redundancia.

Por otra parte, se conocen dos formas fundamentales de realizar un circuito electrónico.

- Mediante dispositivos electrónicos en los que no es posible realizar ningún cambio interno, como por ejemplo microprocesadores y circuitos integrados para aplicaciones específicas (ASIC, del inglés "Application-Specific Integrated Circuit) .

- Mediante dispositivos reconfigurables (también denominados dispositivos lógicos programables) , es decir, cuyas interconexiones internas y funcionalidades pueden ser modificadas una vez fabricado el dispositivo físico. Este es el caso de los arrays de puertas programables de campo (FPGA, del inglés "Field Programmable Gate Array") y los Dispositivos Lógicos Programables Complejos (CPLD, del inglés "Complex Programmable Logic Device) . Dichos circuitos reconfigurables comprenden además otros recursos fijos (o "hard") , es decir elementos que existen en la estructura de silicio desde su construcción y cuya funcionalidad queda definida por el fabricante, y no por el diseñador, como pueden ser memorias, circuitos aritméticos, microprocesadores.

Dentro del segundo grupo de circuitos electrónicos (es decir, mediante dispositivos reconfigurables) , se conocen distintas técnicas relativas a la inclusión de redundancia. Por ejemplo, US 7, 512, 871 B1 presenta una técnica de reparación de errores una vez detectados. Por otra parte, WO 2004/077260 A2 divulga un método y aparato de creación de redundancia en dispositivos lógicos programables en el que primero se realiza un análisis del circuito para localizar puertas lógicas más sensibles a fallos, para luego aplicar sobre ellas los métodos de redundancia y protección. Finalmente, US 7, 650, 585 B1 presenta un modo de implementar un diseño en circuito lógico programable de modo que se reduzca el efecto de errores puntuales en el mismo.

No obstante, en todos los casos anteriores, los elementos del sistema de redundancia, y en concreto los sistemas votadores, se implementan mediante elementos lógicos programables genéricos de los dispositivos reconfigurables, lo cual limita su velocidad y fiabilidad a la de dichos elementos lógicos programables. Sigue existiendo por lo tanto en el estado de la técnica la necesidad de circuitos votadores rápidos y estables que puedan ser integrados dentro de dispositivos lógicos programables.

RESUMEN DE LA INVENCIÓN

La presente invención soluciona los problemas anteriormente descritos mediante un votador que permite obtener resultados rápidos y fiables al basarse en un sumador aritmético. La invención parte de 2n-1 señales lógicas de entrada, siendo n un número entero, y obtiene como resultado al menos una salida lógica que indica el valor más repetido entre las señales lógicas de entrada. Para ello, comprende un sumador cuyas entradas son las entradas lógicas del sistema, de modo que en el bit n de salida del sumador se obtiene el resultado de la votación (siempre considerando como primer bit el bit de salida de menor peso) .

Preferentemente, el sumador mencionado es un recurso hardware de un dispositivo lógico programable, tal como una FPGA. Es decir, no corresponde con un circuito resultante de un diseño programado sobre el dispositivo lógico, sino de un recurso físico presente en dicho dispositivo desde su fabricación. Se consigue así mejorar la fiabilidad del votador respecto a diseños realizados sobre elementos programables del dispositivo.

También preferentemente, para el caso concreto de n igual a 2, es decir, para el caso de redundancia triple (tres señales de entradas) , el votador comprende una salida auxiliar de dos bits que permite, cuando se produce un error en una de las entradas lógicas del sistema, identificar dicha entrada lógica errónea. Preferentemente, dicha salida auxiliar se genera mediante dos funciones o exclusivas (es decir, dos funciones XOR, del inglés "exclusive OR") . El bit de menor peso de la salida auxiliar es la función XOR de la primera y la segunda entradas de salida, y el bit de mayor peso de la salida auxiliar es la función XOR de la segunda y la tercera entradas de salida.

Aún más preferentemente, dichas funciones XOR se implementan también por medio de una suma, en este caso, tomando como resultado de la función el bit de menor peso de una suma de dos señales. Al utilizar también para generar la salida auxiliar sumadores, se consigue añadir la prestación de detección de errores de forma rápida y fiable.

Esta y otras ventajas de la invención serán aparentes a la luz de la descripción detallada de la misma.

BREVE DESCRIPCIÓN DE LAS FIGURAS

Con objeto de ayudar a una mejor comprensión de las características del invento de acuerdo con un ejemplo preferente de realización práctica del mismo y para complementar esta descripción, se acompaña como parte integrante de la misma la siguiente figura, cuyo carácter es ilustrativo y no limitativo:

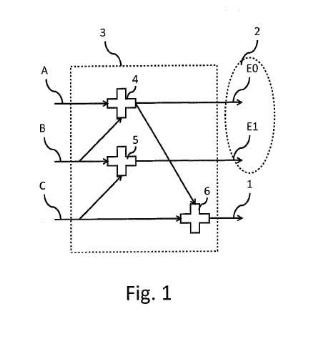

La figura 1 muestra un esquema del sistema votador de la invención de acuerdo con una realización preferente del mismo.

DESCRIPCIÓN DETALLADA DE LA INVENCIÓN

En este texto, el término "comprende" y sus derivaciones (como "comprendiendo", etc.) no deben entenderse en un sentido excluyente, es decir, estos términos no deben interpretarse como excluyentes de la posibilidad de que lo que se describe y define pueda incluir más elementos, etapas, etc.

La figura 1 presenta una implementación particular del sistema votador de la invención, el cual toma como partida una pluralidad de entradas lógicas (en este caso tres entradas A B y C, aunque el sistema es igualmente válido para cualquier número de entradas igual a 2n-1, siendo n un número entero) , y genera una salida lógica 1 que indica cual es la entrada lógica más repetida. Adicionalmente, el sistema tiene una salida auxiliar 2, compuesta por dos bits E0 y E1, que en caso de que una de las entradas lógicas A, B o C es errónea (es decir, su valor no coincide con el de las otras dos entradas lógicas) , identifica dicha entrada errónea. En definitiva, las salidas para todas las combinaciones posibles de entrada se pueden ver en la siguiente tabla:

A B C Salida E1 E0 Error 0 0 0 0 0 0 0 1 0 0 0 0 1 1 0 1 0 0 1 0 2 1 1 0 1 1 1 3 0 0 1 0 1 1 3 1 0 1 1 1 0 2 0 1 1 1 0 1 1 1 1 1 1 0 0 0donde la columna "Error" se refiere a cuál es la entrada errónea (si la hay) , y por tanto corresponde con el valor numérico codificado por los bits E1 y E0. El valor "1" se refiere a la entrada A, el valor "2" a la entrada B, y el valor "3" a la entrada C. El valor "0" en dicha columna "Error" significa que todas las entradas coinciden y por lo tanto no se ha encontrado ningún error.

Tanto la salida lógica 1 como la señal auxiliar 2 se generan mediante un sumador aritmético 3, que corresponde con un recurso fijo de un dispositivo lógico programable, es decir, no es un circuito formado por elementos programables configurados por un diseñador, sino que existe en el dispositivo lógico programable desde su fabricación.

En concreto, la salida 1 es el segundo bit empezando por el bit menos significativo de la suma de las tres entradas A, B y C. Nótese que si el sumador tiene precisamente tres entradas, dicho segundo bit coincide con el bit de mayor peso. Sin embargo, si el sumador tiene un mayor número de entradas (y por lo tanto también de salidas) , el sistema es igualmente válido, sólo que existen bits adicionales por encima del segundo que no son utilizados por el sistema votador.

En la implementación particular mostrada en la figura 1, la suma de A, B y C que corresponde con la salida 1 se realiza en dos etapas. Una primera suma parcial 4 realiza la suma de las entradas A y B, y su resultado...

Reivindicaciones:

1. Sistema votador que comprende un número de entradas lógicas (A, B, C) con unos valores de entrada y una salida lógica (1) con un valor de salida, siendo el valor de salida igual al valor de entrada más repetido en las entradas lógicas (A, B, C) , y donde el número de entradas lógicas (A, B, C) es igual a uno menos que dos elevado a un número entero n;

caracterizado porque comprende al menos un circuito sumador (3) con unas entradas y al menos el número entero n de bits de salida, siendo las entradas del sumador (3) las entradas lógicas del sistema (A, B, C) , y siendo el n-simo bit de salida de mayor peso del sumador (3) la salida lógica (1) del sistema.

2. Sistema según la reivindicación 1 caracterizado porque el circuito sumador (3) es un sumador hardware no programable de un dispositivo lógico programable.

3. Sistema según cualquiera de las reivindicaciones anteriores caracterizado porque el número entero es dos, y porque comprende además una salida auxiliar (2) de dos bits (E0, E1) que indica una entrada lógica (A, B, C) del sistema en la que se produce un error.

4. Sistema según la reivindicación 3 caracterizado porque el bit de menos peso (E0) de la salida auxiliar (2) es una función o exclusiva de la primera entrada lógica (A) y la segunda entrada lógica (B) del sistema, y el bit de mayor peso (E1) de la salida auxiliar (2) es una función o exclusiva de la segunda entrad lógica (B) y la tercera entrada (C) lógica del sistema.

5. Sistema según la reivindicación 4 caracterizado porque las funciones o exclusivas se implementan como el bit de salida de menor peso de una suma de las dos entradas lógicas.

OFICINA ESPAÑOLA DE PATENTES Y MARCAS

Nº solicitud: 201031492

ESPAÑA

Fecha de presentación de la solicitud: 07.10.2010

Fecha de prioridad:

INFORME SOBRE EL ESTADO DE LA TECNICA

51 Int. Cl. : G06F11/18 (2006.01)

DOCUMENTOS RELEVANTES

Categoría 56 Documentos citados Reivindicaciones afectadas X WO 8706037 A1 (TRIPLEX) 08.10.1987, página 9, línea 28 - página 12, línea 5; figuras. 1-5 A "Triple Module Redundancy Design Techniques for Virtex FPGAs" (CARL CARMICHAEL) . 06.07.2006. Xilinx, Virtex Series: Application Note XAPP197 (v1.0.1) . 1-5 A US 7036059 B1 (CARMICHAEL CARL H et al.) 25.04.2006, todo el documento. 1-5 Categoría de los documentos citados X: de particular relevancia Y: de particular relevancia combinado con otro/s de la misma categoría A: refleja el estado de la técnica O: referido a divulgación no escrita P: publicado entre la fecha de prioridad y la de presentación de la solicitud E: documento anterior, pero publicado después de la fecha de presentación de la solicitud El presente informe ha sido realizado • para todas las reivindicaciones • para las reivindicaciones nº : Fecha de realización del informe 11.04.2012 Examinador J. Calvo Herrando Página 1/4INFORME DEL ESTADO DE LA TÉCNICA

Nº de solicitud: 201031492

Documentación mínima buscada (sistema de clasificación seguido de los símbolos de clasificación) G06F Bases de datos electrónicas consultadas durante la búsqueda (nombre de la base de datos y, si es posible, términos de búsqueda utilizados) INVENES, EPODOC

Informe del Estado de la Técnica Página 2/4

OPINIÓN ESCRITA

Nº de solicitud: 201031492

Fecha de Realización de la Opinión Escrita: 11.04.2012

Declaración

Novedad (Art. 6.1 LP 11/1986) Reivindicaciones Reivindicaciones 1-5 SI NO Actividad inventiva (Art. 8.1 LP11/1986) Reivindicaciones Reivindicaciones 1-5 SI NOSe considera que la solicitud cumple con el requisito de aplicación industrial. Este requisito fue evaluado durante la fase de examen formal y técnico de la solicitud (Artículo 31.2 Ley 11/1986) .

Base de la Opinión.

La presente opinión se ha realizado sobre la base de la solicitud de patente tal y como se publica.

Informe del Estado de la Técnica Página 3/4

OPINIÓN ESCRITA

Nº de solicitud: 201031492

1. Documentos considerados.

A continuación se relacionan los documentos pertenecientes al estado de la técnica tomados en consideración para la realización de esta opinión.

Documento Número Publicación o Identificación Fecha Publicación D01 WO 8706037 A1 (TRIPLEX ) 08.10.1987 D02 "Triple Module Redundancy Design Techniques for Virtex FPGAs" (CARL CARMICHAEL) 06.07.2006 D03 US 7036059 B1 (CARMICHAEL CARL H et al.) 25.04.20062. Declaración motivada según los artículos 29.6 y 29.7 del Reglamento de ejecución de la Ley 11/1986, de 20 de marzo, de Patentes sobre la novedad y la actividad inventiva; citas y explicaciones en apoyo de esta declaración El objeto principal de la invención es un sistema votador. Se considera como el documento del estado de la técnica más próximo al objeto reivindicado el documento D01, el cual afecta a la actividad inventiva de todas las reivindicaciones, tal y como se explica a continuación:

Reivindicación independiente R1

El sistema votador descrito por el documento D01 (pág.

9. pág. 12) comprende un número de entradas lógicas donde la salida es el valor de la entrada más repetido.

La diferencia entre el documento D01 y el objeto de la presente invención es que no se especifica que el sistema votador se implemente al menos con un circuito sumador siendo su salida el bit de mayor peso. Sin embargo, esta diferencia se considera una opción normal de diseño a la luz de lo divulgado por el documento D02 donde el uso de sumadores en el diseño de sistemas votadores es una técnica muy conocida.

Por tanto, no se considera que esta diferencia confiera ningún elemento de significación inventiva con respecto al estado de la técnica conocido. La reivindicación R1 no cumple con el requisito de actividad inventiva establecido en el Art. 8.1 LP.

Reivindicaciones dependientes R2-R5

Se considera que la característica descrita en la reivindicación R2 resulta obvia para un experto en la materia. No se considera que requiera ningún esfuerzo inventivo utilizar un sumador hardware no programable como elemento sumador si el propio dispositivo lógico programable (FPGA) cuenta con este tipo de sumadores tal y como se detalla en la propia descripción de la invención.

Como se puede observar en la tabla 1 del documento D01 (página 11) , el sistema divulga una salida auxiliar donde se identifica el módulo donde se produce el error. Por lo tanto, el objeto de la reivindicación R3 no difiere de ninguna manera esencial de lo conocido en el estado de la técnica.

El objeto de las reivindicaciones R4 y R5 comprende sólo modos de realización y no se puede considerar que implique actividad inventiva Por consiguiente, las reivindicaciones R2-R5 no implican actividad inventiva (Art. 8.1 LP)

Informe del Estado de la Técnica Página 4/4

Patentes similares o relacionadas:

Arquitectura de marco tolerante a fallos con triple redundancia de software, del 17 de Enero de 2019, de THALES: Un procedimiento implementado por ordenador para detectar un fallo en un sistema que comprende las etapas de: ejecutar al menos tres máquinas […]

Sistema, método y aparato para la corrección de errores en sistemas multiprocesador, del 27 de Diciembre de 2018, de Data Device Corporation: Un método para sincronizar el estado de una pluralidad de módulos informáticos en un sistema electrónico, teniendo cada módulo informático un procesador, que […]

Sistemas y métodos para asegurar datos en movimiento, del 9 de Mayo de 2018, de Security First Corp: Un método para leer y escribir un conjunto de datos, que comprende: dividir el conjunto de datos en una o más comparticiones de datos 5 usando un algoritmo […]

Procedimientos y aparatos de reducción de fallos de modo común de sistemas de control de software relacionados con seguridad nuclear, del 4 de Enero de 2017, de GE-HITACHI NUCLEAR ENERGY AMERICAS LLC: Un sistema informático para ejecutar una tarea de acuerdo con diferentes frecuencias de reloj para reducir fallos de modo común en el sistema informático, […]

Dispositivo de prevención de fallos y método para operar el dispositivo de prevención de fallos, del 25 de Mayo de 2016, de Thales Deutschland GmbH: Sistema de prevención de fallos para un sistema de salida de datos, comprendiendo el dispositivo * al menos una unidad de memoria (4a, 4b) con un conjunto pregrabado […]

Sistema de vigilancia de valores de medida y desconexión cuando se presentan desviaciones de valores de medida, del 22 de Octubre de 2014, de PHOENIX CONTACT GMBH & CO. KG: Sistema de vigilancia de valores de medida y desconexión cuando se presentan desviaciones de los valores de medida, que incluye: - un microcontrolador […]

Método y sistema para almacenar y leer datos en o a partir de un almacenamiento de valor de clave, del 10 de Septiembre de 2014, de NEC EUROPE LTD: Un método para almacenar (put) datos (v) en un almacenamiento de valor de clave que tiene una pluralidad de n servidores (S1, S2, S3, S4), en el que t< n servidores (S1, S2, […]

Nodo de bus de datos de tolerancia de fallos en un sistema distribuido, del 23 de Octubre de 2013, de SAAB AB: Un nodo de bus de datos, que es un nodo de control, o un nodo de detección yque está dispuesto para comunicar a través de un bus […]

Nodo de bus de datos de tolerancia de fallos en un sistema distribuido, del 23 de Octubre de 2013, de SAAB AB: Un nodo de bus de datos, que es un nodo de control, o un nodo de detección yque está dispuesto para comunicar a través de un bus […]