Procedimiento y aparato para la gestión proactiva de memoria intermedia de direcciones de bifurcación de destino.

Un sistema de predicción de bifurcaciones de múltiples etapas que comprende:

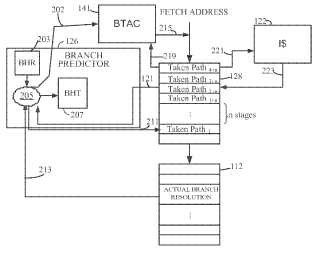

una memoria intermedia de direcciones de bifurcación de destino BTAC (141) configurada para almacenaruna entrada BTAC asociada con una instrucción de bifurcación condicional; y

un circuito predictor (203, 205, 207) de bifurcaciones configurado para almacenar información de estadopara predecir la dirección de la instrucción de bifurcación condicional y para utilizar la información de estadopara predecir la dirección, en el que el circuito predictor (203, 205, 207) de bifurcaciones está configurado,además, para recibir una dirección de bifurcación de la instrucción de bifurcación condicional cuando hasido resuelta realmente, y caracterizado porque el circuito predictor (203, 205, 207) de bifurcaciones estádispuesto para gestionar una directriz de sustitución para la entrada BTAC, siendo capaz dicha gestión demodificar los resultados de una directriz de sustitución usada en la BTAC (141) dependiendo de lainformación de estado almacenada para la instrucción de bifurcación condicional y de la dirección debifurcación recibida.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2007/072317.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: Attn: International IP Administration 5775 Morehouse Drive San Diego, CA 92121 ESTADOS UNIDOS DE AMERICA.

Inventor/es: RYCHLIK,BOHUSLAV.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F9/38 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Ejecución simultánea de instrucciones, p. ej. segmentación, anticipación.

PDF original: ES-2386478_T3.pdf

Fragmento de la descripción:

Procedimientos y aparato para la gestión activa de memoria intermedia de direcciones de bifurcación de destino

Campo de la invención

La presente invención versa acerca de un sistema de predicción de bifurcaciones de múltiples etapas.

Antecedentes

Los microprocesadores llevan a cabo tareas de cálculo en una amplia variedad de aplicaciones. Casi siempre es deseable un rendimiento mayor del procesador para permitir una operación más rápida y/o un aumento de la funcionalidad mediante cambios en el soporte lógico. En muchas aplicaciones integradas, tales como dispositivos electrónicos portátiles, la conservación de la energía también es una meta importante en el diseño y la implementación de los procesadores.

Muchos procesadores modernos emplean una arquitectura de segmentación de cauce en la que se solapan en ejecución instrucciones secuenciales, cada una de las cuales tiene múltiples etapas de ejecución. En aras de un mayor rendimiento, las instrucciones deberían fluir de forma continua por el cauce. Cualquier situación que haga que las instrucciones se atasquen en el cauce puede perjudicar el rendimiento. Si se vacían instrucciones del cauce y luego son buscadas de nuevo, se resienten tanto el rendimiento como el consumo de energía.

La mayoría de los programas incluye instrucciones de bifurcación condicional, desconociéndose el comportamiento real de bifurcación de los cuales hasta que se evalúe la instrucción muy dentro del cauce. Para evitar el atasco que resultaría de esperar la evaluación real de la instrucción de bifurcación, los procesadores modernos pueden emplear alguna forma de predicción de bifurcaciones por la que se prediga el comportamiento de bifurcación de las instrucciones de bifurcación condicional temprano en el cauce. Con base en la evaluación de la bifurcación predicha, el procesador busca especulativamente (busca de antemano) y ejecuta instrucciones de una dirección predica, ya se trate de la dirección de bifurcación de destino (si se predice que se tomará la bifurcación) o la siguiente dirección secuencial después de la instrucción de bifurcación (si se predice que no se tomará la bifurcación) . Que haya de tomarse o no una instrucción de bifurcación condicional se denomina determinación de la dirección de la bifurcación. La determinación de la dirección de la bifurcación puede realizarse en el momento de la predicción y en el momento de la resolución real de la bifurcación. Cuando se determina el comportamiento real de la bifurcación, si se predijo equivocadamente la bifurcación, deben vaciarse del cauce las instrucciones buscadas especulativamente y deben buscarse nuevas instrucciones de la siguiente dirección correcta. La búsqueda de instrucciones de antemano en respuesta a una predicción errónea de bifurcación puede tener un impacto adverso en el rendimiento y el consumo de energía del procesador. En consecuencia, mejorar la precisión de la predicción de bifurcaciones es una importante meta de diseño de los procesadores.

Una forma conocida de predicción de bifurcaciones incluye dividir la predicción de bifurcaciones en dos predictores: una memoria intermedia de direcciones iniciales de bifurcación de destino (BTAC) y una tabla del historial de bifurcaciones (BHT) . La BTAC, también denominada memoria intermedia de bifurcaciones de destino (BTB) , está indexada por una dirección de búsqueda de instrucción y contiene la siguiente dirección buscada, también denominada bifurcación de destino, correspondiente a la dirección de búsqueda de instrucción. Se añaden entradas a una BTAC convencional después de que una instrucción de bifurcación ha pasado por el cauce del procesador y se ha tomado su bifurcación. Si la BTAC convencional está llena, convencionalmente se eliminan entradas de la BTAC usando algoritmos estándar de sustitución de la memoria intermedia (tales como el turno rotatorio o del usado menos recientemente) cuando se añade la siguiente entrada.

Las BTAC, en general, son implementadas a menudo como un diseño de una memoria intermedia muy asociativa y a la que se accede temprano en el cauce de búsqueda. Si la dirección de búsqueda coincide con una entrada BTAC (una diana en la BTAC) , la correspondiente siguiente dirección de búsqueda o dirección de destino es buscada en el ciclo siguiente. Esta situación de coincidencia y subsiguiente búsqueda de la dirección de destino se denomina predicción implícita de bifurcación tomada. Si no hay coincidencia (un diana fallida en la BTAC) , la siguiente dirección incrementada secuencialmente es buscada en el ciclo siguiente. Esta situación de falta de coincidencia se denomina también predicción implícita de bifurcación no tomada.

Las BTAC, en general, son utilizadas junto con un predictor individual más preciso de direcciones de bifurcación, tal como la tabla del historial de bifurcaciones (BHT) , también denominada tabla del historial de patrones (PHT) . Las BHT convencionales son objeto de acceso más tarde en el cauce que una BTAC convencional. Como tales, puede haber presente información adicional para efectuar una mejor predicción. Una BHT convencional puede contener un conjunto de contadores de direcciones predichas con saturación para producir una decisión más precisa de bifurcación tomada/no tomada para instrucciones individuales de bifurcación. Por ejemplo, cada contador de direcciones predichas con saturación puede comprender un contador de 2 bits que adopte uno de cuatro estados, asignándose a cada uno un valor ponderado de predicción, tal como:

11 – Se predice con mucha seguridad que se tomará

– Se predice con poca seguridad que se tomará 01 – Se predice con poca seguridad que no se tomará 00 – Se predice con mucha seguridad que no se tomará

Las BHT, en general, son indexadas convencionalmente por bits almacenados en un registro del historial de bifurcaciones (BHR) . La salida de una BHT convencional es una decisión de bifurcación tomada o no tomada, lo que da como resultado ya sea la búsqueda de la dirección de destino de la instrucción de bifurcación o de la siguiente dirección secuencial en el ciclo siguiente. Comúnmente, la BHT es actualizada con información del resultado de las bifurcaciones cuando se conoce.

Utilizando una BHT convencional, un procesador puede anular una predicción implícita anterior realizada por una BTAC. Por ejemplo, una BTAC puede hacer diana (prediciendo implícitamente una bifurcación tomada) , pero la BHT puede anular la predicción implícita de la BTAC con una predicción de bifurcación no tomada. En cambio, tras una diana fallida de la BTAC, la BHT puede anular la diana fallida de la BTAC con una predicción de bifurcación tomada, dado que la dirección de destino es conocida ahora en este punto del cauce del procesador.

Que una BHT anule predicciones de la BTAC da como resultado ciclos perdidos, lo que resulta de vaciar al cauce del procesador. Que una BHT anule predicciones de la BTAC puede ocurrir de forma reiterada cuando el cauce procese subsiguientemente una instrucción similar de bifurcación. Por ejemplo, si la BTAC predice implícitamente una bifurcación tomada porque se encuentra una coincidencia en la BTAC, empiezan a buscarse instrucciones a partir de la dirección de destino (bifurcación tomada) en el cauce del procesador. Subsiguientemente, si la BHT anula la predicción de la BTAC decidiendo que no debería tomarse la bifurcación, tienen que ser vaciadas del cauce todas las instrucciones posteriores a la búsqueda de la dirección de destino. En esta técnica convencional de predicción de bifurcaciones, este ciclo se repite potencialmente para la misma instrucción de bifurcación buscada subsiguientemente. Este problema de los conflictos reiterados de predicción de bifurcaciones en búsquedas subsiguientes de la misma instrucción de bifurcación condicional es denominado en el presente documento problema de ciclos de vaciado múltiple. En un enfoque convencional, el problema de ciclos de vaciado múltiple puede seguir existiendo para una instrucción de bifurcación condicional hasta que se actualice la BTAC. Por lo tanto, se reconoce que se precisan un aparato y procedimientos para gestionar activamente la BTAC y reducir la probabilidad de la incidencia del problema de ciclos de vaciado múltiple. El documento US2002/0188833 describe un sistema de pila dual de llamada/retorno de predicción de bifurcaciones.

Resumen

Según la invención, se... [Seguir leyendo]

Reivindicaciones:

1. Un sistema de predicción de bifurcaciones de múltiples etapas que comprende:

una memoria intermedia de direcciones de bifurcación de destino BTAC (141) configurada para almacenar una entrada BTAC asociada con una instrucción de bifurcación condicional; y

un circuito predictor (203, 205, 207) de bifurcaciones configurado para almacenar información de estado para predecir la dirección de la instrucción de bifurcación condicional y para utilizar la información de estado para predecir la dirección, en el que el circuito predictor (203, 205, 207) de bifurcaciones está configurado, además, para recibir una dirección de bifurcación de la instrucción de bifurcación condicional cuando ha sido resuelta realmente, y caracterizado porque el circuito predictor (203, 205, 207) de bifurcaciones está

dispuesto para gestionar una directriz de sustitución para la entrada BTAC, siendo capaz dicha gestión de modificar los resultados de una directriz de sustitución usada en la BTAC (141) dependiendo de la información de estado almacenada para la instrucción de bifurcación condicional y de la dirección de bifurcación recibida.

2. El sistema de la reivindicación 1 en el que el circuito predictor (203, 205, 207) de bifurcaciones está 15 configurado para eliminar la entrada BTAC de la BTAC (141) .

3. El sistema de la reivindicación 1 en el que el circuito predictor (203, 205, 207) de bifurcaciones está configurado para mantener la entrada BTAC de la BTAC (141) durante un periodo de tiempo extendido.

4. El sistema de la reivindicación 1 en el que la BTAC (141) está configurada para mantener almacenadas una o

más entradas en un orden de sustitución y en el que el circuito predictor de bifurcaciones está configurado para 20 modificar la posición de la entrada BTAC en el orden de sustitución.

5. El sistema de la reivindicación 4 en el que el circuito predictor (203, 205, 207) de bifurcaciones está configurado para modificar la posición de la entrada BTAC más arriba en el orden de sustitución que su posición actual para aumentar la probabilidad de sustitución de la entrada BTAC.

6. El sistema de la reivindicación 1 que, además, comprende: un puntero de sustitución, en el que la BTAC (141)

emplea una directriz de sustitución de turno rotatorio modificado y en el que el circuito predictor de bifurcaciones está configurado para modificar el puntero de sustitución para que apunte a la entrada BTAC.

7. Un procedimiento de gestión de una memoria intermedia de direcciones de bifurcación de destino BTAC (141) que comprende:

recibir (510) una dirección de bifurcación de una instrucción de bifurcación condicional que ha sido resuelta 30 realmente;

almacenar (520) información de estado en un circuito predictor (203, 205, 207) de bifurcaciones, siendo la información de estado para predecir la dirección de la instrucción de bifurcación condicional; y

caracterizado por

gestionar (530) una directriz de sustitución para una entrada en la BTAC (141) asociada con la instrucción

de bifurcación condicional, siendo capaz dicha gestión de modificar los resultados de una directriz de sustitución usada en la BTAC (141) dependiendo de la información de estado almacenada y de la dirección de bifurcación recibida.

8. El procedimiento de la reivindicación 7 en el que la gestión (530) de una directriz de sustitución para una entrada en la BTAC (141) comprende: la eliminación de la entrada de la BTAC (141) .

9. El procedimiento de la reivindicación 7 en el que la gestión (530) de una directriz de sustitución para una entrada en la BTAC (141) comprende: el mantenimiento de la entrada BTAC de la BTAC (141) durante un periodo de tiempo prolongado.

10. El procedimiento de la reivindicación 7 que, además, comprende: mantener almacenadas en la BTAC (141)

entradas en un orden de sustitución, en el que la gestión (530) de una directriz de sustitución para una entrada 45 en la BTAC comprende modificar la posición de la entrada BTAC en el orden de sustitución.

11. El procedimiento de la reivindicación 9 en el que la modificación de la posición de la entrada BTAC comprende modificar un puntero de sustitución para que apunte a la entrada BTAC.

Patentes similares o relacionadas:

Control de ejecución de hilos en un procesador multihilo, del 24 de Junio de 2020, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para controlar la ejecución de hilos en un entorno informático, comprendiendo dicho método: detener , mediante un hilo […]

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Predicados uniformes en sombreadores para unidades de procesamiento de gráficos, del 11 de Diciembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para procesar datos, comprendiendo el procedimiento: recibir una indicación de que todos los subprocesos de una urdimbre […]

Aumento de protocolo de coherencia para indicar estado de transacción, del 4 de Diciembre de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método implementado por ordenador para implementar un protocolo de coherencia, comprendiendo el método: enviar , por un procesador (112a) solicitante, […]

Método y aparato para un acceso a memoria basado en hilos en un procesador multihilo, del 11 de Septiembre de 2019, de QUALCOMM INCORPORATED: Método para acceder a una memoria por un procesador multihilo , comprendiendo el método: determinar un identificador de hilo asociado a un […]

Procedimientos y aparatos para predecir la no ejecución de instrucciones de no bifurcación condicional, del 15 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para manejar una instrucción de no bifurcación condicional, que comprende: identificar una instrucción […]

Procesamiento transaccional, del 17 de Abril de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método de controlar la ejecución de una transacción en un entorno informático, comprendiendo el método los pasos de: Iniciar, mediante un procesador, la ejecución […]

Guardar/restablecer registros seleccionados en procesamiento transaccional, del 13 de Marzo de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para facilitar el procesamiento de transacciones dentro de un entorno de computación, comprendiendo dicho método: obtener una instrucción […]