Procedimiento de detección de anomalias en un circuito criptográfico protegido por lógica diferencial y circuito para implementar a dicho procedimiento.

Circuito protegido por lógica diferencial que procesa variables lógicas representadas por pares de componentes(at,

af) (bt, bf), una primera red de células (T) que realizan funciones lógicas sobre la primera componente de dichospares, una segunda red de células duales (F) que funciona en lógica complementaria sobre la segunda componente,caracterizado porque las componentes de los pares son agrupadas por vectores (At, Af, Bt, Bf), comprendiendodicho circuito módulos de detección compuestos por dos multiplicadores-acumuladores (81, 82) que realizanoperaciones de multiplicación-acumulación entre los vectores (At, Bt) que agrupan a las primeras componentes delos pares por un lado y los vectores (Af, Bf) que agrupan a las segundas componentes de los pares por otro lado,esto después de que un bit de orden bajo de valor 1 se haya añadido a cada uno de dichos vectores, siendo ladiferencia calculada entre los resultados de las dos operaciones (83) y a continuación procesada por un comparadorcon cero (84) cuya salida toma el valor cero cuando se detecta un estado no coherente en las fases de precarga ode evaluación

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2009/059886.

Solicitante: Institut Telecom - Telecom Paristech.

Nacionalidad solicitante: Francia.

Dirección: 46 Rue Barrault 75013 Paris FRANCIA.

Inventor/es: DANGER,Jean-Luc, GUILLEY,Sylvain, FLAMENT,Florent.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F21/00 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › Disposiciones de seguridad para la protección de computadores, sus componentes, programas o datos contra actividades no autorizadas.

- G06F21/02

PDF original: ES-2386061_T3.pdf

Fragmento de la descripción:

Procedimiento de detección de anomalías en un circuito criptográfico protegido por lógica diferencial y circuito implementa a dicho procedimiento La invención se refiere a un procedimiento y un circuito de detección de anomalías en un circuito criptográfico protegido por lógica diferencial.

La invención se aplica particularmente al campo de la protección de los circuitos criptográficos contra los ataques por inyección de fallos.

La criptografía tiene particularmente como objetivo proteger:

- el secreto de información por medio del cifrado y de su operación dual: el descifrado;

- solamente su integridad, mediante operaciones de firma y de verificación de firma.

La criptografía utiliza métodos matemáticos seguros, en el sentido de que no existen en el estado actual de los conocimientos publicados métodos de ataque más rápido que el ataque exhaustivo correspondiente al ensayo de todas las claves posibles.

En general, los métodos de cifrado implican cálculos complejos necesarios para la seguridad de los sistemas. Esta complejidad no plantea problemas particulares a los ordenadores pero constituye un inconveniente en el caso de dispositivos para el gran público que no cuentan con una gran potencia de cálculo, en general controlados por microprocesadores de coste reducido. Las consecuencias pueden ser entonces de varios órdenes, de este modo por ejemplo una tarjeta bancaria emplearía varios minutos en firmar una transacción o un decodificador digital de televisión de pago no podría seguir el caudal de información en juego.

Para paliar este tipo de problema sin aumentar el precio de los sistemas, es habitual añadir una ayuda a la unidad central que controla el dispositivo, en general en forma de un coprocesador dedicado a la criptografía.

Sin embargo, ya sea implementado por la unidad central o por un coprocesador especializado, el algoritmo criptográfico es implementado en todos los casos por un dispositivo físico, electrónico. Los dispositivos electrónicos presentan imperfecciones inevitables vinculadas a las propiedades inherentes de las leyes de la electricidad.

Es así que sistemas criptográficos seguros desde el punto de vista matemático pueden ser atacados explotando las imperfecciones de los sistemas físicos que implementan el algoritmo. La duración de los cálculos puede depender de los valores de los datos, en particular en sistemas informáticos optimizados en tiempo, lo que puede dar lugar a los ataques de tipo “timing attack” que permiten en algunos casos recuperar la totalidad de las claves secretas a partir de simples mediciones de tiempos de ejecución. El consumo eléctrico instantáneo también puede depender de los datos, lo que puede dar lugar a series de ataques tales como:

- SPA (Simple Power Analysis) que intenta diferenciar las operaciones ejecutadas por una unidad central a partir de una medición de su consumo eléctrico medido durante una operación criptográfica;

- análisis diferencial de consumo DPA (Differential Power Analysis) que utiliza operaciones estadísticas en numerosas mediciones de consumo eléctrico, realizadas durante operaciones de criptografía en mensajes aleatorios y con una clave constante para validar o invalidar una hipótesis planteada en una parte limitada de la clave;

- ataques de tipo “template” (plantilla) que en una primera fase utilizan un dispositivo idéntico al dispositivo atacado, excepto que este dispositivo idéntico no contiene ningún secreto, para construir modelos de consumo indexados por el valor de una parte limitada de la clave y en una segunda fase utilizan varias mediciones de consumo del dispositivo atacado para determinar el modelo cuyos consumos medidos son los más próximos y, de este modo, determinar el valor de esta sub-clave;

Por otro lado, cualquier corriente eléctrica que circula por un conductor genera un campo electromagnético cuya medición puede dar lugar a ataques idénticos en su principio a los ataques relacionados con el consumo eléctrico, particularmente por DPA.

Finalmente, ataques llamados activos, o por inyección de fallos, perturban el funcionamiento de los sistemas para explotar los falsos resultados para recuperar los secretos del sistema.

Se denomina “canal oculto” a cualquier imperfección de un dispositivo físico que emplea un algoritmo criptográfico y susceptible de dejar escapar información vinculada a los secretos conservados en la memoria del dispositivo.

Los ataques en fallos son ataques activos que pueden se de naturalezas muy diferentes, como se explica particularmente en el artículo de David Naccache “Finding faults”, IEEE Security and Privacy, 3 (5) , páginas 61-65, 2005: variación de temperatura o tensión, señal parásita fuerte en la alimentación o mediante campo electromagnético, disparos láser, etc. Los fallos generados tienen como consecuencia la modificación del valor de un nodo del circuito atacado. Estos pueden ser sencillos o múltiples, permanentes o transitorios en función del impacto sobre el silicio. La flexibilidad de las inyecciones de fallos transitorios da lugar a ataques más potentes realizando ensayos múltiples y aumenta, de este modo, las probabilidades de éxito. Los ataques con fallos sencillos simplifican el procedimiento de ataque. Los ataques en fallos se basan en el análisis diferencial entre la salida cifrada no errónea y la salida con fallo. Por ejemplo, el ataque presentado en el artículo de Gilles Piret y Jean-Jacques Quisquater “A Differential Fault Attack Technique against SPN Structures, with Application to the AES and KHAZAD”, en CHES, volumen 2779 de LNCS, páginas 77-88, Springer, 2003 sobre el cifrado AES ha demostrado ser extremadamente eficaz si el fallo llega en la penúltima o antepenúltima ronda.

Los ataques por inyección de fallos han sido, hasta el presente, y esto de forma muy paradójica, considerados como costosos y, por lo tanto, accesibles en la práctica únicamente por organizaciones dudosas sostenidas económicamente. Actualmente es posible controlar a través de Internet una estación de descapsulación y un banco láser conciliable clave en mano. De ello resulta que la verosimilitud de un ataque por inyección de fallos ha aumentado considerablemente. De este modo, un criptoprocesador implantado en un circuito integrado, por ejemplo un FPGA, no obstante solamente puede considerarse seguro si implementa simultáneamente contramedidas para los ataques en observación, particularmente de tipos DPA o EMA, y en inyección de fallos. Además, ataques que combinan observación y fallos se han propuesto, como el descrito por Bruno Robisson y Pascal Manet en su artículo “Differential Behavioral Analysis”, en CHES, volumen 4727 de LNCS, páginas 413-426, Springer, 2007.

Una contramedida eficaz para luchar contra este tipo de ataque se basa en el empleo de la redundancia. Por ejemplo, puede reproducirse un bloque de cálculo tres veces y una función mayoría permite a continuación eliminar el bloque en el que se ha inyectado un fallo. Uno de los inconvenientes de esta solución es que implica un sobrecoste debido a la reproducción del o de los bloques de cálculo o bien a la inserción de un módulo de control de coherencia basado en una verificación de invariantes.

Otra contramedida consiste en detectar la inyección de fallos. En este caso el usuario es alertado y puede actuar para protegerse, reinicializando el sistema, por ejemplo.

Un objetivo de la invención es, particularmente, paliar los inconvenientes mencionados anteriormente.

A tal efecto, la invención tiene por objeto un procedimiento de detección de anomalías en un circuito protegido por lógica diferencial y que procesa variables lógicas representadas por un par de componentes, una primera red de células que realizan funciones lógicas sobre la primera componente de dichos pares, una segunda red de células duales que funcionan en lógica complementaria sobre la segunda componente, estando las funciones lógicas realizadas por cada par de células en una fase de precarga que pone a las variables en un estado conocido en la entrada de las células, seguida por una fase de evaluación en la que un cálculo es realizado por las células. Una anomalía es detectada por al menos un estado no coherente que se produce durante la fase de precarga o durante la fase de evaluación.

El circuito protegido por lógica diferencial es, por ejemplo, un circuito criptográfico.

De acuerdo con un aspecto de la... [Seguir leyendo]

Reivindicaciones:

1. Circuito protegido por lógica diferencial que procesa variables lógicas representadas por pares de componentes (at, af) (bt, bf) , una primera red de células (T) que realizan funciones lógicas sobre la primera componente de dichos pares, una segunda red de células duales (F) que funciona en lógica complementaria sobre la segunda componente, caracterizado porque las componentes de los pares son agrupadas por vectores (At, Af, Bt, Bf) , comprendiendo dicho circuito módulos de detección compuestos por dos multiplicadores-acumuladores (81, 82) que realizan operaciones de multiplicación-acumulación entre los vectores (At, Bt) que agrupan a las primeras componentes de los pares por un lado y los vectores (Af, Bf) que agrupan a las segundas componentes de los pares por otro lado, esto después de que un bit de orden bajo de valor 1 se haya añadido a cada uno de dichos vectores, siendo la diferencia calculada entre los resultados de las dos operaciones (83) y a continuación procesada por un comparador con cero (84) cuya salida toma el valor cero cuando se detecta un estado no coherente en las fases de precarga o de evaluación.

2. Circuito de acuerdo con la reivindicación 1, caracterizado porque la salida del comparador con cero (84) de los módulos de detección está conectada a una conexión oscilante (85) para generar una salida estable (FALLO) , resultado de la detección de estados no coherentes.

3. Circuito protegido por lógica diferencial, preferiblemente definido por una cualquiera de las reivindicaciones 1 ó 2, que procesa variables lógicas representadas por pares de componentes (at, af) (bt, bf) , una primera red de células (T) que realizan funciones lógicas sobre la primera componente de dichos pares, una segunda red de células duales (F) que funcionan en lógica complementaria sobre la segunda componente, estando las funciones lógicas realizadas por cada par de células en una fase de precarga que pone a las variables en un estado conocido en la entrada de las células seguida por una fase de evaluación en la que un cálculo es realizado por las células, comprendiendo dicho circuito una pluralidad de módulos de detección (47) de anomalías colocados en diferentes nodos del circuito, correspondiendo una anomalía a un estado no coherente que se produce durante la fase de precarga o durante la fase de evaluación, produciendo un módulo de detección una señal de salida (FALLO) que indica que se detecta una anomalía a nivel del nodo al que está asociado, caracterizado porque el circuito comprende medios para combinar dichas señales de salidas para generar una señal global de salida (FALLO_GLOBAL) cuyo estado indica que un fallo es detectado por al menos un módulo de detección.

4. Circuito de acuerdo con la reivindicación 3, caracterizado porque las salidas de los módulos de detección (FALLO) se recogen mediante encadenamiento, estando los resultados centralizados en al menos una equipotencial (56, 67) por medio de puertas “O” (53, 54, 63, 64) .

5. Circuito de acuerdo con la reivindicación 4, caracterizado porque la salida de cada cadena de detección está conectada a un una conexión oscilante activada por la señal de reloj del circuito (CLK) y que genera la señal global de salida (FALLO_GLOBAL) que toma el valor 1 cuando al menos un estado no coherente es detectado por uno de los módulos de detección (51, 52, 61, 62) de la cadena.

6. Circuito de acuerdo con la reivindicación 3, caracterizado porque al menos una parte de los módulos de detección del circuito están organizados en árbol (71, 72, 73, 74) , generando el último módulo de detección (74) una señal global que indica si al menos un estado no coherente ha sido detectado en uno de los nodos del circuito controlados por dichos módulos.

7. Circuito de acuerdo con una cualquiera de las reivindicaciones 3 a 6, caracterizado porque un módulo de detección comprende una puerta lógica utilizada para la detección de estados no coherentes que se producen durante la fase de precarga, siendo esta puerta lógica una puerta “O” si el estado coherente es (0, 0) o una puerta “Y” si el estado coherente es (1, 1) .

8. Circuito de acuerdo con una cualquiera de las reivindicaciones 3 a 7, caracterizado porque un módulo de detección comprende una puerta lógica “XNOR” para la detección de estados no coherentes que se producen durante la fase de evaluación.

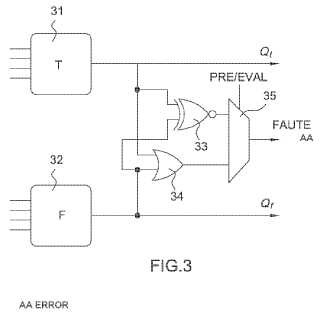

9. Circuito de acuerdo con una cualquiera de las reivindicaciones 3 a 8, caracterizado porque un módulo de detección comprende un multiplexor (35) que permite seleccionar la señal (FALLO) resultante de la detección de estados no coherentes, seleccionándose la salida de la puerta de detección de estados no coherentes en fase de precarga (34) durante la fase de precarga y seleccionándose la salida de la puerta de detección de estados no coherentes en fase de evaluación (33) durante la fase de evaluación, estando la selección controlada por una señal de configuración (PRE/EVAL) .

10. Circuito de acuerdo con una cualquiera de las reivindicaciones anteriores, caracterizado porque el circuito protegido por lógica diferencial es un circuito criptográfico.

11. Circuito de acuerdo con una cualquiera de las reivindicaciones anteriores, caracterizado porque el circuito es un circuito programable de tipo FPGA.

12. Circuito de acuerdo con una cualquiera de las reivindicaciones anteriores, caracterizado por ue el circuito es un circuito de tipo ASIC.

Patentes similares o relacionadas:

Funcionamiento de red de frecuencia única (SFN) para mejoras de cobertura de comunicaciones de tipo máquina (MTC), del 17 de Junio de 2020, de QUALCOMM INCORPORATED: Un procedimiento para comunicaciones de tipo máquina, MTC, inalámbricas realizado por un dispositivo remoto caracterizado por: detectar […]

Método y aparato de procesamiento de servicio, del 3 de Junio de 2020, de Advanced New Technologies Co., Ltd: Un método para el procesamiento de servicios, el método que comprende: después de recibir una solicitud de procesamiento de servicios de un usuario, […]

Dispositivo de a bordo para un vehículo, del 20 de Mayo de 2020, de AUTOSTRADE TECH S.p.A: Dispositivo de a bordo (100, 100', 100") para un vehículo, siendo adecuado dicho dispositivo de a bordo (100, 100', 100") para su uso en un sistema […]

Método para detectar software clonado, del 29 de Abril de 2020, de NAGRAVISION S.A.: Método para detectar un software clonado para ser usado en una unidad de usuario cliente que se comunica con un servidor para solicitar un servicio enviando una solicitud […]

Dispositivo multimedia y procedimiento de transmisión de datos por un dispositivo multimedia, del 18 de Marzo de 2020, de FM Marketing GmbH: Un dispositivo multimedia con un control remoto , que comprende: - un primer microprocesador , - un primer dispositivo de hardware para identificar el control […]

Proceso para asegurar la comunicación de un archivo digital a través de una red de comunicación, del 26 de Febrero de 2020, de AMADEUS S.A.S.: Proceso para comunicar un archivo digital (D1) desde un servidor a un Sistema de Manejo de Información (IHS), comprendiendo el IHS un conjunto […]

Método y aparato para proporcionar entorno virtual personalizado, del 15 de Enero de 2020, de Beijing Xiaomi Mobile Software Co., Ltd: Un método realizado por una plataforma de servicios para proporcionar acceso a una comunidad de servicios que comprende: comparar la información de identificación […]

Procedimiento y dispositivo para controlar la pantalla de seguridad en un dispositivo electrónico, del 28 de Agosto de 2019, de SAMSUNG ELECTRONICS CO., LTD.: Un dispositivo electrónico que comprende: un módulo de representación; una primera memoria que tiene datos de representación almacenados en […]