PROCEDIMIENTO Y APARATO PARA RECONOCER UNA LLAMADA A UNA SUBRUTINA.

Un procedimiento (500) de reconocimiento de una llamada a una subrutina,

que comprende: la detección (510) de un cambio no secuencial en el flujo de un programa; la recuperación (520) de la siguiente dirección secuencial después del cambio no secuencial detectado en el flujo del programa; la comparación (530) de la siguiente dirección secuencial con el contenido de un registro de enlaces para determinar si el cambio no secuencial es una llamada a una subrutina y si se encuentra que la siguiente dirección secuencial es igual que el contenido del registro de enlaces, se empuja (550) la siguiente dirección secuencial o el contenido del registro de enlaces hasta una estructura (134) de pila de enlaces como una dirección de retorno

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2007/085574.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: ATTN: INTERNATIONAL IP ADMINISTRATION 5775 MOREHOUSE DRIVE SAN DIEGO, CALIFORNIA 92121 ESTADOS UNIDOS DE AMERICA.

Inventor/es: MORROW,MICHEAL WILLIAM.

Fecha de Publicación: .

Fecha Solicitud PCT: 27 de Noviembre de 2007.

Fecha Concesión Europea: 13 de Octubre de 2010.

Clasificación Internacional de Patentes:

- G06F9/32B2

- G06F9/38F2B

Clasificación PCT:

- G06F9/38 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Ejecución simultánea de instrucciones, p. ej. segmentación, anticipación.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia.

Fragmento de la descripción:

Campo de la invención

La presente invención se refiere generalmente al campo de los procesadores canalizados y, en particular, a un procedimiento de reconocimiento de una llamada a una subrutina para reducir la energía y aumentar la utilización del procesador canalizado.

Antecedentes

Los microprocesadores realizan tareas computacionales en una amplia variedad de aplicaciones. Casi siempre es deseable un rendimiento mejorado del procesador, para permitir un funcionamiento más rápido y/o una mayor funcionalidad a través de los cambios en el software. En muchas aplicaciones incrustadas, tales como los dispositivos electrónicos portátiles, la conservación de la energía es también un objetivo importante en el diseño e implementación del procesador.

Muchos procesadores de módem emplean una arquitectura canalizada, en la que las instrucciones secuenciales se superponen durante la ejecución para aumentar el rendimiento total del procesador. Con el mantenimiento de una ejecución nivelada a través de ayudas canalizadas se logra un alto rendimiento. La mayoría de los procesadores de módem utilizan también una memoria jerárquica con memorias rápidas de caché en chip que almacenan copias locales de los datos e instrucciones recientemente accedidos.

Los programas del mundo real incluyen instrucciones de bifurcación indirecta, cuyo comportamiento de bifurcación real no se conoce hasta que la instrucción se evalúa en profundidad en la pipeline de ejecución. La mayoría de los procesadores de módem emplean alguna forma de predicción de bifurcación, en la que el comportamiento de bifurcación de instrucciones de bifurcación indirecta se predice anticipadamente en la pipeline, tal como durante una etapa de tubería de búsqueda y carga o de descodificación. Utilizando una técnica de predicción de bifurcación, el procesador de forma especulativa busca y carga la diana de la instrucción de bifurcación indirecta y redirige la pipeline para iniciar el procesamiento de las instrucciones especulativamente cargadas. Cuando se determina la diana de bifurcación real en una etapa de tubería posterior, tal como una etapa de tubería de ejecución, si la bifurcación se predijo erróneamente, las instrucciones especulativamente cargadas deben de eliminarse de la pipeline y cargarse nuevas instrucciones de la dirección de la diana correcta. Las instrucciones de precarga en respuesta a una predicción de diana de bifurcación errónea impactan de forma adversa en el rendimiento del procesador y en el consumo de energía.

Un ejemplo de instrucciones de bifurcación indirecta incluye las instrucciones de bifurcación utilizadas para volver de una subrutina. Por ejemplo, una llamada de retorno desde una subrutina puede incluir una instrucción de bifurcación cuya dirección de retorno esté definida por el contexto de un registro. Una dirección de retorno define la siguiente instrucción a cargar después de que se complete la subrutina y es habitualmente la instrucción después de una instrucción de bifurcación desde la cual se llamó originalmente a la subrutina. Muchas arquitecturas de alto rendimiento designan un registro de propósito general particular para su uso en los retornos de subrutinas, habitualmente denominado registro de enlaces.

Para mayor facilidad, una llamada de retorno también puede denominarse instrucción de retorno de bifurcación. Para que un procesador canalizado utilice predicción de bifurcación para una instrucción de retorno de bifurcación, el software convencional incluye una llamada a subrutina explícita tal como una bifurcación y una instrucción de enlace para grabar la dirección de retorno dentro del registro de enlaces. Muchas implementaciones de alto rendimiento incluyen una estructura de pila de enlaces en la etapa de descodificación del procesamiento de la instrucción de bifurcación y enlace. Los valores de retorno de enlace son empujados dentro de esta pila, para permitir una predicción de bifurcación exacta cuando retornan las subrutinas correspondientes. Las estructuras convencionales de pila de enlaces contienen una lista de direcciones de retorno para soportar múltiples llamadas a subrutinas que fluyen a través de una pipeline y para soportar el anidamiento de múltiples niveles de llamadas a subrutinas. Subsiguientemente, cuando la instrucción de retorno de bifurcación dentro de la subrutina está siendo descodificada, se lee la dirección de retorno de la estructura de pila de enlaces para ser utilizada en la predicción para predecir la dirección diana si otro hardware de predicción de bifurcación dicta que el procesador debe redirigir la pipeline. Si el resultado predicho indica el redireccionamiento de la pipeline, la pipeline inicia la carga de instrucciones de la dirección de retorno que se leyó de la estructura de la pila de enlaces.

Sin embargo, existen muchos compiladores y código heredado que no generan o incorporan

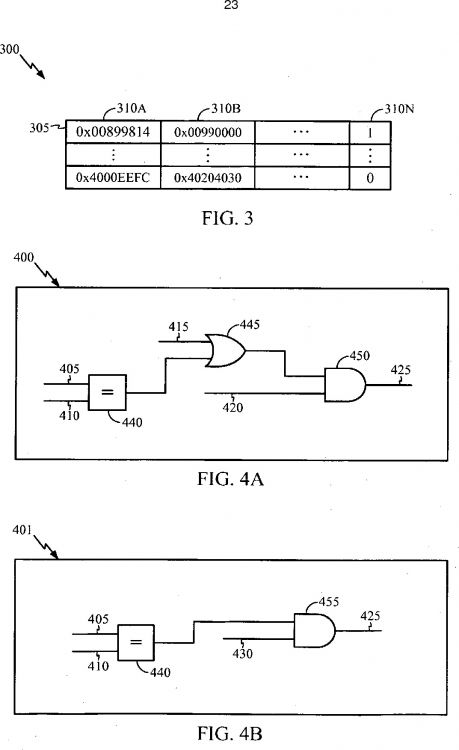

instrucciones convencionales de bifurcación y enlace cuando llaman a una subrutina. Por lo tanto, en esas situaciones, no se utiliza la estructura de la pila de enlaces dando como resultado que la integridad de la estructura de la pila de enlaces quede comprometida. Por ejemplo, la canalización convencional de una dirección de retorno de una estructura de pila 5 de enlaces puede que no esté correlacionada con la instrucción de retorno que estimuló el despliegue de la dirección de retorno en primer lugar. Un efecto de una estructura de pila de enlaces comprometida incluye mayores predicciones erróneas en las instrucciones de retorno. Además, en aquellas situaciones en las que no se reconoce una llamada a una subrutina en un segmento de programa, el problema se acrecienta ya que el hardware de predicción de bifurcación no puede utilizarse para poblar las instrucciones de la pila de enlaces en las subsiguientes llamadas a subrutinas no reconocibles. A modo de ejemplo, remítase a la siguiente tabla que contiene un segmento de código que podría ejecutarse sobre un procesador compatible ARM Ltd.:

0x00899808 LDR LR, 0X00899818

0X008998C ADD

0X0089981 0 SUB

0X0089981 4 BR 0X00990000

0X0089981 8 INSTRA

0X0089981 C INSTRB

…

0X00990000 ADD

0X00990004 SUB

0X00990008 MOV

0X0099000C BX LR

15 El flujo del programa del segmento de código de la tabla 1 incluye el procesamiento de las instrucciones en orden secuencial empezando en la dirección 0x00899808 y hasta la dirección 0x00899814, En la dirección 0x00899814, una instrucción de bifurcación cambia el flujo del programa de forma que la siguiente instrucción procesada se sitúa en la dirección 0x00990000, el inicio de una subrutina.

La combinación de la configuración del registro de enlaces (es decir, LDR LR 0x00899818) y de la instrucción de bifurcación (es decir BR) prepara al procesador para una bifurcación subsiguiente hacia una subrutina. En este ejemplo, la subrutina real a la cual se efectúa la llamada empieza en la dirección 0x00990000 y termina en la dirección 0x009900. La instrucción LDR LR, 0x00899818 indica que la dirección 0x00899818 debe copiarse dentro del registro de enlaces (LR) dando como resultado el almacenamiento de la dirección de retorno, la dirección 0x00899818, dentro del registro de enlaces. Al final de la subrutina, se recupera la dirección de retorno del registro de enlaces. Más específicamente, la dirección de retorno se recupera cuando se ejecuta BX LR, la instrucción de retorno de bifurcación. Existen otros segmentos de código que implican una llamada a una subrutina e incluyen instrucciones que modifican el registro de enlaces tal como la combinación secuencial de las instrucciones MOV LR, PC BR[A] donde [A] es la dirección el inicio de una subrutina.

RESUMEN

La presente invención reconoce la omnipresencia de dicho software heredado, compiladores que producen segmentos de código que tienen dos o más instrucciones que se corresponden con una llamada a una subrutina, así como el coste implicado en la reescritura del software heredado para utilizar instrucciones de bifurcación y enlace convencionales cuando se llama a una subrutina. Además, la presente invención reconoce la necesidad de que los microprocesadores desarrollados hoy en día reconozcan las secuencias de instrucciones que implican una llamada a una subrutina para utilizar una estructura de pila de enlaces y predecir de forma efectiva la dirección de retorno cuando se ejecuta una instrucción de retorno...

Reivindicaciones:

1. Un procedimiento (500) de reconocimiento de una llamada a una subrutina, que comprende:

la detección (510) de un cambio no secuencial en el flujo de un programa; la recuperación (520) de la siguiente dirección secuencial después del cambio no secuencial detectado en el flujo del programa; la comparación (530) de la siguiente dirección secuencial con el contenido de un registro de enlaces para determinar si el cambio no secuencial es una llamada a una subrutina y si se encuentra que la siguiente dirección secuencial es igual que el contenido del registro de enlaces, se empuja (550) la siguiente dirección secuencial o el contenido del registro de enlaces hasta una estructura (134) de pila de enlaces como una dirección de retorno.

2. El procedimiento de la reivindicación 1, en el que el cambio no secuencial en el flujo del programa es una instrucción de bifurcación.

3. El procedimiento de la reivindicación 1, que comprende además:

la indicación (540) de que el cambio no secuencial en el flujo del programa es una llamada a una subrutina.

4. El procedimiento de la reivindicación 3, en el que la indicación (540) de que el cambio no secuencial en el flujo del programa es una subrutina comprende:

el almacenamiento de un marcador en un circuito (132) de predicción de bifurcación asociado con el cambio no secuencial en el flujo del programa.

5. Un aparato (114) para reconocer una llamada a una subrutina que comprende:

medios para detectar (510) un cambio no secuencial en el flujo de un programa; medios para recuperar (520) la siguiente dirección secuencial después del cambio no secuencial detectado en el flujo del programa y medios para comparar(530) la siguiente dirección secuencial con el contenido de un registro de enlaces para determinar si el cambio no secuencial es una llamada a una subrutina y si se encuentra que la siguiente dirección secuencial es igual al contenido del registro de enlaces, medios para empujar (550) la siguiente dirección secuencial o el contenido del registro de enlaces hasta una estructura (134) de pila de enlaces como la dirección de retorno.

6. El aparato de la reivindicación 5, en el que el cambio no secuencial en el flujo del programa es una instrucción de bifurcación.

7. El aparato de la reivindicación 5, que comprende además:

medios para indicar (540) que el cambio no secuencial en el flujo del programa es una llamada a una subrutina.

8. El aparato de la reivindicación 5, en el que los medios para indicar (540) que el cambio no secuencial en el flujo del programa es una subrutina comprenden:

medios para almacenar un marcador en un circuito de predicción de bifurcación asociado con el cambio no secuencial en el flujo del programa.

9. Un aparato para reconocer una llamada a una subrutina, que comprende:

un procesador canalizado para procesar instrucciones y un aparato como el reivindicado en cualquiera de las reivindicaciones 5, 7 y 8.

Patentes similares o relacionadas:

SUPRESIÓN DE LA ACTUALIZACIÓN DE UN REGISTRO DEL HISTÓRICO DE RAMIFICACIONES POR RAMIFICACIONES DE FIN DE BUCLE, del 1 de Febrero de 2011, de QUALCOMM INCORPORATED: Procedimiento de predicción de ramificación, caracterizado porque comprende la supresión de una actualización de un Registro de Histórico de Ramificación […]

Control de ejecución de hilos en un procesador multihilo, del 24 de Junio de 2020, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para controlar la ejecución de hilos en un entorno informático, comprendiendo dicho método: detener , mediante un hilo […]

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Predicados uniformes en sombreadores para unidades de procesamiento de gráficos, del 11 de Diciembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para procesar datos, comprendiendo el procedimiento: recibir una indicación de que todos los subprocesos de una urdimbre […]

Aumento de protocolo de coherencia para indicar estado de transacción, del 4 de Diciembre de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método implementado por ordenador para implementar un protocolo de coherencia, comprendiendo el método: enviar , por un procesador (112a) solicitante, […]

Método y aparato para un acceso a memoria basado en hilos en un procesador multihilo, del 11 de Septiembre de 2019, de QUALCOMM INCORPORATED: Método para acceder a una memoria por un procesador multihilo , comprendiendo el método: determinar un identificador de hilo asociado a un […]

Procedimientos y aparatos para predecir la no ejecución de instrucciones de no bifurcación condicional, del 15 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para manejar una instrucción de no bifurcación condicional, que comprende: identificar una instrucción […]

Procesamiento transaccional, del 17 de Abril de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método de controlar la ejecución de una transacción en un entorno informático, comprendiendo el método los pasos de: Iniciar, mediante un procesador, la ejecución […]