METODOS Y APARATO PARA LA EJECUCION MULTIPROCESO DE INSTRUCCIONES INFORMATICAS.

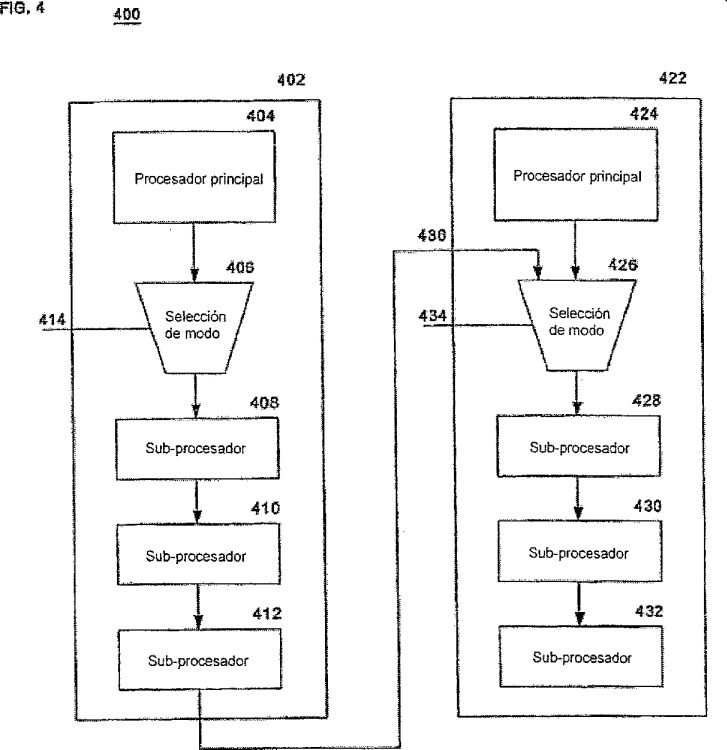

Un sistema (100) informático multiproceso, que comprende: un procesador (202) principal operable para gestionar el procesado de bucles de instrucciones de un programa,

incluyendo cada bucle de instrucciones una o más sub-instrucciones; y una pluralidad de sub-procesadores (204, 206) operables para procesar cada sub-instrucción en una pluralidad de etapas secuenciales, caracterizado porque al menos un primer sub-procesador (204) es operable para recibir secuencialmente la o las sub-instrucciones del procesador (202) principal y para propagar la sub-instrucción a un subprocesador (206) subsiguiente, y al menos un segundo sub-procesador es operable para recibir secuencialmente la o las sub-instrucciones del primer sub-procesador; donde el procesador (202) principal y la pluralidad de sub-procesadores (204, 206) están dispuestos juntos en cascada de modo que diferentes sub-procesadores son operables para ejecutar diferentes operaciones relativas a diferentes iteraciones de bucle respectivas de una sub-instrucción dada durante un ciclo dado; y el procesador principal controla las iteraciones de bucle pasando información a los sub-procesadores

Tipo: Resumen de patente/invención. Número de Solicitud: W0233507US.

Solicitante: SONY COMPUTER ENTERTAINMENT INC..

Nacionalidad solicitante: Japón.

Dirección: 2-6-21, MINAMI-AOYAMA, MINATO-KU,TOKYO 107-0062.

Inventor/es: MAGOSHI,HIDETAKA,SONY COMPUTER ENT. AMERICA INC.

Fecha de Publicación: .

Fecha Concesión Europea: 29 de Julio de 2009.

Clasificación Internacional de Patentes:

- G06F15/78V

- G06F9/32B6

- G06F9/38E

- G06F9/38T

Clasificación PCT:

- G06F15/80 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 15/00 Computadores digitales en general (detalles G06F 1/00 - G06F 13/00 ); Equipo de procesamiento de datos en general. › que comprenden un conjunto de unidades de procesamiento con control común, p. ej. varios procesadores de datos de instrucción única (G06F 15/82 tiene prioridad).

- G06F9/32 G06F […] › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Formación de la dirección de la instrucción siguiente, p. ej. por incremento del contador de instrucción (G06F 9/38 tiene prioridad).

- G06F9/38 G06F 9/00 […] › Ejecución simultánea de instrucciones, p. ej. segmentación, anticipación.

Clasificación antigua:

- G06F15/00 G06F […] › Computadores digitales en general (detalles G06F 1/00 - G06F 13/00 ); Equipo de procesamiento de datos en general.

Patentes similares o relacionadas:

SUPRESIÓN DE LA ACTUALIZACIÓN DE UN REGISTRO DEL HISTÓRICO DE RAMIFICACIONES POR RAMIFICACIONES DE FIN DE BUCLE, del 1 de Febrero de 2011, de QUALCOMM INCORPORATED: Procedimiento de predicción de ramificación, caracterizado porque comprende la supresión de una actualización de un Registro de Histórico de Ramificación […]

MICROPROCESADOR CON SELECCIÓN AUTOMÁTICA DE PARALELISMO SIMD, del 9 de Junio de 2011, de QUALCOMM INCORPORATED: Un procedimiento para controlar el paralelismo de operaciones en un procesador de datos en paralelo, que comprende: monitorizar una o más condiciones […]

USO DEL SISTEMA DE RENOMBRADO DE REGISTROS PARA EL ENVÍO DE LOS RESULTADOS INTERMEDIOS ENTRE INSTRUCCIONES CONSTITUTIVAS DE UNA INSTRUCCIÓN EXPANDIDA, del 21 de Febrero de 2011, de QUALCOMM INCORPORATED: Un procedimiento de ejecución de una instrucción expandida, que comprende: la conversión de la instrucción expandida en dos o más instrucciones […]

USO DEL SISTEMA DE RENOMBRADO DE REGISTROS PARA EL ENVÍO DE LOS RESULTADOS INTERMEDIOS ENTRE INSTRUCCIONES CONSTITUTIVAS DE UNA INSTRUCCIÓN EXPANDIDA, del 21 de Febrero de 2011, de QUALCOMM INCORPORATED: Un procedimiento de ejecución de una instrucción expandida, que comprende: la conversión de la instrucción expandida en dos o más instrucciones […]

APARATO Y METODO PARA PROCESAR DATOS ENCAUZADOS, del 27 de Mayo de 2010, de XELERATED AB: Método de procesamiento encauzado, que comprende una pluralidad de fases (9a-9e) de procesamiento encauzado, caracterizado por las etapas de:

recibir un […]

APARATO Y METODO PARA PROCESAR DATOS ENCAUZADOS, del 27 de Mayo de 2010, de XELERATED AB: Método de procesamiento encauzado, que comprende una pluralidad de fases (9a-9e) de procesamiento encauzado, caracterizado por las etapas de:

recibir un […]

Procesador digital de señales y dispositivo de comunicación de banda base, del 5 de Noviembre de 2018, de MediaTek Sweden AB: Una unidad de ejecución de vectores para su uso en un procesador digital de señales que tiene un núcleo de procesador, […]

Procesador digital de señales y método para direccionar una memoria en un procesador digital de señales, del 18 de Octubre de 2017, de MediaTek Sweden AB: Un procesador digital de señales que comprende al menos una unidad funcional, que puede ser una unidad de ejecución de vectores , o un acelerador, […]

Procesador de señal digital y dispositivo de comunicación de banda base, del 16 de Agosto de 2017, de MediaTek Sweden AB: Un procesador de señal digital que comprende: - un núcleo de procesador que incluye una unidad de ejecución de enteros […]

Arquitectura híbrida SIMD/MIMD dinámicamente reconfigurable de un coprocesador para sistemas de visión, del 4 de Julio de 2013, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), dinámicamente […]

Arquitectura híbrida SIMD/MIMD dinámicamente reconfigurable de un coprocesador para sistemas de visión, del 4 de Julio de 2013, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), dinámicamente […]