SISTEMA MICROPROCESADOR CON UNIDAD DE CONTROL CABLEADA RECONFIGURABL, Y METODO PARA OPERAR UN MICROPROCESADOR.

La invención se refiere a un sistema microprocesador que comprende un microprocesador que comprende un camino de datos (1) y una unidad de control (2) cableada.

El sistema está configurado para, como respuesta a una instrucción de reconfiguración (200), reconfigurar la unidad de control, de manera que la unidad de control,

- antes de recibir dicha instrucción de reconfiguración, está configurada para que el microprocesador procese instrucciones de un programa compilado para una primera arquitectura de procesador, y

- después de recibir dicha instrucción de reconfiguración, se reconfigure para quedar configurada para que el microprocesador procese instrucciones de un programa compilado para una segunda arquitectura de procesador, distinta de la primera arquitectura de procesador

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P200802227.

Solicitante: UNIVERSIDAD REY JUAN CARLOS.

Nacionalidad solicitante: España.

Provincia: MADRID.

Inventor/es: CASTILLO VILLAR,JAVIER, MARTINEZ TORRES,JOSE IGNACIO.

Fecha de Solicitud: 28 de Julio de 2008.

Fecha de Publicación: .

Fecha de Concesión: 15 de Octubre de 2010.

Clasificación Internacional de Patentes:

- G06F9/30 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Disposiciones para ejecutar instrucciones de máquinas, p. ej. decodificación de instrucciones (para ejecutar microinstrucciones G06F 9/22).

Clasificación PCT:

- G06F9/30 G06F 9/00 […] › Disposiciones para ejecutar instrucciones de máquinas, p. ej. decodificación de instrucciones (para ejecutar microinstrucciones G06F 9/22).

Fragmento de la descripción:

Sistema microprocesador con unidad de control cableada reconfigurable, y método para operar un microprocesador.

Campo técnico de la invención

La invención se engloba en el campo de los microprocesadores.

Antecedentes de la invención

En la actualidad la mayor parte de los microprocesadores de propósito general están construidos siguiendo la arquitectura denominada RISC (Reduced Instruction Set Computer). En este tipo de arquitectura, la cantidad de diferentes instrucciones que puede ejecutar el procesador ha sido reducida para simplificar el diseño del procesador.

Básicamente, un procesador RISC comprende dos partes diferenciadas, a saber, la unidad de control y el camino de datos.

- El camino de datos comprende todo el hardware necesario para realizar las tareas que demanda cada instrucción ensamblador o código máquina, incluyendo la unidad aritmético-lógica (ALU: "Arithmetic-Logic Unit") encargada de realizar cálculos, la memoria de instrucciones que contiene el programa a ejecutar, la memoria de datos que contiene los datos con los que opera el programa/procesador, registros (por ejemplo, organizados en un banco de registros), así como una gran cantidad de otros elementos, incluyendo sumadores, desplazadores, multiplexores, etc.

- Por otra parte, la unidad de control (CU: "Control Unit") se encarga de recibir las instrucciones del programa contenidas en la memoria de instrucciones y generar las señales de control necesarias para que el camino de datos realice las operaciones necesarias para ejecutar dichas instrucciones.

Existen diversas formas de implementar físicamente una unidad de control, siendo las más habituales la unidad de control cableada ("hardwired") y la microprogramada ("microprogrammed").

- La unidad de control cableada tiene una configuración básicamente rígida. Mediante circuitos lógicos se interpreta la instrucción y se generan las salidas de control hacia el camino de datos.

- La unidad de control microprogramada contiene en su interior una serie de microinstrucciones que se encargan de detallar los pasos de bajo nivel que debe ejecutar el camino de datos para ejecutar la instrucción.

Generalmente, la unidad de control cableada es mucho más rápida y eficiente en consumo de recursos (área de silicio) y es por tanto la más comúnmente usada en procesadores RISC. Sin embargo, la unidad de control microprogramada dota de mayor flexibilidad al sistema ya que es posible cambiar el microprograma para corregir errores, añadir soporte para nuevas instrucciones o incluso cambiar toda la codificación del juego de instrucciones convirtiendo virtualmente el microprocesador en otro diferente. De esta manera se puede, por ejemplo, cambiar las microinstrucciones contenidas en una unidad de control microprogramada para que el microprocesador, en lugar de ejecutar código o programas compilados para una determinada arquitectura de procesador (por ejemplo, para PowerPC, MIPS, Intel x86, SPARC, ARM, Alpha, etc.) pueda ejecutar programas compilados para otro tipo de arquitectura. Lógicamente, esto hace que el procesador sea mucho más flexible.

Esta flexibilidad de las unidades de control microprogramadas ha sido explotada para diseñar procesadores que puedan ejecutar juegos de instrucciones de diferentes arquitecturas (es decir, programas compilados para diferentes arquitecturas de procesador) únicamente modificando el microprograma. Esto es posible debido a las grandes similitudes existentes entre los juegos de instrucciones de las diferentes arquitecturas, de tal forma que es posible ejecutar todos estos diferentes juegos de instrucciones sobre el mismo camino de datos sin apenas modificaciones. En la práctica puede haber alguna instrucción de un juego de instrucciones que no se pueda ejecutar sobre un determinado camino de datos originalmente configurado para otra arquitectura de procesador; por lo tanto, puede ser conveniente, para mayor flexibilidad, que el camino de datos disponga del hardware adicional para ejecutar esa instrucción. Por lo tanto, para disponer de una flexibilidad máxima el procesador debe tener un camino de datos que contenga el conjunto de hardware necesario para ejecutar el mayor número posible de juegos de instrucciones diferentes sin modificaciones. Es decir, puede tratarse de un camino de datos que representa un "superconjunto" de los caminos de datos de diferentes procesadores, por ejemplo, de los diferentes procesadores RISC.

US-A-2004/0133770 (Pappalardo, et al.) describe un procesador que comprende dos unidades de control, una cableada (con las ventajas que ello implica en cuanto a rapidez y consumo de recursos) y otra microprogramada (con las ventajas que ello implica en cuanto a flexibilidad). Por lo tanto, el microprocesador puede adaptarse a programas compilados para otras arquitecturas (distintas de las que originalmente se han previsto al diseñar la unidad de control cableada) modificando la programación de la unidad de control microprogramada. Por lo tanto, en un principio, se combinan las ventajas de ambos tipos de unidad de control, aunque con la desventaja de tener que disponer de dos unidades de control, lo cual implica una mayor cantidad de hardware, con las desventajas que ello implica en cuanto a, por ejemplo, el uso de superficie.

WO-A-2007/015258 (Gopi, et al.) hace referencia a una unidad de control configurable. Para ello, se ha previsto un juego de instrucciones con cierta capacidad de configuración. Para ciertas aplicaciones puede ser interesante cambiar el comportamiento de algunas instrucciones y para ello cada instrucción tiene un campo con atributos que cambia la respuesta de la unidad de control a dicha instrucción. La unidad de control interpreta dichos atributos y ejecuta esa instrucción de forma diferente en función del atributo. Es decir, el juego de instrucciones presenta unos campos especiales que son capaces de modificar algunas propiedades de esa unidad de control, como por ejemplo el tiempo que la instrucción tarda en ejecutarse. Esta funcionalidad está soportada por un hardware adicional en la unidad de control.

Descripción de la invención

Un primer aspecto de la invención se refiere a un sistema microprocesador que comprende un microprocesador que comprende:

(i) un camino de datos que comprende, al menos, una unidad aritmético-lógica, registros, una memoria de instrucciones configurada para contener instrucciones de un programa que el microprocesador debe ejecutar, y una memoria de datos configurada para contener datos con los que pueda operar el programa; y

(ii) una unidad de control configurada para recibir instrucciones de programa de la memoria de instrucciones y para generar señales de control y aplicarlas al camino de datos de manera que se realicen, en el camino de datos, operaciones de acuerdo con las instrucciones de programa; esta unidad de control es una unidad de control cableada.

De acuerdo con la invención, el sistema está configurado para, como respuesta a una instrucción de reconfiguración contenida en las instrucciones de programa, reconfigurar la unidad de control, de manera que la unidad de control,

- que antes de recibir dicha instrucción de reconfiguración estaba configurada para que el microprocesador procese instrucciones de un programa compilado para una primera arquitectura de procesador,

- después de recibir dicha instrucción de reconfiguración se reconfigure para quedar configurada para que el microprocesador procese instrucciones de un programa compilado para una segunda arquitectura de procesador, distinta de la primera arquitectura de procesador.

De esta manera, se consigue combinar la flexibilidad de los microprocesadores con unidad de control microprogramada con la rapidez y bajo consumo de los microprocesadores con unidad de control cableada. Es decir, se consigue un sistema que combina lo mejor de ambos conceptos. Por lo tanto, se puede, cuando sea conveniente, cambiar la configuración lógica de la unidad de control para que el microprocesador, que antes estaba configurado para procesar instrucciones de un programa compilado para una arquitectura de procesador, pase a estar configurado para procesar, correctamente, instrucciones de un programa compilado para otra arquitectura de procesador. Ejemplos de arquitecturas de procesador son: PowerPC, MIPS, Intel x86, SPARC, ARM, Alpha, etc.

Por ejemplo:

1) En la arquitectura MIPS la instrucción de suma se codifica de la siguiente forma:

add, rt,rs,rd

donde...

Reivindicaciones:

1. Sistema microprocesador que comprende un microprocesador que comprende:

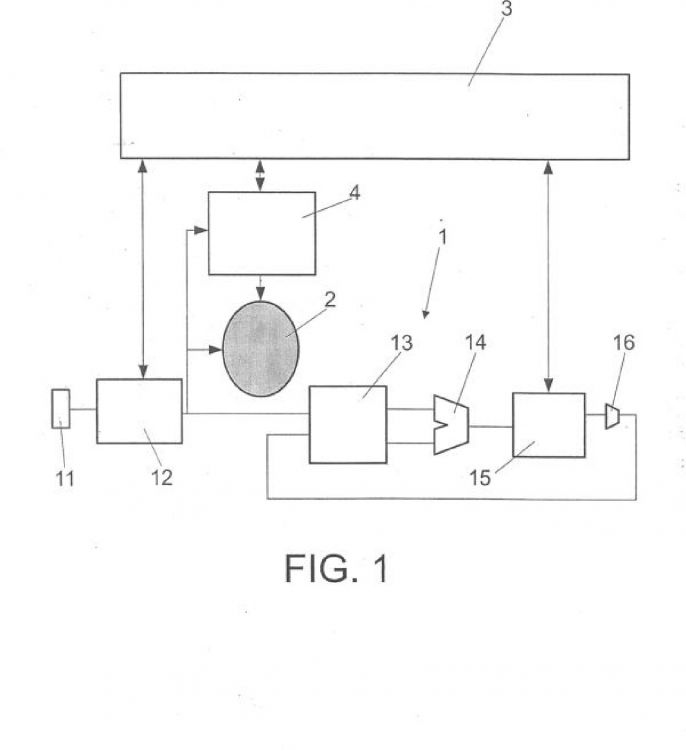

un camino de datos (1) que comprende, al menos, una unidad aritmético-lógica (14), registros (13), una memoria de instrucciones (12) configurada para contener instrucciones de un programa que el microprocesador debe ejecutar, y una memoria de datos (15) configurada para contener datos con los que pueda operar el programa; y

una unidad de control (2) configurada para recibir instrucciones de programa de la memoria de instrucciones (12) y para generar señales de control y aplicarlas al camino de datos (1) de manera que se realicen, en el camino de datos, operaciones de acuerdo con las instrucciones de programa;

siendo la unidad de control (2) una unidad de control cableada;

caracterizado porque

el sistema está configurado para, como respuesta a una instrucción de reconfiguración (200) contenida en las instrucciones de programa, reconfigurar la unidad de control, de manera que la unidad de control,

- antes de recibir dicha instrucción de reconfiguración, está configurada para que el microprocesador procese instrucciones de un programa compilado para una primera arquitectura de procesador, y

- después de recibir dicha instrucción de reconfiguración, se reconfigure para quedar configurada para que el microprocesador procese instrucciones de un programa compilado para una segunda arquitectura de procesador, distinta de la primera arquitectura de procesador.

2. Sistema según la reivindicación 1, caracterizado porque comprende una memoria (3) que contiene al menos dos conjuntos de datos indicativos de respectivas configuraciones lógicas de la unidad de control (2).

3. Sistema según la reivindicación 2, caracterizado porque comprende un dispositivo reconfigurador (4) configurado para, como respuesta a la instrucción de reconfiguración, modificar la configuración de la unidad de control de acuerdo con los datos de uno de dichos conjuntos de datos.

4. Sistema según cualquiera de las reivindicaciones anteriores, caracterizado porque la unidad de control está implementada en un dispositivo de lógica programable.

5. Sistema según cualquiera de las reivindicaciones 1-3, caracterizado porque la unidad de control está implementada en un circuito ASIC que comprende al menos una parte de lógica reconfigurable correspondiente a la unidad de control.

6. Sistema según cualquiera de las reivindicaciones anteriores, caracterizado porque está configurado para cambiar la configuración de la unidad de control repetitivamente para, durante un período de funcionamiento, operar con programas compilados para diferentes arquitecturas, con el fin de dificultar un análisis de la operación del microprocesador a partir de un análisis del consumo energético del sistema.

7. Sistema según cualquiera de las reivindicaciones anteriores, caracterizado porque está configurado para realizar cambios de la configuración de la unidad de control repetitivamente para, durante un período de funcionamiento, operar con programas compilados para diferentes arquitecturas, realizándose dichos cambios de forma aleatoria o pseudoaleatoria.

8. Método para operar un microprocesador que comprende:

un camino de datos (1) que comprende, al menos, una unidad aritmético-lógica (14), registros (13), una memoria de instrucciones (12) configurada para contener instrucciones de un programa que el microprocesador debe ejecutar, y una memoria de datos (15) configurada para contener datos con los que pueda operar el programa; y

una unidad de control (2) configurada para recibir instrucciones de programa de la memoria de instrucciones (12) y para generar señales de control y aplicarlas al camino de datos (1) de manera que se realicen, en el camino de datos, operaciones de acuerdo con las instrucciones de programa;

siendo la unidad de control (2) una unidad de control cableada;

caracterizado porque

el método comprende los pasos de

como respuesta a una instrucción de reconfiguración (200) contenida en las instrucciones de programa, reconfigurar la unidad de control, de manera que la unidad de control

- pase de estar configurada para que el microprocesador procese instrucciones de un programa compilado para una primera arquitectura de procesador,

- a estar configurada para que el microprocesador procese instrucciones de un programa compilado para una segunda arquitectura de procesador, distinta de la primera arquitectura de procesador.

9. Método según la reivindicación 8, caracterizado porque el paso de reconfigurar la unidad de control se realiza accediendo a datos indicativos de configuración lógica de la unidad de control alojados en una memoria (3) que contiene al menos dos conjuntos de datos indicativos de respectivas configuraciones lógicas de la unidad de control.

10. Método según la reivindicación 9, caracterizado porque como respuesta a la instrucción de reconfiguración se accede a uno de dichos conjuntos de datos y, mediante un dispositivo hardware, se reconfigura la unidad de control de acuerdo con dicho conjunto de datos.

11. Método según cualquiera de las reivindicaciones 8-10, caracterizado porque la reconfiguración se realiza sobre una unidad de control implementada en un dispositivd de lógica programable.

12. Método según cualquiera de las reivindicaciones 8-10, caracterizado porque la reconfiguración se realiza sobre una unidad de control implementada en un circuito ASIC que comprende al menos una parte de lógica reconfigurable correspondiente a la unidad de control.

13. Método según cualquiera de las reivindicaciones 8-12, que comprende el paso de reconfigurar repetitivamente la unidad de control para que el microprocesador opere, en diferentes momentos de un periodo de funcionamiento del microprocesador, con programas compilados para diferentes arquitecturas de microprocesador.

14. Método según la reivindicación 13, caracterizado porque durante dicho período de funcionamiento se reconfigura la unidad de control de forma aleatoria o pseudoaleatoria.

15. Método según cualquiera de las reivindicaciones 8-14, que comprende el paso de, como respuesta a la instrucción de reconfiguración pero antes reconfigurar la unidad de control, terminar el procesamiento de instrucciones recibidas antes de la recepción de la instrucción de reconfiguración.

16. Uso de un dispositivo según cualquiera de las reivindicaciones 1-7, para dificultar un análisis de la operación del microprocesador a partir de un análisis del consumo energético del sistema.

17. Uso del método según cualquiera de las reivindicaciones 8-15, con el fin de dificultar un análisis de la operación del microprocesador a partir de un análisis del consumo energético del sistema.

Patentes similares o relacionadas:

Método y equipo para realizar una reorganización de bits de un vector, del 29 de Julio de 2020, de INTEL CORPORATION: Un procesador que comprende:

un decodificador para decodificar una instrucción de reorganización de bits de un vector, comprendiendo […]

Método y equipo para realizar una reorganización de bits de un vector, del 29 de Julio de 2020, de INTEL CORPORATION: Un procesador que comprende:

un decodificador para decodificar una instrucción de reorganización de bits de un vector, comprendiendo […]

Control de ejecución de hilos en un procesador multihilo, del 24 de Junio de 2020, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para controlar la ejecución de hilos en un entorno informático, comprendiendo dicho método: detener , mediante un hilo […]

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Operaciones SIMD de anchura mixta que tienen operaciones de elementos pares y de elementos impares usando un par de registros para elementos de datos anchos, del 25 de Marzo de 2020, de QUALCOMM INCORPORATED: Un procedimiento para realizar una operación de tipo "una instrucción, múltiples datos" (SIMD) de anchura mixta, comprendiendo el procedimiento: recibir , […]

Transformar especificadores de instrucción no contiguos a especificadores de instrucción contiguos, del 19 de Febrero de 2020, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un producto de programa informático para emular instrucciones en un entorno informático, comprendiendo el producto de programa informático: un medio de almacenamiento […]

Predicados uniformes en sombreadores para unidades de procesamiento de gráficos, del 11 de Diciembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para procesar datos, comprendiendo el procedimiento: recibir una indicación de que todos los subprocesos de una urdimbre […]

Aumento de protocolo de coherencia para indicar estado de transacción, del 4 de Diciembre de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método implementado por ordenador para implementar un protocolo de coherencia, comprendiendo el método: enviar , por un procesador (112a) solicitante, […]

Procedimientos y aparatos para predecir la no ejecución de instrucciones de no bifurcación condicional, del 15 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para manejar una instrucción de no bifurcación condicional, que comprende: identificar una instrucción […]