SISTEMA DE MATRIZ DE CONMUTACION CON ARBITRAJES DE BUS PLURALES POR CICLO MEDIANTE UN ARBITRO DE FRECUENCIA SUPERIOR.

Un sistema de matriz cruzada (30), que comprende:

un bus que funciona a una frecuencia de bus;

al menos un dispositivo maestro (34) conectado al bus y que solicita transacciones de bus dirigidas a al menos un dispositivo esclavo (36) conectado al bus y que se involucra en transacciones de bus; y

que se caracteriza por comprender además

un árbitro capaz de arbitrar más de una solicitud de transacción de bus en un único ciclo de reloj de frecuencia de bus al funcionar a una frecuencia de árbitro superior a la frecuencia de bus

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2006/006649.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 5775 MOREHOUSE DRIVE,SAN DIEGO, CA 92121.

Inventor/es: GANASAN,JAYA PRAKASH SUBRAMANIAM.

Fecha de Publicación: .

Fecha Concesión Europea: 14 de Julio de 2010.

Clasificación Internacional de Patentes:

- G06F13/40D2

- H04L12/56S1A

Clasificación PCT:

- G06F13/40 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 13/00 Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16). › Estructura del bus.

Clasificación antigua:

- G06F13/40 G06F 13/00 […] › Estructura del bus.

Fragmento de la descripción:

Sistema de matriz de conmutación con arbitrajes de bus plurales por ciclo mediante un árbitro de frecuencia superior.

Antecedentes

La presente invención se refiere generalmente al campo del procesamiento de datos electrónicos, y en particular a un sistema y a un procedimiento para el arbitraje de bus de alto rendimiento.

La transferencia de datos entre unidades funcionales es una operación común en los sistemas de ordenador. Transferir un programa de disco a memoria a un procesador; enviar datos de un motor gráfico a una memoria intermedia a una tarjeta de vídeo; y enviar una entrada de un teclado o un ratón a un procesador son todos ellos ejemplos habituales de transferencia de datos en un sistema de ordenador.

La figura 1 muestra un diagrama simplificado de una arquitectura de bus de un sistema, indicado de manera general por el número 10. Un bus del sistema 12, que puede ser dividido en un canal de direcciones, un canal de datos, un canal de control y similares, interconecta unidades del sistema. Los dispositivos maestros, tales como la CPU 14 o un motor DMA 16, inician la transferencia de datos, denominadas aquí como transacciones de bus, a través del bus 12 a o desde dispositivos esclavos, tales como una memoria 18 y circuitos de entrada/salida 20. Cuando dos o más maestros 14, 16 independientes están conectados al bus 12, su acceso al bus se controla mediante un árbitro 22.

Como es conocido en la técnica, uno o más dispositivos maestros 14, 16 declaran una solicitud de bus al árbitro 22. El árbitro 22 monitoriza la actividad sobre el bus 12, y cuando el bus 12 se encuentra disponible, envía una asignación de bus a uno de los dispositivos maestros 14, 16 solicitantes. El dispositivo maestro 14, 16 al que se le ha asignado acceso puede entonces iniciar transacciones a través del bus 12, tales como ciclos de lectura o escritura dirigidos a uno o más de los dispositivos esclavos 18, 20.

Aunque el bus del sistema 10 funciona bien para conectar unos pocos dispositivos maestros 14, 16 con una variedad de dispositivos esclavos 18, 20, impone la limitación de que tan sólo uno de los dispositivos maestros 14, 16 puede acceder a un dispositivo esclavo 18, 20 a la vez. En procesadores de alto rendimiento, a menudo se da el caso de que dos o más dispositivos maestros 14, 16 pueden desear un acceso independiente a uno o más dispositivos esclavos 18, 20.

La figura 2 muestra un sistema de transferencia de datos de alto rendimiento, indicado generalmente por el número 30. Una matriz de conmutación 32, conocida asimismo como conmutador de barras cruzadas, interconecta una pluralidad de dispositivos maestros 34 con una pluralidad de dispositivos esclavos 36, teniendo cualquier dispositivo maestro acceso cualquier dispositivo esclavo en el caso más general. Por ejemplo, la figura 2 muestra al maestro 1 accediendo al esclavo 1, y simultáneamente, al maestro 2 accediendo al esclavo 0. En algunas implementaciones, uno o más de los dispositivos esclavos 36 puede incluir dos o más buses de direcciones, lo que permite un acceso simultáneo por más de un dispositivo maestro 34.

Para un sistema de bus 30 que comprende n dispositivos maestros 34 y un único dispositivo esclavo 36, tan sólo se necesita un árbitro en la matriz de conmutación 32 para arbitrar accesos en competencia al dispositivo esclavo 36. Para un sistema de n x m barras cruzadas 30, con n maestros 34 y m esclavos 36, se puede implementar de uno a m árbitros. El mayor rendimiento se conseguirá con m árbitros, con cada árbitro dedicado a un dispositivo esclavo 36. Con menos de m árbitros, esto es, con al menos un árbitro realizando el arbitraje para dos o más dispositivos esclavos 36, el rendimiento se degradará, ya que cada árbitro puede arbitrar tan sólo a un dispositivo esclavo 36 a la vez, o dentro de un ciclo de bus dado. Sin embargo, producir muchos árbitros consume área de chip, complica el enrutamiento, y aumenta el consumo de potencia.

Un conmutador de barras cruzadas con una lógica de árbitro dedicada a cada puerto esclavo es conocido del documento de patente US 2005/0027920.

Resumen

De acuerdo con uno o más modos de realización, un árbitro en un bus arbitra múltiples solicitudes de transacciones de bus en un único ciclo de reloj de frecuencia de bus, al funcionar a una frecuencia de árbitro superior a la frecuencia de bus.

En un modo de realización, un sistema incluye un bus que funciona a una frecuencia de bus. Al menos un dispositivo maestro está conectado al bus y solicita transacciones de bus. Al menos un dispositivo esclavo está conectado al bus y se involucra en transacciones de bus. Un árbitro arbitra más de una solicitud de transacción en un único ciclo de reloj de frecuencia de bus al funcionar a una frecuencia de árbitro superior a la frecuencia de bus.

En otro modo de realización, un procedimiento para arbitrar múltiples solicitudes de transacción de bus en un bus que funciona a una frecuencia de bus comprende operar un árbitro a una frecuencia de árbitro superior a la frecuencia de bus, y arbitrar múltiples solicitudes de transacciones de bus en un ciclo de reloj de frecuencia de bus.

Breve descripción de los dibujos

La figura 1 es un diagrama de bloques funcionales de un bus de ordenador del estado de la técnica anterior.

La figura 2 es un diagrama de bloques funcionales de un bus de barras cruzadas.

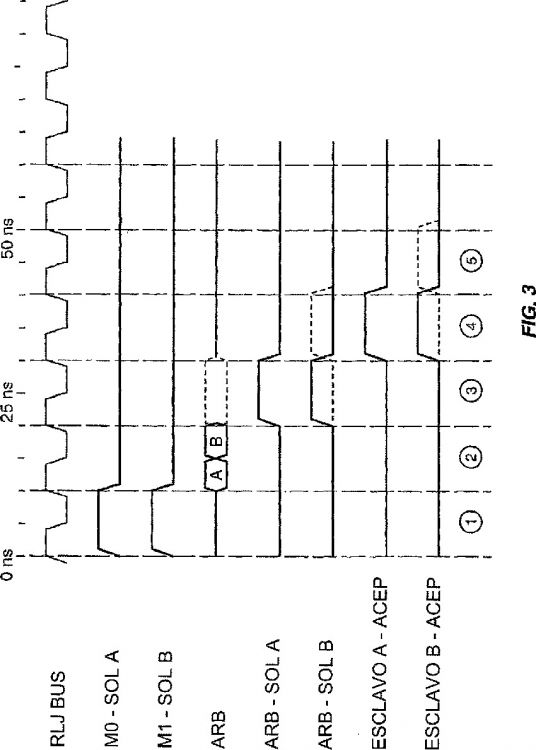

La figura 3 es un diagrama temporal de un ciclo de arbitraje de bus de barras cruzadas.

Descripción detallada

La figura 3 muestra un diagrama temporal de solicitudes de transacciones de bus representativas y arbitraje en un sistema de matriz cruzada 30. En este ejemplo, el bus funciona a una frecuencia de bus de 100 MHz, con un ciclo de reloj de 10 ns, y dos dispositivos esclavos A y B comparten un único árbitro. Dos dispositivos maestros emiten simultáneamente solicitudes de transacciones de bus dirigidas a dos dispositivos esclavos, A y B, en el ciclo de bus 1.

En un sistema 30 que tiene un árbitro convencional, el arbitraje se llevaría a cabo para el dispositivo esclavo A en el ciclo de bus 2, y para el dispositivo esclavo B en el ciclo de bus 3, como se indica mediante las líneas de puntos. El árbitro emitiría una solicitud al dispositivo esclavo A en el ciclo de bus 3 y al dispositivo esclavo B en el ciclo de bus 4, como se indica por las líneas de puntos. Los dispositivos esclavos aceptarían en los ciclos de bus 4 y 5 respectivamente, y los dispositivos maestros M0 y M1 procederían con la transacción de bus una vez recibida la aceptación de cada dispositivo esclavo respectivo.

En uno o más modos de realización, se llevan a cabo múltiples ciclos de arbitraje en un ciclo de reloj de frecuencia de bus haciendo funcionar al árbitro a una frecuencia de árbitro superior a la frecuencia de bus. Como se muestra en las señales de línea continua de la figura 3, el árbitro realiza un arbitraje para ambos dispositivos esclavos A y B en el ciclo de bus 2, al funcionar (en este modo de realización) a una frecuencia de árbitro que es dos veces la frecuencia de bus. Así pues, el árbitro es capaz de emitir solicitudes a ambos dispositivos esclavos A y B en el ciclo de bus 3, y ambos dispositivos esclavos A y B pueden aceptar en el ciclo de bus 4. Tanto M0 como M1 pueden comenzar transacciones de bus en el ciclo de bus 5, el cual en el caso de M1 es un ciclo completo antes que en el caso descrito anteriormente, y mostrado en la figura 3 en línea de puntos, en donde el árbitro funciona a la frecuencia de bus. De modo similar, al funcionar el árbitro a 3x, 4x u otro múltiplo de la frecuencia de bus, las solicitudes dirigidas a tres, cuatro o más esclavos pueden ser arbitradas en un único ciclo de reloj de frecuencia de bus, lo que permite que las respectivas transacciones de bus se procesen en paralelo.

En estos modos de realización, una única instancia de un árbitro puede arbitrar múltiples solicitudes de transacciones de bus para múltiples esclavos en paralelo, sin requerir duplicar instancias de la lógica de arbitraje. Como se utiliza en la presente memoria, una instancia única de un árbitro comprende la lógica y la información de configuración necesarias para realizar un arbitraje de una o más solicitudes de transacciones de bus dirigidas a un dispositivo esclavo 36. Al hacer funcionar a un árbitro a una frecuencia de árbitro superior a la frecuencia de bus, se pueden arbitrar múltiples solicitudes de transacciones de bus en un único ciclo de reloj de frecuencia de bus, utilizando tan sólo una instancia de...

Reivindicaciones:

1. Un sistema de matriz cruzada (30), que comprende:

un bus que funciona a una frecuencia de bus;

al menos un dispositivo maestro (34) conectado al bus y que solicita transacciones de bus dirigidas a al menos un dispositivo esclavo (36) conectado al bus y que se involucra en transacciones de bus; y

que se caracteriza por comprender además

un árbitro capaz de arbitrar más de una solicitud de transacción de bus en un único ciclo de reloj de frecuencia de bus al funcionar a una frecuencia de árbitro superior a la frecuencia de bus.

2. El sistema de matriz cruzada de la reivindicación 1 en el que el árbitro comprende una única instantación de lógica de arbitraje.

3. El sistema de matriz cruzada de la reivindicación 1, en el que la frecuencia de árbitro es un múltiplo de la frecuencia de bus.

4. El sistema de matriz cruzada de la reivindicación 1 en el que:

el dispositivo esclavo incluye al menos dos trayectorias de direcciones;

dos dispositivos maestros solicitan simultáneamente transacciones de bus al dispositivo esclavo; y

el árbitro emite asignaciones a ambos dispositivos maestros en un único ciclo de reloj de frecuencia de bus.

5. El sistema de matriz cruzada de la reivindicación 1, en el que

el dispositivo maestro solicita simultáneamente transacciones de bus a dos dispositivos esclavos; y

el árbitro emite asignaciones a los dispositivos maestros para ambos dispositivos esclavos en un único ciclo de reloj de frecuencia de bus.

6. El sistema de matriz cruzada de la reivindicación 1, en el que, si no se declara más de una solicitud de transacción de bus, la frecuencia de árbitro es igual a la frecuencia de bus.

7. El sistema de matriz cruzada de la reivindicación 1, en el que la frecuencia de árbitro se predice como respuesta a una actividad de solicitud de transacciones de bus.

8. El sistema de matriz cruzada de la reivindicación 1, en el que el árbitro arbitra secuencialmente al menos una primera y una segunda solicitud de transacción de bus en un único ciclo de reloj de frecuencia de bus, y en el que el arbitraje de la segunda solicitud incluye el resultado del arbitraje de la primera solicitud.

9. El sistema de matriz cruzada de la reivindicación 8, en el que el árbitro mantiene el estado de las transacciones de bus pendientes.

10. Un procedimiento para arbitrar múltiples solicitudes de transacción de bus, que comprende:

proporcionar un árbitro capaz de funcionar a una frecuencia de árbitro superior a la frecuencia de bus; y

arbitrar múltiples solicitudes de transacción de bus en un ciclo de reloj de frecuencia de bus.

11. El procedimiento de la reivindicación 10, en el que la frecuencia del árbitro es un múltiplo de la frecuencia de bus.

12. El procedimiento de la reivindicación 11, en el que el árbitro arbitra una solicitud de transacción de bus en cada ciclo de reloj de frecuencia de árbitro.

13. El procedimiento de la reivindicación 12, en el que el árbitro arbitra secuencialmente al menos una primera y una segunda solicitud de transacción de bus en un único ciclo de reloj de frecuencia de bus, y en el que el arbitraje de la segunda solicitud incluye el resultado del arbitraje de la primera solicitud.

14. El procedimiento de la reivindicación 13, en el que el árbitro mantiene el estado de las transacciones de bus pendientes.

15. El procedimiento de la reivindicación 10, en el que la frecuencia de árbitro es variable.

16. El procedimiento de la reivindicación 15 en el que la frecuencia de árbitro se predice en base a una actividad de bus.

17. El procedimiento de la reivindicación 10, en el que si tan sólo queda pendiente una solicitud de bus, la frecuencia de árbitro es igual a la frecuencia de bus.

Patentes similares o relacionadas:

CONCENTRADOR DE BUS SERIE UNIVERSAL QUE PUEDE ROTAR, del 15 de Septiembre de 2011, de BELKIN INTERNATIONAL, INC: - Un sistema concentrador de conectores , que comprende: un primer cuerpo que comprende una pluralidad de conectores (208a - 208d) accesible desde una superficie […]

PROCEDIMIENTO DE CONTROL DE FLUJO PARA MEJORAR LA TRANSFERENCIA DE DATOS A TRAVÉS DE UNA MATRIZ DE CONMUTACIÓN, del 22 de Marzo de 2011, de QUALCOMM INCORPORATED: Un circuito integrado (IC) de sistema-en-chip (SoC), que comprende: un controlador de bus; una pluralidad de esclavos (16A, 16B, 16C, ..., 16N) interconectados con […]

CONMUTADOR DE DIRECCIÓN NO BLOQUEANTE CON COLAS SUPERFICIALES POR AGENTE, del 17 de Marzo de 2011, de APPLE INC.: Un sistema que comprende: una pluralidad de agentes (12A-12D); una interconexión ; y un conmutador acoplado a la pluralidad de agentes y a la interconexión, […]

DISPOSITIVO Y MÉTODO ASOCIADO PARA GESTIONAR AUTOMÁTICAMENTE LOS FLUJOS DE DATOS DIGITALES DE UN HUÉSPED ENTRE LA INTERFAZ COMÚN Y LOS MÓDULOS ASOCIADOS, del 4 de Enero de 2011, de SMARDTV S.A.: Dispositivo para gestionar automáticamente el flujo de datos digitales de un huésped constituido por un descodificador para la recepción de televisión digital […]

DISPOSITIVO Y MÉTODO ASOCIADO PARA GESTIONAR AUTOMÁTICAMENTE LOS FLUJOS DE DATOS DIGITALES DE UN HUÉSPED ENTRE LA INTERFAZ COMÚN Y LOS MÓDULOS ASOCIADOS, del 4 de Enero de 2011, de SMARDTV S.A.: Dispositivo para gestionar automáticamente el flujo de datos digitales de un huésped constituido por un descodificador para la recepción de televisión digital […]

Método y aparato para detectar contrapresión de mensajes, del 8 de Abril de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de detección de contrapresión de paquetes, en donde el método se aplica a un dispositivo que tiene un puerto de Interconexión de […]

Sistema de procesamiento de datos y método de procesamiento de datos, del 1 de Enero de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un sistema de procesamiento de datos , que comprende una unidad central de procesamiento, CPU , una memoria , un controlador […]

Dispositivo de inserción de terminal, del 27 de Noviembre de 2019, de Ingenico Group: Dispositivo de conexión de un terminal de comunicación, dispositivo que comprende:

- una superficie plana ;

- un conector macho destinado a conectarse a […]

Dispositivo de inserción de terminal, del 27 de Noviembre de 2019, de Ingenico Group: Dispositivo de conexión de un terminal de comunicación, dispositivo que comprende:

- una superficie plana ;

- un conector macho destinado a conectarse a […]

Dispositivo de conmutación, sistema de interconexión de componentes periféricos rápida y procedimiento de inicialización del mismo, del 13 de Noviembre de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un dispositivo de conmutación que comprende: múltiples puertos de Interconexión de Componentes Periféricos rápidos, PCIe, aguas arriba , […]