"APARATO DIVISOR DE FRECUENCIA PROGRAMABLE".

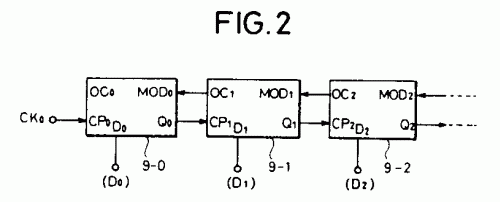

APARATO DIVISOR DE FRECUENCIA PROGRAMABLE CON UNA RED DIVISORA DE FRECUENCIA CON VARIAS ETAPAS DIVISORAS DE FRECUENCIAS PROGRAMABLES CONECTADAS EN CASCADA QUE DIVIDEN POR DOS Y TRES LA FRECUENCIA DE UN IMPULSO DE RELOJ BASADA EN UN NIVEL LOGICO DE UNA SEÑAL DE ENTRADA PREFIJADA USADA PARA CAMBIAR UNA RELACION VARIABLE DE DIVISION,

Y MEDIOS DE PUERTA LOGICA PARA DETERMINAR SI CADA SALIDA DE ETAPA SE LLEVA O NO A CONFIGURACION PREDETERMINADA, Y SE INTRODUCE UNA SEÑAL DE INSTRUCCION PARA TOMAR UNA DECISION RESPECTO AL INCREMENTO EN (+1) DE LA RELACION DE DIVISION, PARA GENERAR LA SALIDA DE UN NIVEL LOGICO, HACIENDO QUE. UNA ETAPA EQUIVALENTE A UNA PRIMERA ETAPA, DIVIDA POR TRES LA FRECUENCIA DEL IMPULSO DE RELOJ SI SE DETERMINA QUE ES POSITIVO EN LA DETECCION ANTE RIOR, Y LA SALIDA DE LOS MEDIOS SE SUMINISTRA A LA ETAPACORRESPONDIENTE A LA PRIMERA PARA SELECCIONAR UNA RELACION DE DIVISION DE N Y (N+1).

Tipo: Resumen de patente/invención.

Solicitante: NIHON MUSEN KABUSHIKI KAISHA.

Nacionalidad solicitante: Japón.

Dirección: 1-1, SHIMORENJYAKU 5-CHOME MITAKA-SHI, TOKYO 181.

Inventor/es: YAMASHITA, KAZUO, ADACHI, NOBUYUKI, INOUE, AKIHARU.

Fecha de Solicitud: 2 de Septiembre de 1991.

Fecha de Publicación: .

Fecha de Concesión: 11 de Mayo de 1994.

Clasificación Internacional de Patentes:

- H03K23/48 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 23/00 Contadores de impulsos que comprenden cadenas de cómputo; Divisores de frecuencia que comprenden cadenas de cómputo (H03K 29/00 tiene prioridad). › con una base o raíz diferente de una potencia de dos (H03K 23/42 tiene prioridad).

- H03K23/50 H03K 23/00 […] › utilizando circuitos desconectadores biestables a reacción (H03K 23/42 - H03K 23/48 tienen prioridad).

- H03L7/197 H03 […] › H03L CONTROL AUTOMATICO, ARRANQUE, SINCRONIZACION O ESTABILIZACION DE GENERADORES DE OSCILACIONES O DE IMPULSOS ELECTRONICOS (de generadores dinamoeléctricos H02P). › H03L 7/00 Control automático de frecuencia o fase; Sincronización (sintonización de circuitos resonantes en general H03J; sincronización en los sistemas de comunicación digital, ver los grupos apropiados en la clase H04). › siendo utilizada una diferencia de tiempos para enclavar el bucle, y contando el contador entre dos números variables en el tiempo o dividiendo el divisor de frecuencia por un factor variable en el tiempo, p. ej. para obtener una división de frecuencia fraccionaria.

Patentes similares o relacionadas:

Convertidor de fase a digital en bucle de bloqueo de fase totalmente digital, del 3 de Junio de 2020, de QUALCOMM INCORPORATED: Un procedimiento de conversión de fase a digital, comprendiendo el procedimiento: recibir por medio de un multiplexor de selección de ruta […]

Sintetizador, del 13 de Marzo de 2019, de MITSUBISHI ELECTRIC CORPORATION: Sintetizador que comprende un sintetizador de ajuste aproximado y un sintetizador de ajuste preciso, en el que el sintetizador de ajuste aproximado […]

SINTETIZADOR DE FRECUENCIA DE BAJO RUIDO QUE UTILIZA DIVISORES DE NUMEROS SEMI-ENTEROS Y COMPENSACION DE GANANCIA ANALOGICA., del 1 de Abril de 2005, de RAYTHEON COMPANY: UN SINTETIZADOR 10 DE FRECUENCIAS DE BAJO RUIDO, QUE USA DIVISORES 13, 15 DE FRECUENCIAS, POR LO MENOS UNO DE LOS CUALES (DIVISOR 15) PUEDE INCREMENTARSE […]

METODO Y SISTEMA PARA REDUCIR LAS FLUCTUACIONES DE UNA ESTRUCTURA DE PLL (BUCLE DE ENGANCHE DE FASE) CARACTERIZADA POR UNA RAZON RACIONAL ENTRE LAS FRECUENCIAS DE ENTRADA Y SALIDA., del 1 de Abril de 1998, de ALCATEL ALSTHOM COMPAGNIE GENERALE D'ELECTRICITE: SE PRESENTA UN METODO DE CONTROL DE PLL EN QUE LA RAZON ENTRE LA FRECUENCIA DE SALIDA Y LA DE ENTRADA ES UN NUMERO RACIONAL. SE CARACTERIZA POR LA PRESENCIA […]

SINTESIS FRACCIONAL-N DE ACUMULADORES ENGANCHADOS CON REDUCCION DE ERROR RESIDUAL., del 16 de Febrero de 1997, de MOTOROLA, INC.: SINTESIS FRACCIONAL-N DE ACUMULADORES ENGANCHADOS CON REDUCCION DE ERROR RESIDUAL PARA SER UTILIZADO EN TRANSCEPTORES DE RADIO DIGITALES. SE DESCRIBE […]

SINTESIS FRACCIONAL-N DE ACUMULADORES MULTIPLES ENGANCHADOS., del 16 de Febrero de 1997, de MOTOROLA, INC.: SINTESIS FRACCIONAL-N DE ACUMULADORES MULTIPLES ENGANCHADOS PARA SER UTILIZADO EN TRANSCEPTORES DE RADIO DIGITALES. SE DESCRIBE UN SINTETIZADOR […]

METODO Y APARATO PARA REDUCIR LA CORRIENTE EN MODO DE ESPERA EN EQUIPOS DE COMUNICACIONES, del 16 de Septiembre de 2007, de TELEFONAKTIEBOLAGET L M ERICSSON (PUBL): ESTA INVENCION SE REFIERE A UN PROCEDIMIENTO Y A UN APARATO QUE SIRVEN PARA REDUCIR EL CONSUMO DE ENERGIA DE UN DISPOSITIVO DE COMUNICACIONES. EN MODO DE VIGILIA, […]

METODO Y APARATO PARA REDUCIR LA CORRIENTE EN MODO DE ESPERA EN EQUIPOS DE COMUNICACIONES, del 16 de Septiembre de 2007, de TELEFONAKTIEBOLAGET L M ERICSSON (PUBL): ESTA INVENCION SE REFIERE A UN PROCEDIMIENTO Y A UN APARATO QUE SIRVEN PARA REDUCIR EL CONSUMO DE ENERGIA DE UN DISPOSITIVO DE COMUNICACIONES. EN MODO DE VIGILIA, […]

DETECCION DE FASE DIGITAL, LINEAL, SIN BANDA MUERTA, del 1 de Julio de 2007, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un bucle de bloqueo de fase fraccionario en N que comprende: un detector de fase que comprende: una primera entrada dispuesta para […]

DETECCION DE FASE DIGITAL, LINEAL, SIN BANDA MUERTA, del 1 de Julio de 2007, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un bucle de bloqueo de fase fraccionario en N que comprende: un detector de fase que comprende: una primera entrada dispuesta para […]