PROCESADOR CON GENERADOR DE DIRECCIONES.

Procesador (1a, 1b) para procesar datos, que comprende: un generador (2,

100) de direcciones, que es operativo para generar una secuencia de direcciones (8) que tienen valores no fraccionarios cuantificados y que se basan en una dirección de base y un valor de desplazamiento fraccionario, caracterizado porque el generador de direcciones: es operativo además para actualizar dicho valor de desplazamiento fraccionario en un paso fraccionario (Δ) desde la generación de una dirección a una dirección subsiguiente en dicha secuencia de direcciones, es operativo además para almacenar temporalmente el valor de desplazamiento fraccionario actualizado para la generación de la dirección subsiguiente, y comprende un cuantificador (102) operativo para generar la dirección (8) basándose en una suma de la dirección de base y el valor de desplazamiento fraccionario

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2007/052820.

Solicitante: TELEFONAKTIEBOLAGET LM ERICSSON (PUBL).

Nacionalidad solicitante: Suecia.

Dirección: PATENT UNIT 164 83 STOCKHOLM SUECIA.

Inventor/es: PERSSON, PER, GUSTAFSSON,Harald.

Fecha de Publicación: .

Fecha Solicitud PCT: 23 de Marzo de 2007.

Clasificación Internacional de Patentes:

- G06F9/30Z

- G06F9/345 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › de operandos o de resultados múltiples.

- G06F9/355A2

- G06F9/38S6

Clasificación PCT:

- G06F9/345 G06F 9/00 […] › de operandos o de resultados múltiples.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Fragmento de la descripción:

Campo técnico

La presente invención se refiere a un procesador, que comprende un generador de direcciones para generar una dirección basándose en una dirección de base y un paso fraccionario.

Antecedentes 5

Un procesador se puede usar para procesar datos. Los datos se pueden almacenar, por ejemplo, en una memoria, que es accesible por el procesador. Para acceder a los datos de la memoria, el procesador necesita una dirección, en la que están almacenados los datos. Las direcciones que son necesarias para adquirir datos para una cierta aplicación se pueden generar y almacenar temporalmente en un registro de direcciones. El registro de direcciones se puede actualizar continuamente con 10 direcciones nuevas durante el progreso de la aplicación.

En muchas aplicaciones, un paso para actualizar la dirección del registro de direcciones no es el mismo cada vez que se realiza una operación de actualización. El paso puede ser o bien un incremento o bien un decremento. Aplicaciones diferentes pueden usar estrategias diferentes para los pasos. Además, un paso incluso puede ser fraccionario, por ejemplo, un valor no entero, aun cuando las direcciones de la 15 memoria estén situadas siempre en posiciones enteras. Por ejemplo, si se necesita un paso de 0,75, se puede generar la siguiente secuencia de direcciones cuando el valor de una dirección de inicio es 0: [0],75, [1],5, [2],25, [3],0, [3],75, [4],5,..., en donde la parte entera de la secuencia de direcciones indicada entre corchetes se usará para el acceso a memoria. En este caso, puede observarse que la dirección que presenta el valor 3 se usará dos veces. Algunas aplicaciones en las que se usa la actualización 20 fraccionaria son la interpolación, el escalado, el remuestreo, la sincronización, y la consulta en tablas.

La actualización de una dirección para el registro de direcciones con una cantidad fraccionaria se realiza normalmente mediante instrucciones de software, o una secuencia de instrucciones de software, ejecutadas por el procesador. Además, en la técnica se sabe que unidades de hardware, que son externas para un procesador, realizan una interpolación basándose en pasos fraccionarios. La 25 interpolación se realiza por tanto fuera del propio procesador. Las direcciones generadas como parte de un método de interpolación no son accesibles mediante las instrucciones de software. La realización de solamente un método de interpolación predeterminado por las unidades de hardware tiene la consecuencia de que los datos interpolados resultantes son accesibles para otras unidades pero no la dirección usada para la interpolación. Por lo tanto, la dirección se puede usar solamente con una finalidad 30 predeterminada, tal como el método de interpolación predeterminado. Esto hace que las unidades de hardware resulten rígidas.

En el documento US 2004/0003199 A1 se da a conocer un dispositivo de interfaz de memoria que proporciona una interfaz de direcciones fraccionarias entre un procesador de datos y un sistema de memoria. La interfaz de memoria proporciona la interpolación de valores de datos. La interfaz de memoria 35 incluye un generador de direcciones para generar una primera y una segunda direcciones de memoria, y una unidad de acceso a memoria para recuperar un primer y un segundo valores de datos y para la interpolación entre el primer y el segundo valores de los datos. El generador de direcciones comprende un registro que contiene una dirección fraccionaria de los datos a recuperar del sistema de memoria, y un registro que contiene un desplazamiento fraccionario a aplicar a la dirección entre búsquedas en la 40 memoria. Después de cada búsqueda en la memoria, el desplazamiento se suma a la dirección usando un sumador, y la dirección resultante se sitúa en el registro de direcciones, preparada para la siguiente búsqueda. En una realización, el generador de direcciones incluye también un registro de módulo y un registro de direcciones de base. Los mismos permiten que el sumador realice una aritmética modular, facilitando de este modo un direccionamiento circular. 45

Un problema con la actualización de una dirección para el registro de direcciones mediante software ejecutado por el procesador es que la actualización de la dirección se realiza frecuentemente en partes del núcleo kernel, tales como bucles internos, del software. Normalmente, los bucles internos están frecuentemente en ejecución. Por lo tanto, cualquier instrucción ejecutada adicional para actualizar el registro de direcciones en una parte del núcleo kernel tiene un impacto negativo directo sobre el 50 rendimiento del sistema. Este problema resulta particularmente importante para una actualización con un paso fraccionario de una dirección para el registro de direcciones, ya que todas las arquitecturas de procesadores disponibles requieren la ejecución de unas cuantas instrucciones de software adicionales para actualizar la dirección mediante un paso fraccionario.

En aplicaciones que usan un paso fraccionario para actualizar una dirección, el cuello de botella 55 de una parte de núcleo del procesador lo constituye frecuentemente la introducción y la extracción de datos de un repositorio de datos. Un problema con la introducción y la extracción de datos es la

actualización eficaz de una dirección. Como ejemplo, un oscilador de ondas de sintetizador, que es básicamente un interpolador, necesita pasos fraccionarios para actualizar una dirección para todas las muestras de entrada así como todos los coeficientes de una tabla. Consecuentemente, incluso una pequeña mejora del rendimiento en la actualización con un paso fraccionario de direcciones puede proporcionar una mejora sustancial del rendimiento del sistema en el que se utiliza la generación de 5 direcciones.

Sumario

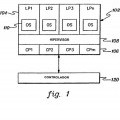

Según una realización de la invención, un procesador para procesar datos comprende un generador de direcciones. El generador de direcciones es operativo para generar una dirección basándose en una dirección de base y un valor de desplazamiento, y para actualizar dicho valor de 10 desplazamiento mediante un paso fraccionario. El procesador puede ser un procesador principal, que comprende el generador de direcciones en una parte del núcleo del mismo. Alternativamente, el procesador puede comprender un procesador principal y por lo menos un co-procesador conectado operativamente al procesador principal. El co-procesador comprende el generador de direcciones.

El generador de direcciones es operativo para generar la dirección basándose en la dirección de 15 base y un valor de desplazamiento. Dicho valor de desplazamiento se actualiza mediante el paso fraccionario.

El generador de direcciones es operativo para generar la dirección basándose en una dirección de base, que es una dirección de base fraccionaria.

El generador de direcciones puede comprender un cuantificador operativo para generar la 20 dirección basándose en la suma de la dirección de base más el valor de desplazamiento.

El generador de direcciones puede ser operativo para generar la dirección basándose en una dirección de base, que es una dirección de base entera.

El generador de direcciones puede comprender un cuantificador operativo para generar un valor de desplazamiento entero basándose en el valor de desplazamiento, el cual se basa en el paso 25 fraccionario. El generador de direcciones puede ser operativo para generar la dirección basándose en el valor de desplazamiento entero.

El generador de direcciones puede comprender un sumador operativo para generar la suma de la dirección de base más el valor de desplazamiento.

El generador de direcciones puede comprender un sumador operativo para generar y dar salida a 30 la suma de un valor de desplazamiento, que es uno de entre el valor de desplazamiento que está basado en el paso fraccionario y un valor de desplazamiento de entrada, más el paso fraccionario. Adicionalmente, el generador de direcciones puede comprender un contador de módulo, operativo para generar un valor de desplazamiento subsiguiente, para ser usado con el fin de generar una dirección subsiguiente, basándose en la salida del sumador y un valor de desplazamiento máximo. 35

El generador de direcciones puede comprender un multiplexor operativo para dar salida al valor de desplazamiento. El valor de desplazamiento puede ser uno de entre el valor de desplazamiento de entrada y un valor de desplazamiento generado por el contador de módulo.

El generador de direcciones puede ser operativo...

Reivindicaciones:

1. Procesador (1a, 1b) para procesar datos, que comprende:

un generador (2, 100) de direcciones, que es operativo para generar una secuencia de direcciones (8) que tienen valores no fraccionarios cuantificados y que se basan en una dirección de base y un valor de desplazamiento fraccionario, 5

caracterizado porque el generador de direcciones:

es operativo además para actualizar dicho valor de desplazamiento fraccionario en un paso fraccionario (Δ) desde la generación de una dirección a una dirección subsiguiente en dicha secuencia de direcciones,

es operativo además para almacenar temporalmente el valor de desplazamiento fraccionario 10 actualizado para la generación de la dirección subsiguiente, y

comprende un cuantificador (102) operativo para generar la dirección (8) basándose en una suma de la dirección de base y el valor de desplazamiento fraccionario.

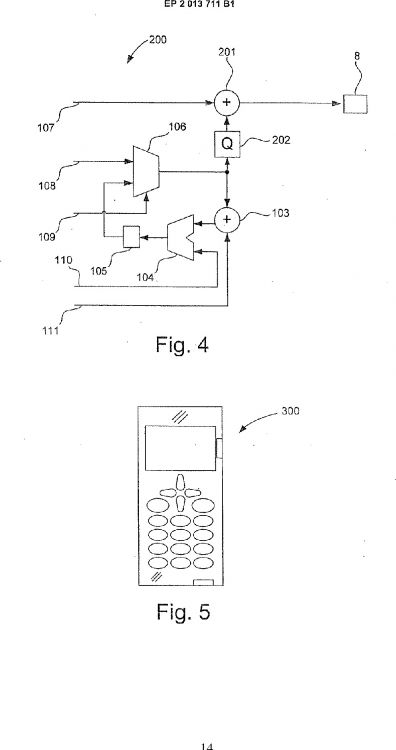

2. Procesador (1a, 1b) para procesar datos, que comprende:

un generador (2, 200) de direcciones, que es operativo para generar una secuencia de direcciones 15 (8) que tienen valores no fraccionarios cuantificados y que se basan en una dirección de base y un valor de desplazamiento fraccionario,

caracterizado porque el generador de direcciones:

es operativo además para actualizar dicho valor de desplazamiento fraccionario en un paso fraccionario (Δ) desde la generación de una dirección a una dirección subsiguiente en dicha 20 secuencia de direcciones,

es operativo además para almacenar temporalmente el valor de desplazamiento fraccionario actualizado para la generación de la dirección subsiguiente,

es operativo además para generar la dirección (8) basándose en una suma de la dirección de base y un valor de desplazamiento entero, y 25

comprende un cuantificador (202) operativo para generar el valor de desplazamiento entero basándose en el valor de desplazamiento fraccionario.

3. Procesador según la reivindicación 1 ó 2, en el que el procesador (1a) es un procesador principal, que comprende el generador (2, 100, 200) de direcciones en una parte (3) de núcleo del mismo.

4. Procesador según la reivindicación 1 ó 2, que comprende un procesador principal (5) y por lo 30 menos un co-procesador (6) conectado operativamente al procesador principal, en donde el co-procesador comprende el generador (2, 100, 200) de direcciones.

5. Procesador según la reivindicación 1, en el que la dirección de base es una dirección de base fraccionaria.

6. Procesador según las reivindicaciones 1 ó 5, en el que la dirección de base se incrementa en 35 0,5.

7. Procesador según la reivindicación 1 ó 2, en el que la dirección de base es una dirección de base entera.

8. Procesador según cualquiera de las reivindicaciones 1 a 7, en el que el generador (2, 100, 200) de direcciones comprende un sumador (103) operativo para generar y dar salida a la suma de un 40 valor de desplazamiento, el cual es uno de entre el valor de desplazamiento fraccionario que se basa en el paso fraccionario y un valor de desplazamiento de entrada, más el paso fraccionario, y un contador (104) de módulo operativo para generar un valor de desplazamiento subsiguiente, para ser usado con el fin de generar una dirección subsiguiente, sobre la base de la salida del sumador (103) y un valor de desplazamiento máximo (N). 45

9. Procesador según la reivindicación 8, en el que el generador (2, 100, 200) de direcciones comprende un multiplexor (106) operativo para dar salida al valor de desplazamiento, el cual es uno de entre el valor de desplazamiento de entrada y un valor de desplazamiento generado por el contador (104)

de módulo.

10. Procesador según cualquiera de las reivindicaciones anteriores, en el que el generador (2, 100, 200) de direcciones es operativo en respuesta a por lo menos una instrucción de software.

11. Procesador según cualquiera de las reivindicaciones anteriores, en el que un número de bits necesarios para representar el valor de desplazamiento fraccionario es menor que un número de bits 5 necesarios para representar la dirección de base.

12. Aparato electrónico, que comprende el procesador según cualquiera de las reivindicaciones 1 a 11.

13. Aparato electrónico según la reivindicación 12, en el que el aparato electrónico es un teléfono móvil. 10

Patentes similares o relacionadas:

Procedimientos y aparatos para cancelar solicitudes de captura previa de datos para un bucle, del 25 de Octubre de 2017, de QUALCOMM INCORPORATED: Un procedimiento para cancelar solicitudes de captura previa de memoria caché de datos no de demanda, en un sistema procesador que comprende un procesador […]

COMPOSICION FARMACEUTICA ESTABLE QUE COMPRENDE ERITROPOYETINA., del 16 de Marzo de 2007, de LEK PHARMACEUTICALS D.D.: Una composición farmacéutica estable de eritropoyetina (EPO), que consiste en: a. una cantidad terapéuticamente efectiva de EPO b. un sistema regulador […]

MECANISMO DE EXTRACCIÓN DE ATRIBUTOS DE CACHÉ E INSTRUCCIÓN PARA EL MISMO, del 21 de Noviembre de 2011, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método de funcionamiento de un ordenador que comprende: la extracción , por un procesador de un sistema de procesamiento, de una […]

DESCUBRIMIENTO DE TOPOLOGÍA VIRTUAL PARA CONFIGURACIÓN DE ORDENADOR, del 21 de Noviembre de 2011, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Para un sistema de ordenador anfitrión dividido en particiones lógicamente que comprende procesadores anfitriones, un método para descubrir […]

INVALIDACIÓN DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 27 de Mayo de 2011, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para borrar elementos de memorias intermedias de traducción de direcciones en un sistema informático , comprendiendo el sistema […]

INVALIDACIÓN DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 27 de Mayo de 2011, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para borrar elementos de memorias intermedias de traducción de direcciones en un sistema informático , comprendiendo el sistema […]

INVALIDACIÓN DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 29 de Abril de 2011, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar una gama de dos o más elementos de una tabla de traducción de direcciones en un sistema informático que tiene tablas de […]

INVALIDACIÓN DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 29 de Abril de 2011, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar una gama de dos o más elementos de una tabla de traducción de direcciones en un sistema informático que tiene tablas de […]

INVALIDACION DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 19 de Abril de 2010, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar los elementos de tablas de traducción y borrar los correspondientes elementos de tablas de traducción dinámica de direcciones (DAT) […]

INVALIDACION DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 19 de Abril de 2010, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar los elementos de tablas de traducción y borrar los correspondientes elementos de tablas de traducción dinámica de direcciones (DAT) […]