INVALIDACIÓN DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA.

Un método para invalidar una gama de dos o más elementos de una tabla de traducción de direcciones en un sistema informático que tiene tablas de traducción de direcciones para traducir dinámicamente direcciones virtuales a direcciones de almacenamiento principal,

el método comprende los pasos de: determinar una instrucción ejecutable para máquina desde un código de operación para ser ejecutada, que la instrucción esté configurada para iniciar la ejecución de una operación de invalidación y borrado; y ejecutar la instrucción, comprendiendo el paso de ejecución los pasos de: determinar, desde la información proporcionada por la instrucción, una primera dirección de elemento de tabla de traducción de un primer elemento de una tabla de traducción, de la gama de dos o más elementos de una tabla de traducción de direcciones para ser invalidadas;determinar, desde la información de gama proporcionada por la instrucción, un número de elementos de una tabla de traducción de direcciones para ser invalidadas; y basándose en la primera dirección del elemento de tabla de traducción determinada, invalidar la gama de dos o más elementos de una tabla de traducción de direcciones indicadas por la información de la gama

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E05108510.

Solicitante: INTERNATIONAL BUSINESS MACHINES CORPORATION.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: NEW ORCHARD ROAD ARMONK, NY 10504 ESTADOS UNIDOS DE AMERICA.

Inventor/es: HELLER,LISA, PFEFFER,ERWIN, PLAMBECK,KENNETH, SLEGEL,TIMOTHY.

Fecha de Publicación: .

Fecha Solicitud PCT: 6 de Mayo de 2004.

Clasificación Internacional de Patentes:

- G06F12/10L

- G06F12/10L2

- G06F12/10S

- G06F9/30Z

- G06F9/38D

Clasificación PCT:

- G06F12/10 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 12/00 Acceso, direccionamiento o asignación en sistemas o arquitecturas de memoria (entrada digital a partir de, o salida digital hacia soportes de registro, p. ej. hacia unidades de almacenamiento de disco G06F 3/06). › Traducción de direcciones.

- G06F9/312 G06F […] › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Control de operaciones de carga, de registro o de borrado.

Clasificación antigua:

- G06F9/312 G06F 9/00 […] › Control de operaciones de carga, de registro o de borrado.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

PDF original: ES-2357802_T3.pdf

Fragmento de la descripción:

Esta invención está relacionada, en general, con el proceso dentro de un entorno informático y, en particular, con uno o más de invalidación de almacenamiento, borrado de elementos de la memoria intermedia y una instrucción para ellos.

Los entornos informáticos existentes utilizan el almacenamiento virtual que es mantenido normalmente en almacenamiento auxiliar para aumentar el tamaño del almacenamiento disponible. Cuando se hace referencia a una 5 página de almacenamiento virtual, la dirección virtual utilizada cuando se hace referencia a esta página es traducida, por medio de una traducción dinámica de direcciones, en una dirección real de almacenamiento. Si la traducción ha tenido éxito, el almacenamiento virtual es válido; en otro caso, es inválido. Una página de almacenamiento virtual está indicada como válida o inválida por medio de un bit de invalidación en un elemento de la tabla de páginas, incluyendo este elemento una dirección real de almacenamiento si la página es válida. 10

Las páginas de almacenamiento pueden ser invalidadas de una en una, tal como se describe en el documento US 6119204. Por ejemplo, en un entorno informático basado en la arquitectura/z, ofrecida por International Business Machines Corporation, se utiliza una instrucción, denominada como Instrucción de Elemento de Invalidación de La Tabla de Páginas (IPTE), para invalidar una página de almacenamiento. La invalidación incluye la colocación de un indicador de invalidación en una estructura de control, asociado con el almacenamiento virtual y situado en el almacenamiento 15 físico principal. En el almacenamiento físico principal, para indicar que no puede traducirse una dirección virtual de un lugar del almacenamiento virtual, por medio de una traducción dinámica de direcciones, en una dirección de almacenamiento físico principal, denominada también dirección real. Además, se utiliza la instrucción para borrar los elementos de la memoria intermedia interna a la máquina, asociados con la página, pudiendo utilizarse esos elementos durante la traducción dinámica de direcciones para evitar el acceso a estructuras de control en el almacenamiento físico 20 principal. Por ejemplo, en la arquitectura/z, existen Memorias Intermedias de Traducción Adelantada, que se utilizan durante la traducción dinámica de direcciones de las direcciones virtuales a direcciones reales. Cuando se invalida una página de almacenamiento, se borran también las correspondientes memorias intermedias de elementos asociados con esa página.

También hay instrucciones que permiten la purga de todas las Memorias Intermedias de Traducción Adelantada. Por 25 ejemplo, en la arquitectura/z, una instrucción, denominada instrucción de Comparar e Intercambiar y Purgar (CSP), purga todos los elementos de las Memorias Intermedias de Traducción Adelantada.

Así, aunque hay instrucciones para invalidar una página de almacenamiento y limpiar las memorias intermedias de elementos asociados con esa página, e instrucciones para limpiar todas las memorias intermedias, sigue existiendo la necesidad de instrucciones que puedan invalidar selectivamente diversos tamaños de unidades de almacenamiento y/o 30 limpiar las memorias intermedias de elementos asociados con ellas. Por ejemplo, existe la necesidad de una instrucción que permita la especificación de una unidad seleccionada de almacenamiento mayor que una página para que sea invalidada y/o borre los elementos de la memoria intermedia asociados con ella. Existe una necesidad adicional de una instrucción que permita borrar los elementos de la memoria intermedia para unidades de almacenamiento seleccionadas, sin afectar elementos de memoria intermedia de otras unidades de almacenamiento. 35

La presente invención proporciona un método para invalidar el almacenamiento de un entorno informático, como se reivindica en la reivindicación 1.

Preferiblemente, la presente invención proporciona un método para invalidar el almacenamiento de un entorno informático. El método incluye, por ejemplo, especificar una unidad de almacenamiento a invalidar, incluyendo la unidad de almacenamiento una pluralidad de páginas de almacenamiento, y donde la especificación incluye proporcionar un 40 descriptor de la unidad de almacenamiento; e invalidar la unidad de almacenamiento.

Preferiblemente, la presente invención proporciona un método para facilitar el borrado de las memorias intermedias de un entorno informático. El método incluye, por ejemplo, identificar una unidad de almacenamiento para la cual se ha de efectuar el borrado de uno o más elementos de una o más memorias intermedias, donde la unidad de almacenamiento incluye una pluralidad de páginas de almacenamiento; y borrar uno o más elementos de una o más memorias 45 intermedias asociadas con la unidad de almacenamiento identificada, donde uno o más elementos asociados con otra unidad de almacenamiento no son borrados.

Preferiblemente, se proporciona una instrucción que ha de ejecutarse dentro de un entorno informático. La instrucción incluye, por ejemplo, un código de operación para identificar una instrucción a ejecutar; una designación de invalidación para especificar la información asociada con una unidad de almacenamiento a invalidar, incluyendo la unidad de 50 almacenamiento una pluralidad de páginas de almacenamiento; otra designación para especificar información adicional para utilizar por la instrucción; y una designación de borrado para especificar información asociada con una de las unidades de almacenamiento y otra unidad de almacenamiento para la cual han de borrarse uno o más elementos de una o más memorias intermedias, donde uno o más componentes de una o más de las designaciones de invalidación, de la otra designación y de la designación de borrado, son configurables como no-operaciones. 55

Preferiblemente, se proporciona una instrucción a ejecutar dentro de un entorno informático. La instrucción incluye, por ejemplo, un código de operación para identificar una instrucción a ejecutar; y al menos una de las siguientes:

una primera designación de invalidación para especificar la información asociada con una unidad de almacenamiento a invalidar, incluyendo la unidad de almacenamiento una pluralidad de páginas de almacenamiento; una segunda designación de invalidación para especificar información adicional asociada con la unidad de almacenamiento a invalidar; y una designación de borrado para especificar información asociada con una de las unidades de almacenamiento y otra unidad de almacenamiento para la cual han de borrarse uno 5 o más elementos de una o más memorias intermedias, donde la información especificada por la designación de borrado no está asociada con al menos otra unidad de almacenamiento, para la cual no han de borrarse uno o más elementos.

En esta memoria se describen y reivindican también productos de sistemas y programas de ordenador correspondientes a los métodos resumidos anteriormente. 10

Se realizan características y ventajas adicionales por medio de las técnicas de la presente invención. Otros modos de realización y aspectos de la invención se describen también en detalle en esta memoria y se consideran parte de la invención reivindicada.

La materia objeto que se considera como la invención, está particularmente indicada y reivindicada separadamente en las reivindicaciones del final de la memoria. Los anteriores y otros objetos, características y ventajas de la invención son 15 evidentes a partir de la siguiente descripción detallada, tomada conjuntamente con los dibujos que se acompañan, en los cuales:

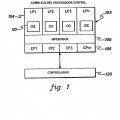

La figura 1 representa un modo de realización de un entorno informático que incorpora y utiliza uno o más aspectos de la presente invención;

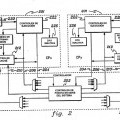

La figura 2 representa un modo de realización de detalles adicionales asociados con un controlador de la figura 20 1, de acuerdo con un aspecto de la presente invención;

La figura 3 representa un modo de realización de un ordenador central que puede emular a otro ordenador, de acuerdo con un aspecto de la presente invención;

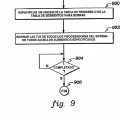

La figura 4 representa un modo de realización de la lógica asociada con el almacenamiento de invalidación, de acuerdo con un aspecto de la presente invención; 25

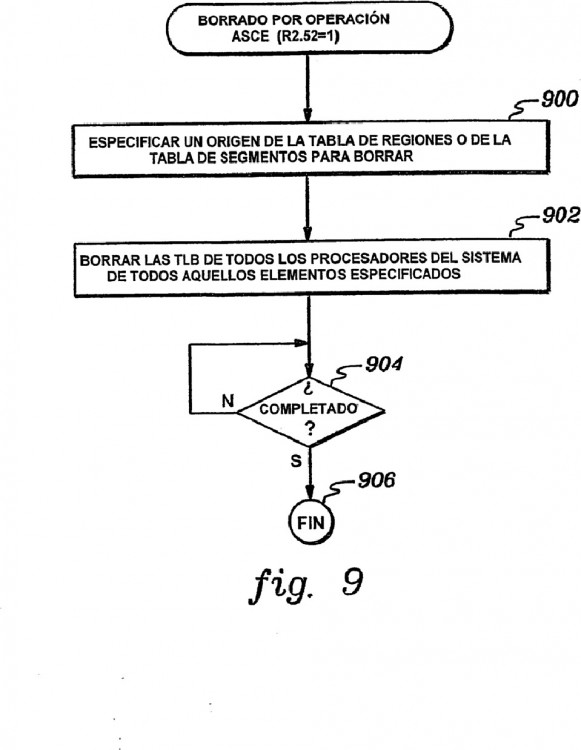

La figura 5 representa un modo de realización de la lógica asociada con el borrado de elementos de la memoria intermedia, de acuerdo con un aspecto de la presente invención;

La figura 6a representa un modo de realización... [Seguir leyendo]

Reivindicaciones:

1. Un método para invalidar una gama de dos o más elementos de una tabla de traducción de direcciones en un sistema informático que tiene tablas de traducción de direcciones para traducir dinámicamente direcciones virtuales a direcciones de almacenamiento principal, el método comprende los pasos de:

determinar una instrucción ejecutable para máquina desde un código de operación para ser ejecutada, que la 5 instrucción esté configurada para iniciar la ejecución de una operación de invalidación y borrado; y

ejecutar la instrucción, comprendiendo el paso de ejecución los pasos de:

determinar, desde la información proporcionada por la instrucción, una primera dirección de elemento de tabla de traducción de un primer elemento de una tabla de traducción, de la gama de dos o más elementos de una tabla de traducción de direcciones para ser invalidadas; 10

determinar, desde la información de gama proporcionada por la instrucción, un número de elementos de una tabla de traducción de direcciones para ser invalidadas; y

basándose en la primera dirección del elemento de tabla de traducción determinada, invalidar la gama de dos o más elementos de una tabla de traducción de direcciones indicadas por la información de la gama.

2. El método de acuerdo con la reivindicación 1, en el que la gama de dos o más elementos de una tabla de traducción 15 de direcciones para ser invalidadas comprende cada una un bit inválido para la invalidación, en el que cuando el bit inválido es 0, se permite el uso o utilización del elemento de la tabla de traducción de direcciones para la traducción dinámica, en el que cuando el bit inválido es1, no se permite el uso o utilización del elemento de la tabla de traducción de direcciones para la traducción dinámica.

3. El método de acuerdo con la reivindicación 1, en el que la gama de dos o más elementos de la tabla de traducción 20 consta de uno cualquiera de entre los elementos de la tabla de segmentos o de los elementos de la tabla de regiones.

4. El método de acuerdo con la reivindicación 1, en el que el sistema informático comprende procesadores centrales (CPU), registradores con fines generales de arquitectura, memorias intermedias de traducción de direcciones, las memorias intermedias de traducción de direcciones teniendo elementos de memorias intermedias de traducción de direcciones que mantienen información de traducción de direcciones, las tablas de traducción de dirección constando 25 de una cualquiera de entre:

una o más tablas de segmentos que contienen elementos que apuntan a las tablas de páginas.,

una o más primeras tablas de regiones que contienen elementos que apuntan a segundas tablas de regiones, conteniendo las segundas tablas de regiones elementos que apuntan a terceras tablas de regiones, conteniendo las terceras tablas de regiones elementos que apuntan a las tablas de segmentos, conteniendo las tablas de 30 segmentos elementos que apuntan a las tablas de páginas,

una o más segundas tablas de regiones que contienen elementos que apuntan a terceras tablas de regiones, conteniendo las terceras tablas de regiones elementos que apuntan a las tablas de segmentos, conteniendo las tablas de segmentos elementos que apuntan a las tablas de páginas,

una o más terceras tablas de regiones que contienen elementos que apuntan a tablas de segmentos, 35 conteniendo las tablas de segmentos elementos que apuntan a las tablas de páginas; y la determinación desde el paso del código de operación que comprende los pasos adicionales de:

recuperar la segunda información desde una posición especificada por la instrucción, comprendiendo la segunda información una indicación de la función de invalidar y borrar.

5. El método de acuerdo con la reivindicación 4, en el que la segunda información indica la función de invalidar y borrar 40 cuando el bit 52 de la segunda información es 0.

6. El método de acuerdo con la reivindicación 1, en el que el sistema informático comprende una o más memorias intermedias de traducción de direcciones para poner en la memoria caché la información de traducción de direcciones, comprendiendo el método el paso adicional de:

borrar las memorias intermedias de traducción de direcciones de los elementos de memorias intermedias de 45 traducción de direcciones asociadas con los elementos de la tabla de traducción de direcciones de la gama de dos o más elementos de la tabla de traducción de direcciones.

7. El método de acuerdo con la reivindicación 6, en el que las memorias intermedias de traducción de direcciones constan de una o más Memorias Intermedias de Traducción Adelantada (TLB).

8. El método de acuerdo con la reivindicación 6, en el que las memorias intermedias de traducción de direcciones 50 comprenden una cualquiera de entre:

una memoria intermedia de traducción de direcciones asociada con el procesador central,

una memoria intermedia de traducción de direcciones asociada con otro procesador central del sistema informático, o

todas las memorias intermedias de traducción de direcciones asociadas con el sistema informático.

9. El método de acuerdo con la reivindicación 1, en el que el paso de la determinación desde un código de operación comprende los pasos adicionales de: 5

extraer la instrucción desde el almacenamiento principal, comprendiendo la instrucción:

a) un primer campo para ubicar tercera información, comprendiendo la tercera información una localización del origen de la tabla de traducción de direcciones para invalidar; y

b) un segundo campo para ubicar cuarta información, comprendiendo la cuarta información una porción del índice de la tabla de traducción de direcciones; y para formar la primera dirección del elemento de la 10 tabla de traducción a partir de la tercera información en conjunción con la cuarta información.

10. El método de acuerdo con la reivindicación 9, donde en el primer campo se coloca o ubica la tercera información en un primer registrador con fines generales de arquitectura, en el que la ubicación del origen de la tabla de traducción de direcciones consta de una cualquiera de entre una dirección de una tabla de región o una dirección de una tabla de segmentos. 15

11. El método de acuerdo con la reivindicación 9, en el que la tercera información comprende además un campo de control del tipo de designación para designar una cualquiera de entre una región para la invalidación o una tabla de segmentos para la invalidación.

12. El método de acuerdo con la reivindicación 9, donde en el segundo campo se ubica la cuarta información, comprendiendo la cuarta información un primer campo del índice de región, un segundo campo del índice de región, un 20 tercer campo del índice de región, un campo del índice de segmento y la gama.

13. El método de acuerdo con la reivindicación 1, en el que la instrucción consta de 32 bits contiguos, que incluye un campo de código de operación que consta de 16 bits contiguos, un primer campo de operando que consta de 4 bits contiguos, un segundo campo de operando que consta de 4 bits contiguos, y un tercer campo de operando que consta de 4 bits contiguos, en el que los bits contiguos del primer campo son contiguos a los bits contiguos del segundo campo 25 y en el que los campos de operandos especifican los registradores con fines generales respectivos de un espacio del registrador de arquitectura informática.

14. El método de acuerdo con la reivindicación1, en el que el paso de la invalidación de la gama de dos o más elementos de la tabla de traducción de direcciones comprende el paso adicional de marcar inválidos, un bit inválido de cada uno de los elementos de la tabla de traducción de direcciones de la gama de dos o más elementos de la tabla de 30 traducción de direcciones.

15. El método de acuerdo con la reivindicación 1, en el que el sistema informático comprende además tablas de páginas, teniendo las tablas de páginas direcciones de almacenamiento principal reales, en el que las direcciones de almacenamiento principal reales comprenden una cualquiera de entre una dirección absoluta, una dirección real o una dirección física. 35

16. Un programa de ordenador o programa informático que comprende instrucciones para llevar a cabo todos los pasos del método de acuerdo con cualquier reivindicación precedente del método, cuando dicho programa de ordenador se ejecute en un sistema informático.

17. Un sistema que comprende medios adaptados para llevar a cabo todos los pasos del método de acuerdo con cualquier reivindicación precedente del método. 40

18. El sistema de la reivindicación 17, que comprende:

un almacenamiento principal;

uno o más procesadores centrales en comunicación con el almacenamiento principal;

registradores con fines generales de arquitectura accesibles para el/los procesador/es central/es;

tablas de traducción de direcciones para traducir dinámicamente direcciones virtuales para las direcciones del 45 almacenamiento principal, las tablas de traducción de direcciones siendo accesibles para el/los procesador/es central/es; y

una o más unidades de ejecución de instrucciones accesibles para el/los procesador/es central/es, las unidades de ejecución de instrucciones estando en comunicación con los registradores con fines generales de arquitectura, las unidades de ejecución de instrucciones ejecutando instrucciones para máquina extraídas del 50 almacenamiento principal.

Patentes similares o relacionadas:

INVALIDACIÓN DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 27 de Mayo de 2011, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para borrar elementos de memorias intermedias de traducción de direcciones en un sistema informático , comprendiendo el sistema […]

INVALIDACIÓN DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 27 de Mayo de 2011, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para borrar elementos de memorias intermedias de traducción de direcciones en un sistema informático , comprendiendo el sistema […]

INVALIDACION DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 19 de Abril de 2010, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar los elementos de tablas de traducción y borrar los correspondientes elementos de tablas de traducción dinámica de direcciones (DAT) […]

INVALIDACION DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 19 de Abril de 2010, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar los elementos de tablas de traducción y borrar los correspondientes elementos de tablas de traducción dinámica de direcciones (DAT) […]

MECANISMO DE EXTRACCIÓN DE ATRIBUTOS DE CACHÉ E INSTRUCCIÓN PARA EL MISMO, del 21 de Noviembre de 2011, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método de funcionamiento de un ordenador que comprende: la extracción , por un procesador de un sistema de procesamiento, de una […]

DESCUBRIMIENTO DE TOPOLOGÍA VIRTUAL PARA CONFIGURACIÓN DE ORDENADOR, del 21 de Noviembre de 2011, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Para un sistema de ordenador anfitrión dividido en particiones lógicamente que comprende procesadores anfitriones, un método para descubrir […]

PROCESADOR CON GENERADOR DE DIRECCIONES, del 11 de Marzo de 2011, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Procesador (1a, 1b) para procesar datos, que comprende: un generador de direcciones, que es operativo para generar una secuencia de direcciones que tienen […]

PROCESADOR CON GENERADOR DE DIRECCIONES, del 11 de Marzo de 2011, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Procesador (1a, 1b) para procesar datos, que comprende: un generador de direcciones, que es operativo para generar una secuencia de direcciones que tienen […]

USO DEL SISTEMA DE RENOMBRADO DE REGISTROS PARA EL ENVÍO DE LOS RESULTADOS INTERMEDIOS ENTRE INSTRUCCIONES CONSTITUTIVAS DE UNA INSTRUCCIÓN EXPANDIDA, del 21 de Febrero de 2011, de QUALCOMM INCORPORATED: Un procedimiento de ejecución de una instrucción expandida, que comprende: la conversión de la instrucción expandida en dos o más instrucciones […]

USO DEL SISTEMA DE RENOMBRADO DE REGISTROS PARA EL ENVÍO DE LOS RESULTADOS INTERMEDIOS ENTRE INSTRUCCIONES CONSTITUTIVAS DE UNA INSTRUCCIÓN EXPANDIDA, del 21 de Febrero de 2011, de QUALCOMM INCORPORATED: Un procedimiento de ejecución de una instrucción expandida, que comprende: la conversión de la instrucción expandida en dos o más instrucciones […]

Sistema de procesamiento de datos y método de procesamiento de datos, del 1 de Enero de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un sistema de procesamiento de datos , que comprende una unidad central de procesamiento, CPU , una memoria , un controlador […]

Múltiples conjuntos de campos de atributos dentro de una única entrada de tabla de páginas, del 25 de Septiembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento que comprende: traducir , por una primera unidad de procesamiento , una dirección de memoria virtual a una […]