METODO Y CIRCUITO PARA IMPLEMENTAR UN ELEMENTO TRANSLINEAL CON TECNOLOGIA CMOS.

Método y circuito para implementar un elemento translineal con tecnología CMOS.

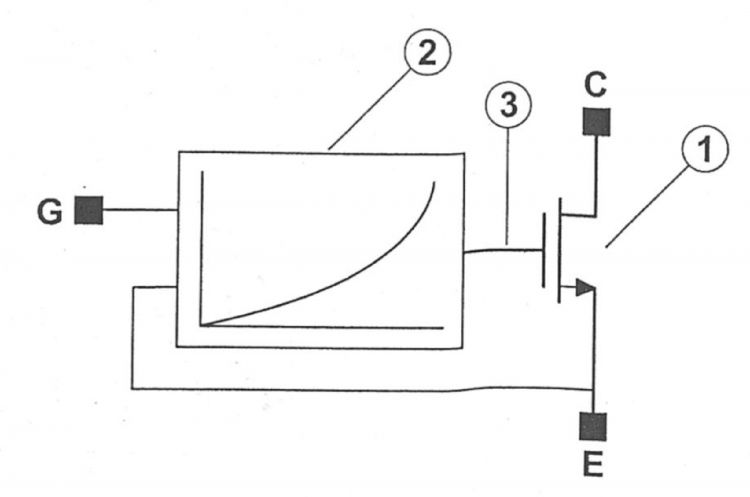

El método consiste en utilizar un transistor de efecto de campo MOS (1) como elemento translineal, realizando una predistorsión (2) de la tensión de puerta (G) del elemento translineal tomando como referencia la tensión de emisor (E) del elemento translineal y aplicar la tensión predistorsionada a la puerta (3) de dicho transistor, de forma que se compense la pérdida de transconductancia normalizada que sufren los transistores de efecto de campo MOS conforme aumenta la corriente que circula por ellos. Con esta predistorsión es posible extender el margen de corrientes durante el cual el transistor muestra la curva característica tensión-corriente exponencial necesaria para realizar su función de elemento translineal

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P200602780.

Solicitante: UNIVERSITAT POLITECNICA DE CATALUNYA.

Nacionalidad solicitante: España.

Provincia: BARCELONA.

Inventor/es: MADRENAS BOADAS,JORDI, FERNANDEZ MARTINEZ,DANIEL.

Fecha de Solicitud: 25 de Octubre de 2006.

Fecha de Publicación: .

Fecha de Concesión: 22 de Junio de 2010.

Clasificación Internacional de Patentes:

- G05F5/00 FISICA. › G05 CONTROL; REGULACION. › G05F SISTEMAS DE REGULACION DE VARIABLES ELECTRICAS O MAGNETICAS (regulación de la distribución en el tiempo o de la periodicidad de impulsos en los sistemas de radar o de radionavegación G01S; regulación de la corriente o de la tensión, especialmente adaptada para su uso en relojes electrónicos G04G 19/02; sistemas que funcionan en bucle cerrado para regular variables no eléctricas por medios eléctricos G05D; control de la alimentación de energía eléctrica a los computadores digitales G06F 1/26; para obtener las características de funcionamiento deseadas de electroimanes con armadura H01F 7/18; regulación de redes de distribución de energía eléctrica H02J; regulación de la carga de baterías H02J 7/00; regulación del valor de salida de convertidores estáticos, p. ej. reguladores de conmutación, H02M; regulación del valor de salida de generadores eléctricos H02N, H02P 9/00; control de transformadores, reactancias o bobinas de choque H02P 13/00; regulación de la respuesta de frecuencia, ganancia, potencia de salida máxima, amplitud o ancho de banda de amplificadores H03G; regulación de la sintonización de circuitos resonantes H03J; control de generadores de oscilaciones o de impulsos electrónicos H03L; regulación de las características de líneas de transmisión H04B; control de fuentes eléctricas de luz H05B 39/04, H05B 41/36, H05B 45/10, H05B 45/20, H05B 47/10; control eléctrico de aparatos de rayos X H05G 1/30). › Sistemas de regulación de variables eléctricas por detección de las desviaciones de la señal eléctrica de entrada del sistema y controlando por estas desviaciones un dispositivo interior al sistema para obtener una señal de salida regulada.

Clasificación PCT:

- G05F5/00 G05F […] › Sistemas de regulación de variables eléctricas por detección de las desviaciones de la señal eléctrica de entrada del sistema y controlando por estas desviaciones un dispositivo interior al sistema para obtener una señal de salida regulada.

Fragmento de la descripción:

Método y circuito para implementar un elemento translineal con tecnología CMOS.

Sector de la técnica

La presente invención se refiere a un método y circuito electrónicos capaces de implementar, en tecnología CMOS, la funcionalidad de un elemento translineal según la definición dada por B. Gilbert en "Translinear Circuits: A proposed Classification", publicado en la revista Electronics Letters del año 1975. El elemento translineal es el núcleo de proceso de los circuitos translineales, que se utilizan en el procesado analógico para realizar con precisión operaciones como amplificadores, productos, divisiones, potencias y raíces en el dominio de la corriente. También se emplean en el filtrado de señales dentro de las técnicas log-domain, osciladores, detectores de fase y PLLs. Existe un interés creciente en el diseño translineal debido a que éste proporciona soluciones sencillas, compactas y muy adaptables, con un consumo energético extremadamente bajo y grandes márgenes dinámicos, lo que los hace muy atractivos para numerosas aplicaciones.

Estado de la técnica

Históricamente, al hablar de elemento translineal se pensaba en un transistor bipolar BJT. Por dichos motivos históricos, se ha asimilado la nomenclatura de los terminales de los transistores bipolares al elemento translineal, esto es, un terminal de emisor (E), puerta o base (G) o (B) y colector (C). En su forma ideal (o teórica) sus características son un ancho de banda infinito, una corriente de puerta nula y una corriente de colector exponencial con diferencia de tensión entre la puerta y el emisor del elemento translineal, esto es,

donde I0 corresponde a la corriente específica, uT al voltaje térmico, y los parámetros ? y ? son magnitudes adimensionales que escalan, respectivamente, la corriente de colector y la diferencia de tensión entre la puerta y el emisor y dependen de la implementación concreta del elemento translineal.

Tomando la derivada de la expresión anterior respecto a la tensión VGE y dividiendo entre la corriente de colector IC obtenemos la transconductancia normalizada del elemento translineal ideal, que es

Nótese que la transconductancia normalizada es constante para el elemento translineal ideal.

El transistor bipolar (BJT) se considera el elemento translineal por excelencia y es el que se ha venido utilizando desde los inicios del diseño translineal. Sigue la ecuación (1) durante ocho décadas de corriente de colector, tomando ? como el área relativa de la unión base emisor, ? como un valor próximo a la unidad y el terminal de puerta del elemento translineal ideal como el terminal de base del BJT. No obstante, cuando el transistor bipolar se utiliza como elemento translineal, ciertas de sus características, como la ganancia de corriente ß finita o la resistencia de emisor, afectan negativamente a la respuesta del circuito translineal o limitan el margen de corriente de colector utilizable.

La ß finita, o la existencia de corriente de puerta no nula, es la principal causa de error en los circuitos translineales implementados con transistores bipolares. Dicha no idealidad implica un drenaje de corriente no previsto por la ecuación (1) y que, dependiendo de la implementación y del tipo de polarización que se utilice, se puede mitigar en parte aumentando ligeramente alguna de las polarizaciones, aunque ello no es siempre posible. En circuitos translineales dinámicos (filtros log-domain), se ha publicado un análisis por V.W. Leung y G.W. Roberts bajo el título "Effects of transistor nonidealities on high-order log-domain ladder filter frequency responses" en la revista IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing del año 2000, que indica que la ß finita afecta principalmente el factor de calida Q de un filtro biquad implementado con integradores log-domain, debido a las pérdidas que estos últimos sufren. En implementaciones de filtros clase AB, donde aparecen picos importantes de corriente, también empeoran significativamente la distorsión del filtro y la intermodulación según se indica en el informe técnico "1-V Log Domain Filters" de C. Enz y M. Punzenberger del proyecto ALPINS, elaborado en 1998.

La resistencia de emisor supone un incremento en la tensión base-emisor del transistor bipolar, y por tanto, una desviación de la función de transferencia exponencial del elemento translineal, principalmente en la región de alta corriente. El efecto sobre lazos estáticos depende de sobre cuál de los elementos circule la alta corriente y de su tipo de polarización. En filtros log-domain su efecto es una alteración de la frecuencia de corte y la aparición de distorsión por intermodulación con altas amplitudes de señal y altas frecuencias, según análisis anteriormente citado de V.W. Leung y G.W. Roberts. Para reducir estos efectos es necesario aumentar adecuadamente las dimensiones del transistor, a pesar de que ello aumente las capacidades parásitas y limite la operación a altas frecuencias. Otras soluciones al problema de la resistencia de emisor se encuentran en la patente estadounidense núm. 6,225,850 de Ion E. Opris "Series resistance compensation in translinear circuits" de mayo de 2001.

Hoy en día, debido a la rápida expansión de la electrónica digital CMOS en el mercado, el elevado coste económico de los procesos de fabricación BiCMOS les resta atractivo a las implementaciones con transistores bipolares desde un punto de vista industrial, por lo que se han estudiado profusamente las posibilidades del transistor MOS como elemento translineal. Desafortunadamente, la curva característica del MOS es muy compleja y no existe un único modelo analítico para todo el margen de conducción del dispositivo, por lo que, típicamente, se divide dicho margen de conducción en tres regiones, denominadas de inversión débil, moderada y fuerte. La zona de inversión débil presenta una transconductancia aproximadamente constante, esto es, sigue la expresión (1) con fidelidad y, por tanto, puede utilizarse en diseño translineal, no obstante, la transconductancia cae y no se mantiene constante en las zonas de inversión moderada y fuerte, y esto hace que no sea posible hacer trabajar el MOS como elemento translineal en estas zonas de la misma forma que se podría hacer en inversión débil o con un transistor bipolar BJT.

La zona de inversión débil del transistor MOS está situada, para la corriente de drenador, entre el nivel de ruido y 500nA (unas tres décadas) para un transistor de relación de aspecto de canal aproximadamente unitaria. En esta zona, si el transistor está en saturación, la corriente sigue la expresión

Donde ID0 es la corriente específica, n es la pendiente del efecto sustrato y uT el voltaje térmico. Nótese que si surtidor y sustrato están a la misma tensión, la corriente de drenador que circula a través de él sigue la expresión (1) tomando ? como la relación de aspecto W/L, ? como la inversa de la pendiente del efecto sustrato (n) y los terminales de emisor y colector del elemento translineal ideal como les terminales de surtidor y drenador del MOST, respectivamente.

Existen dos inconvenientes importantes en las soluciones translineales MOS en inversión débil. En primer lugar está el reducido margen dinámico con el que cuentan, que hace disminuir progresivamente la precisión de la respuesta conforme la corriente que circula a través de los elementos translineales aumenta y el transistor se acerca a la zona de inversión moderada. En esta zona la corriente que circula por el MOS no crece tan rápidamente como lo requerido por la ecuación (3) con lo que el MOS deja de comportarse como elemento translineal. Una solución parcial a este problema es maximizar la relación de aspecto W/L para que la zona de inversión débil se extienda a valores mayores de corriente. Esto agrava el segundo de los inconvenientes de las soluciones translineales MOS, y es el reducido ancho de banda con el que cuentan (típicamente inferior...

Reivindicaciones:

1. Método para implementar elementos translineales consistente en utilizar técnicas de predistorsión o preénfasis con el objetivo de compensar la pérdida de transconductancia de un dispositivo electrónico y aproximar en un margen de operación más amplio el funcionamiento de un elemento translineal ideal, caracterizado por sensar las tensiones o corrientes de control del elemento translineal y utilizar la diferencia de dichas tensiones o corrientes, o una aproximación de la misma, para generar una señal de control que se aplica al dispositivo electrónico.

2. El método de la reivindicación 1 caracterizado porque el dispositivo electrónico es un transistor MOS.

3. El método de cualquiera de las reivindicaciones anteriores caracterizado porque dicho método implementa un elemento con característica exponencial en lugar de un elemento translineal.

4. Circuito electrónico que genera una corriente exponencial, o una aproximación de la misma, en uno de sus terminales en función de una diferencia de tensiones de control, consistente en un dispositivo de salida (M1) conectado al terminal que genera dicha corriente y, al menos, otro dispositivo de referencia (M2) conectado a las tensiones de control, caracterizado por corregir las desviaciones respecto a dicha exponencial mediante la comparación de la corriente del dispositivo de referencia con una magnitud constante (Ibias1) para generar una diferencia de tensiones de control que se aplica al dispositivo de salida.

5. El circuito de las reivindicación 4 caracterizado porque la comparación se realiza con una magnitud variable.

6. El circuito de las reivindicaciones 4 y 5 caracterizado porque una o más tensiones de control se conectan a seguidores de tensión (M5, M7).

7. El circuito de las reivindicaciones 4 a 6 caracterizado porque la corriente generada por el dispositivo de referencia se copia mediante uno o varios espejos de corriente (M3, M4).

8. El circuito de las reivindicaciones 4 a 7 caracterizado porque se aprovecha la resistencia parásita de uno o varios dispositivos electrónicos (M4, M5, M6) para permitir un mejor ajuste de la curva característica en alguna o todas las partes de la curva característica.

9. El circuito de las reivindicaciones 4 a 8 caracterizado porque alguno o todos los dispositivos electrónicos son transistores MOS.

10. El circuito de las reivindicaciones 4 a 9 caracterizado porque se añaden condensadores a uno o varios nodos del circuito para mejorar la respuesta dinámica del circuito.

11. El circuito de las reivindicaciones 4 a 10 caracterizado porque el circuito se utiliza como elemento translineal.

Patentes similares o relacionadas:

Alimentación de tensión variable de alta eficacia, del 3 de Junio de 2020, de SNAPTRACK INC.: Una fase de fuente de alimentación , que comprende: una alimentación de tensión variable de alta eficacia para generar una tensión […]

DISPOSITIVO ELECTRÓNICO PARA TELÉFONO PÚBLICO., del 8 de Abril de 2019, de TELIDIA INNOVACIÓN Y DESARROLLO, S.L.U: 1. Dispositivo electrónico para teléfono público que comprende medios electrónicos de control y medios de conexión , caracterizado porque los […]

TELÉFONO PÚBLICO DE INTERIORES, del 8 de Abril de 2019, de TELIDIA INNOVACIÓN Y DESARROLLO, S.L.U: 1. Teléfono público de interiores que comprende medios electrónicos de control y al menos un sistema de entrada de monedas , caracterizado porque comprende un […]

DISPOSITIVO ELECTRÓNICO PARA TELÉFONO PÚBLICO, del 8 de Abril de 2019, de TELIDIA INNOVACIÓN Y DESARROLLO, S.L.U: 1. Dispositivo electrónico para teléfono público que comprende medios electrónicos de control y medios de conexión , caracterizado porque los […]

Método de protección para información de datos relativos a un dispositivo electrónico y su circuito de protección, del 25 de Abril de 2018, de Shenzhen Xinguodu Technology Co. Ltd: Un circuito para proteger información de datos de un equipo electrónico, que comprende un procesador y un dispositivo electrónico conectado con el procesador […]

Aparato y método para corregir datos adquiridos, del 28 de Febrero de 2018, de LSIS Co., Ltd: Un aparato para corregir datos adquiridos, que incluye una unidad de procesamiento de topología, TP, para adquirir datos que incluyen información […]

Sistema con detección de tensión en la entrada, con regulación de tensión de salida y programable, del 8 de Noviembre de 2016, de GARCÍA HOYA, Francisco Javier: Sistema con detección de tensión en la entrada, con regulación de tensión de salida y programable. La invención se refiere a un sistema de regulación de tensión […]

Regulador integrado, en particular regulador de tensión, y dispositivo de control para medios de protección de personas, del 12 de Octubre de 2016, de ROBERT BOSCH GMBH: Regulador integrado, en particular regulador de tensión para medios de protección de personas en un vehículo, con un elemento de regulación (T), el cual transforma una señal […]