PROCEDIMIENTO DE GESTION DE MEMORIA NO VOLATIL EN UNA TARJETA DE CHIP.

Procedimiento de gestión del acceso a una memoria no volátil(VNVM),

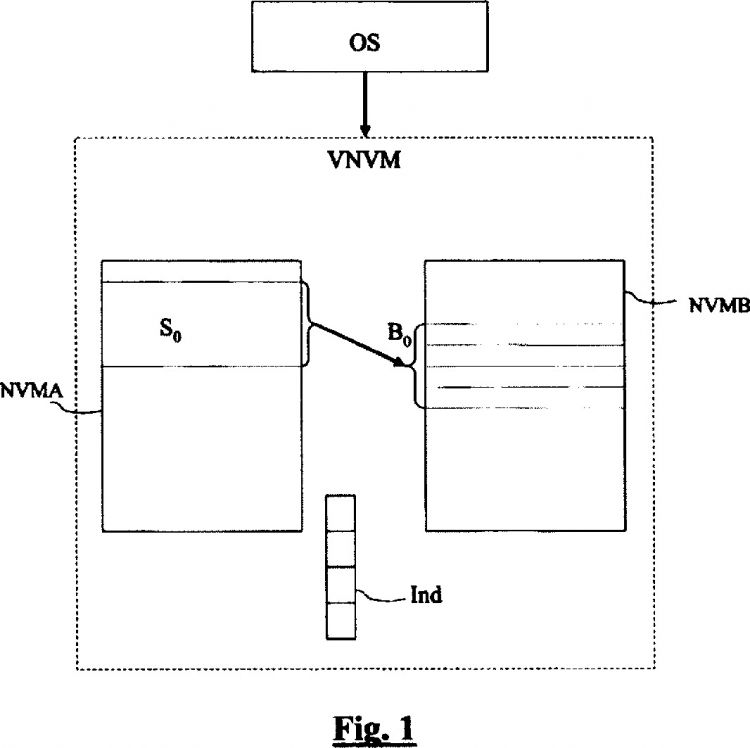

caracterizado porque dicha memoria no volátil (VNVM) resulta de la asociación de una memoria no volátil de un primer tipo (NVMA)que incluye características de alta capacidad y de gran granulosidad con una memoria no volátil del segundo tipo (NVMB) que incluye características de baja capacidad y fina granulosidad, de modo que dicha memoria no volátil (VNVM) resultante de dicha asociación presenta características de capacidad de dicha memoria no volátil del primer tipo con las características de granulosidad de dicha memoria no volátil del segundo tipo, dichas memorias no volátiles del primer y segundo tipo (NVMA, NVMB) son memorias de semi-conductor

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2006/063244.

Solicitante: GEMALTO SA.

Nacionalidad solicitante: Francia.

Dirección: 6, RUE DE LA VERRERIE,92190 MEUDON.

Inventor/es: GARNIER,THIERRY.

Fecha de Publicación: .

Fecha Concesión Europea: 10 de Febrero de 2010.

Clasificación Internacional de Patentes:

- G06F12/08B12

Clasificación PCT:

- G06F12/08 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 12/00 Acceso, direccionamiento o asignación en sistemas o arquitecturas de memoria (entrada digital a partir de, o salida digital hacia soportes de registro, p. ej. hacia unidades de almacenamiento de disco G06F 3/06). › en sistemas de memorias jerárquicas, p. ej. sistemas de memoria virtual.

Fragmento de la descripción:

Procedimiento de gestión de memoria no volátil en una tarjeta de chip.

La presente invención se refiere a la gestión de la memoria no volátil en entornos de ejecución embarcados y concierne particularmente la gestión de las memorias de este tipo en un aparato electrónico portátil dotado de un microcontrolador que agrupa un procesador y memorias de tipo volátil y no volátil, como una tarjeta inteligente por ejemplo.

Actualmente, para los dispositivos de este tipo, se intenta ir hacia memorias no volátiles de gran capacidad, que son actualmente del orden del centenar de Kilobyte (Kb), pero se prevé a largo plazo capacidades de varios megabytes (Mb).

Ahora bien, las memorias no volátiles de gran capacidad, por ejemplo las memorias Flash de tipo NAND o NOR, aunque se benefician de una velocidad de escritura por bitio generalmente elevada, presentan un inconveniente importante cuando se prevé utilizarlos en el ámbito de la tarjeta inteligente. Este inconveniente tiene relación con su granulosidad, que dista mucho de estar acabada. Típicamente, el borrado de estas memorias no volátiles de gran capacidad se efectúa por bloque 8 Kb, 16 Kb, 32 Kb, e incluso más y la escritura puede hacerse por página de 512 bytes. En efecto, cuanto más importante es la granulosidad, menos descodificación debe hacerse y mejor es la densidad a nivel integración de la memoria.

Asimismo, la gestión de estas memorias debe adaptarse a este bajo grado de fragmentación asociado a ellas por construcción, haciendo que resulte difícil prever utilizar memorias no volátiles de grandes capacidades en las tarjetas inteligentes, o modificar un byte, habida cuenta de las grandes dificultades sobre el aspecto integridad de los datos propios a los sistemas de explotación embarcados para tarjeta inteligente, podrá necesitar el borrado, la escritura o el desplazamiento de bloques consecuentes de datos.

En efecto, el respeto de la integridad de los datos en las tarjetas inteligentes requiere para cada fase de gestión de la memoria, por ejemplo durante la escritura de un dato, varias manipulaciones. Así pues, es necesario preservar tanto el antiguo como el nuevo dato hasta que no se haya escrito con certeza el dato, de modo a cerciorarse de no perder ningún dato en caso de fallo de alimentación por ejemplo. Puesto que este proceso, implica muchas más manipulaciones en la memoria, solamente podrá preverse escribir un dato cuando el dato en cuestión se refiere a un byte por ejemplo, pero resultará imposible cuando la memoria debe ser regida por bloques de 32 Kb por ejemplo. El tiempo para efectuar varias escrituras de un bloque de 32 Kb resulta entonces redhibitorio.

Para evitar estas dificultades físicas, los fabricantes de memorias de semiconductor proponen a los proveedores de sistemas de explotación que modulen su oferta de manera a conseguir distintos compromisos entre la capacidad, la granulosidad de los bloques memorias y la velocidad de acceso. No obstante, continuamos en el mismo esquema, según el cual las memorias de gran capacidad abarcan sectores de memoria muy importantes, del tipo 16, 32,64 Kb, lo que resulta, como ya se ha visto, especialmente difícil de administrar en el contexto tarjetas inteligentes en términos de integridad de los datos y de resultado.

Ya se conoce la patente US 5, 860, 083 que enseña un mecanismo de memoria oculta para acelerar los accesos a las aplicaciones registradas en un disco duro. El sistema propuesto asocia un disco duro y una unidad de memoria flash.

Por otra parte, existen métodos para acelerar los accesos a las memorias de gran capacidad. Generalmente, estos métodos utilizan importantes recursos en RAM con el objetivo esencial de aumentar los resultados sin obligaciones particulares de consumo e integridad de los datos. Por otro lado, no hay ningún problema en cuanto a la granulosidad para los RAM, puesto que presentan un acceso aleatorio a un byte. No obstante, estas soluciones existentes no son compatibles con el ámbito que enfoca la presente invención que es aquel de las tarjetas inteligentes. En efecto, la memoria RAM es costosa, necesita mucho espacio y consume bastante, además no garantiza la integridad de los datos puesto que se trata de una memoria de tipo volátil.

La invención pone la mira en solucionar estos inconvenientes, proponiendo un sistema de gestión memoria, que responda a las características exigidas por los aparatos electrónicos portátiles, de tipo tarjeta inteligente de nueva generación, que permita emplear memorias no volátiles de gran capacidad, garantizando al mismo tiempo una granularidad fina de los accesos a las memorias que sea compatible con las dificultades vinculadas al tratamiento de la integridad de los datos en las tarjetas inteligentes, al mismo tiempo que buenos resultados en términos de velocidad de tratamiento de los accesos a la memoria.

Así pues, la invención tiene por objeto un procedimiento de gestión del acceso a una memoria no volátil, caracterizada porque dicha memoria no volátil resulta de la asociación de una memoria no volátil de un primer tipo que incluye primeras características de capacidad y de granulosidad, con una memoria no volátil de un segundo tipo que incluye segundas características de capacidad y granulosidad, de modo que dicha memoria no volátil resultante de dicha asociación presenta las características de capacidad de dicha memoria no volátil del primer tipo con las características de granulosidad de dicha memoria no volátil del segundo tipo.

Ventajosamente, el acceso al menos a un bloque de la memoria no volátil del primer tipo incluye las siguientes etapas que consisten en:

Según un modo de realización, cuando se ha accedido a dicho bloque en escritura, incluye, además, una etapa de actualización de los datos de dicho bloque en el emplazamiento correspondiente de dicho bloque en dicha memoria del primer tipo.

Según este modo de realización, la etapa de actualización de dicho bloque en memoria no volátil del primer tipo consiste en borrar en tarea de fondo dicho bloque en la memoria del primer tipo a raíz de su desplazamiento hacia la memoria no volátil del segundo tipo y a colocar de nuevo si fuera necesario dicho bloque, una vez que se haya efectuado la operación de escritura, en el emplazamiento correspondiente al dicho bloque desplazado en la memoria no volátil del primer tipo.

En una variante, el reemplazo en memoria no volátil del primer tipo de datos de dicho bloque actualizados sólo interviene en el caso de que se reclame el espacio ocupado en memoria no volátil del segundo tipo por este bloque, con el fin de colocar allí otro bloque. En el caso contrario, el sistema puede acceder a los datos de la memoria virtual no volátil acomodándose de manera transparente al hecho de que estos datos están colocados físicamente en memoria no volátil del primero o segundo tipo.

Ventajosamente, según un modo de realización, el procedimiento incluye la colocación de un bloque de datos ya desplazado en la memoria no volátil del segundo tipo en su emplazamiento correspondiente en memoria no volátil del primer tipo, antes del acceso al menos a otro bloque de la memoria no volátil del primer tipo.

Ventajosamente, el procedimiento incluye el registro de por lo menos un identificador en una memoria persistente, previsto para establecer un vinculo entre cada bloque desplazado de la memoria no volátil del primer tipo, y la porción de memoria correspondiente de la memoria no volátil del segundo tipo.

Preferiblemente, se asocia una memoria no volátil del primer tipo que incluye características de alta capacidad y gran granulosidad con una memoria no volátil del segundo tipo que incluye características de baja capacidad y fina granulosidad.

La invención concierne igualmente un aparato electrónico portátil, dotado con medios de tratamiento de datos que incluyen un microprocesador y memorias de tipo volátil y no volátil, caracterizado porque la memoria no volátil resulta de la asociación de una memoria no volátil de un primer tipo que incluye primeras características de capacidad y granulosidad,...

Reivindicaciones:

1. Procedimiento de gestión del acceso a una memoria no volátil(VNVM), caracterizado porque dicha memoria no volátil (VNVM) resulta de la asociación de una memoria no volátil de un primer tipo (NVMA)que incluye características de alta capacidad y de gran granulosidad con una memoria no volátil del segundo tipo (NVMB) que incluye características de baja capacidad y fina granulosidad, de modo que dicha memoria no volátil (VNVM) resultante de dicha asociación presenta características de capacidad de dicha memoria no volátil del primer tipo con las características de granulosidad de dicha memoria no volátil del segundo tipo, dichas memorias no volátiles del primer y segundo tipo (NVMA, NVMB) son memorias de semi-conductor.

2. Procedimiento según la reivindicación 1, caracterizado porque el acceso de al menos a un bloque (S0) de la memoria no volátil del primer tipo (NVMA) incluye las siguientes etapas que consisten en:

3. Procedimiento según la reivindicación 2, caracterizado porque, se accede a dicho bloque (S0) en escritura, incluye por otro lado una etapa de actualización de datos del dicho bloque en el emplazamiento correspondiente del dicho bloque en dicha memoria del primer tipo.

4. Procedimiento según la reivindicación 3, caracterizado porque la etapa de actualización de dicho del bloque (S0) en memoria no volátil del primer tipo (NVMA) consiste en borrar en tarea de fondo de dicho bloque (S0) en la memoria del primer tipo (NVMA) a raíz de su desplazamiento hacia la memoria no volátil del segundo tipo (NVMB) y en colocar de nuevo dicho bloque, una vez la operación de escritura efectuada, en el emplazamiento correspondiente al dicho bloque desplazado en la memoria no volátil del primer tipo (NVMA).

5. Procedimiento según cualquiera de las reivindicaciones 2 a 4, caracterizado porque incluye la nueva colocación de un bloque de datos ya desplazado en la memoria no volátil del segundo tipo (NVMB) en su emplazamiento correspondiente en memoria no volátil del primer tipo (NVMA), previamente al acceso de por lo menos a otro bloque (S0) de la memoria no volátil del primer tipo (NVMA).

6. Procedimiento según cualquiera de las reivindicaciones 2 a 5, caracterizado porque incluye el registro de por lo menos un identificador (Ind) en una memoria persistente, prevista para establecer un vínculo entre cada bloque (S0) desplazado de la memoria no volátil del primer tipo (NVMA), y la porción de memoria correspondiente de la memoria no volátil del segundo tipo (NVMB).

7. Aparato electrónico portátil, dotado con medios de tratamiento de datos que incluyen un microprocesador y memorias de tipo volátil y no volátil, caracterizado porque la memoria no volátil (VNVM) resulta de la asociación de una memoria no volátil de un primer tipo (NVMA) que incluye características de alta capacidad y gran granulosidad, con una memoria no volátil de un segundo tipo que incluye características de baja capacidad y de fina granulosidad, de modo que dicha memoria no volátil (VNVM) resultante de dicha asociación presenta las características de capacidad de dicha memoria no volátil del primer tipo con las características de granulosidad de dicha memoria no volátil del segundo tipo, dichas memorias no volátiles del primer y segundo tipo (NVMA, NVMB) son memorias de semi conductor.

8. Aparato electrónico portátil según la reivindicación 7, caracterizado porque la memoria no volátil del primer tipo es una memoria Flash de tipo NOR o NAND.

9. Aparato electrónico portátil según las reivindicaciones 7 u 8, caracterizado porque la memoria no volátil del segundo tipo es una memoria EEPROM, FeRAM, MRAM, o PCRAM.

10. Aparato electrónico portátil según cualquiera de las reivindicaciones 7 a 9, caracterizado porque incluye medios para la aplicación del procedimiento según cualquiera de las reivindicaciones 2 a 6.

11. Aparato electrónico portátil según cualquiera de las reivindicaciones 7 a 10, caracterizado porque este aparato es una tarjeta de memoria.

Patentes similares o relacionadas:

Método y aparato para almacenar en caché, del 3 de Junio de 2020, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un método para habilitar el almacenamiento en caché de una sección de un archivo multimedia en un Equipo de Usuario, UE , conectado […]

Procedimiento y aparato para gestionar memoria caché en sistema de comunicación, del 15 de Enero de 2020, de SAMSUNG ELECTRONICS CO., LTD.: Un procedimiento para gestionar una memoria caché por una estación base, BS, en un sistema de comunicación inalámbrica, comprendiendo el procedimiento: […]

Método y aparato para un acceso a memoria basado en hilos en un procesador multihilo, del 11 de Septiembre de 2019, de QUALCOMM INCORPORATED: Método para acceder a una memoria por un procesador multihilo , comprendiendo el método: determinar un identificador de hilo asociado a un […]

Dispositivo de inspección de anomalías, unidad central de procesamiento y método de inspección de anomalías, del 7 de Agosto de 2019, de MITSUBISHI HEAVY INDUSTRIES, LTD.: Una unidad de inspección de fallos provista para una unidad central de procesamiento conectada a una unidad de gestión de memoria , comprendiendo la unidad […]

Método y dispositivo para procesar datos, del 12 de Junio de 2019, de ZTE CORPORATION: Un método para procesar datos, que comprende: después de recibir datos introducidos por un bus de datos, de acuerdo con una indicación de destino de los datos y una indicación […]

Actualización de resultados de consulta de base de datos almacenados en memoria caché, del 29 de Mayo de 2019, de AMADEUS S.A.S.: Un método de actualización de unos resultados de consulta de base de datos precalculados en un sistema de base de datos distribuido , […]

Actualización de resultados de consulta de base de datos almacenados en memoria caché, del 29 de Mayo de 2019, de AMADEUS S.A.S.: Un método de actualización de unos resultados de consulta de base de datos precalculados en un sistema de base de datos distribuido , […]

Uso de compresión de memoria para reducir la carga de compromiso de memoria, del 6 de Mayo de 2019, de Microsoft Technology Licensing, LLC: Un método de reducir una cantidad de compromiso de memoria para un programa en un dispositivo de cálculo , comprendiendo el método: determinar […]

Sistema de almacenamiento distribuido, del 24 de Abril de 2019, de Soon-Shiong, Patrick: Un sistema de almacenamiento distribuido que comprende: una base de datos de co 5 ntenido que almacena datos de contenido digital que comprenden […]