GENERADOR DE NUMEROS REALMENTE ALEATORIOS.

Generador de números realmente aleatorios.

Generador de números aleatorios,

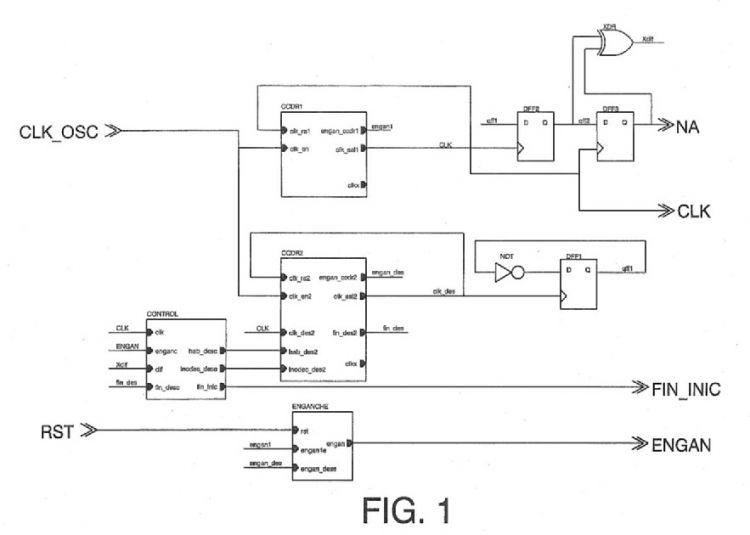

que comprende un primer circuito para compensación digital de retardo (CCDR1), un segundo circuito para compensación digital de retardo (CCDR2), un primer flip-flop (DFF1), un segundo flip-flop (DFF2) y un tercer flip-flop (DFF3). Adicionalmente el generador comprende un circuito de control y enganche.

Dicho generador consigue un estado estacionario de generación de números aleatorios logrando un cierto desfase entre una primera señal de reloj (CLK) y una segunda señal de reloj (clk_des), de tal modo que el segundo flip-flop (DFF2) trabaje en un estado de metaestabilidad

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P200702299.

Solicitante: UNIVERSIDAD DEL PAIS VASCO-EUSKAL HERRIKO UNIBERTSITATEA.

Nacionalidad solicitante: España.

Provincia: VIZCAYA.

Inventor/es: BIDARTE PERAITA,UNAI, ASTARLOA CUELLAR,ARMANDO, LAZARO ARROTEGUI,JESUS, ZULOAGA IZAGUIRRE,AITZOL.

Fecha de Solicitud: 17 de Agosto de 2007.

Fecha de Publicación: .

Fecha de Concesión: 1 de Julio de 2010.

Clasificación Internacional de Patentes:

- G06F7/58R

- H03K3/84 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 3/00 Circuitos para la generación de impulsos eléctricos; Circuitos monoestables, biestables o multiestables (H03K 4/00 tiene prioridad; para generadores de funciones digitales en ordenadores G06F 1/02). › Generación de impulsos que tienen una distribución estadística predeterminada de un parámetro, p. ej. generadores de impulsos aleatorios.

Clasificación PCT:

- G06F7/58 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 7/00 Métodos o disposiciones para el procesamiento de datos actuando sobre el orden o el contenido de los datos tratados (circuitos lógicos H03K 19/00). › Generadores de números aleatorios o seudoaleatorios.

- H03K3/84 H03K 3/00 […] › Generación de impulsos que tienen una distribución estadística predeterminada de un parámetro, p. ej. generadores de impulsos aleatorios.

Fragmento de la descripción:

Generador de números realmente aleatorios.

Campo de la invención

La presente invención pertenece al campo de la electrónica digital, más concretamente al de los generadores de números aleatorios.

Antecedentes de la invención

Cuando una aplicación requiere números aleatorios se pueden emplear secuencias de números aleatorios existentes o generar nuevas secuencias. El primer caso consiste en emplear secuencias aleatorias disponibles en bases de datos, lo cual tiene la ventaja de emplear datos cuyas características estadísticas han sido previamente analizadas, pero, por el contrario, existe un grave problema de seguridad. Por este motivo, lo más habitual es generar los números aleatorios en tiempo real en un generador que reúna los requisitos impuestos por la aplicación. Requisitos habituales para las secuencias generadas son: distribución uniforme, autocorrelación tendente a cero, varianza determinada, período largo, velocidad de generación determinada, etc.

La mayor parte de los generadores de números aleatorios son en realidad generadores de números pseudoaleatorios, es decir, son secuencias de números generadas de manera determinística. Las secuencias parecen aleatorias, pero se calculan mediante la aplicación de un algoritmo a un número inicial o semilla. Siempre que se parta de una misma semilla la secuencia generada será exactamente la misma. Su mayor ventaja es que permiten la generación a alta velocidad, sólo requieren una semilla inicial y se pueden reproducir exactamente. Existen multitud de estos generadores probados y descritos en detalle actualmente y se pueden destacar, entre otros, los siguientes métodos: generadores de congruencia lineal, generadores de desplazamiento de bits, generadores de Fibonacci y de Galois, generadores no lineales, etc.

Aunque los generadores de números pseudoaleatorios pueden generar secuencias aleatorias con buenas características estadísticas a alta velocidad, no son adecuados para aplicaciones en las que prime la seguridad. Tal es el caso de las secuencias aleatorias para criptografía, en las que debe ser imposible calcular el siguiente número de una secuencia conocidos todos los anteriores, es decir la secuencia ha de ser realmente aleatoria. Un generador de números aleatorios con unas características estadísticas y de seguridad adecuadas para aplicaciones tan exigentes como pueden ser las de criptografía, ha de emplear como circuito fundamental no un generador de números pseudoaleatorios sino un generador de números realmente aleatorios. Los generadores de números realmente aleatorios se basan en el muestreo de variables estocásticas presentes en procesos físicos, tales como la desintegración radiactiva, el lanzamiento de un dado, el tiempo transcurrido entre dos pulsaciones de teclado o ratón de un usuario, fenómenos meteorológicos, etc.

Cuando la secuencia aleatoria fundamental se genera a alta velocidad suele presentar parámetros estadísticos que no se ajustan a los deseados, como por ejemplo distinta probabilidad de aparición de los valores 0 y 1, o correlación en los bits cercanos en el tiempo. Esto es consecuencia de las características intrínsecas de los procesos físicos que originan las secuencias aleatorias. Por este motivo normalmente un circuito adicional realiza un post-procesamiento de la secuencia aleatoria fundamental obtenida en el generador de números realmente aleatorios para eliminar características estadísticas indeseadas y conseguir una secuencia aleatoria válida para la aplicación. Otro objetivo del post-procesamiento consiste en minimizar el efecto que cambios ambientales en parámetros como la temperatura puedan tener en la secuencia aleatoria.

Existen multitud de propuestas de probada eficacia para implementar lo que se han denominado circuitos postprocesadores (unas basadas en técnicas lineales como el método de von Neyman, las funciones de hash o los registros de desplazamiento con realimentación lineal y otras basadas en técnicas no lineales para mejorar la seguridad) pero, por el contrario, la generación de secuencias realmente aleatorias en base a circuitos digitales implementables en tecnología FPGA (Field Programmable Gate Array) o ASIC (Application Specific Integrated Circuit) continúa siendo un reto.

Por razones prácticas, los fenómenos físicos más adecuados para los generadores de números realmente aleatorios son aquellos integrables en circuitos electrónicos de estado sólido, ya que las aplicaciones que hacen uso de los números aleatorios se implementan casi en su totalidad en circuitos integrados. Dos métodos convencionales son el ruido térmico de resistencias o uniones PN y los osciladores controlados por tensión, pero requieren circuitos analógicos. Dado que la gran mayoría de los circuitos electrónicos empleados hoy día para tareas de procesamiento y control son digitales, resultan mucho más interesantes los generadores de números realmente aleatorios implementables en su totalidad en tecnología digital.

Descripción de la invención

La invención se refiere a un generador de números aleatorios.

En un primer aspecto de la invención, dicho generador comprende un primer circuito para compensación digital de retardo, un segundo circuito para compensación digital de retardo, un primer flip-flop, un segundo flip-flop y un tercer flip-flop.

El primer circuito para compensación digital de retardo y el segundo circuito para compensación digital de retardo están conectados en un primer puerto de entrada a una señal de un oscilador.

El primer circuito para compensación digital de retardo tiene como salida de su primer puerto de salida una primera señal de reloj, dicha primera señal de reloj realimenta el primer circuito para compensación digital de retardo en un segundo puerto de entrada.

El segundo circuito para compensación digital de retardo tiene como salida de su primer puerto de salida una segunda señal de reloj, dicha segunda señal de reloj realimenta el segundo circuito para compensación digital de retardo en un segundo puerto de entrada.

El primer flip-flop tiene como señal de reloj la segunda señal de reloj y usa la señal de salida de dicho primer flip-flop invertida como entrada del primer flip-flop.

El segundo flip-flop tiene como señal de reloj la primera señal de reloj y usa la señal de salida del primer flip-flop como señal de entrada.

El tercer flip-flop tiene como señal de reloj la primera señal de reloj y usa la señal de salida del segundo flip-flop como señal de entrada, obteniendo como señal de salida del tercer flip-flop una señal aleatoria.

El segundo circuito para compensación digital de retardo adicionalmente podrá comprender un tercer puerto de entrada, un cuarto puerto de entrada y un quinto puerto de entrada.

Adicionalmente, el generador de números aleatorios podrá comprender un circuito de control con un primer puerto de entrada, un segundo puerto de entrada, un tercer puerto de entrada, un cuarto puerto de entrada, un primer puerto de salida, un segundo puerto de salida y un tercer puerto de salida.

El primer puerto de salida del circuito de control está conectado con el cuarto puerto de entrada del segundo circuito para compensación digital de retardo, el segundo puerto de salida del circuito de control con el quinto puerto de entrada del segundo circuito para compensación digital de retardo, y el primer puerto de entrada del circuito de control estando conectado con la primera señal de reloj.

Adicionalmente, el generador de números aleatorios podrá comprender un circuito de enganche con un primer puerto de entrada, un segundo puerto de entrada, un tercer puerto de entrada y un puerto de salida.

En dicho circuito de enganche, la entrada al primer puerto de entrada es una señal de reset. El segundo puerto de entrada está conectado al segundo puerto de salida del primer circuito para compensación digital de retardo, el tercer puerto de entrada al segundo puerto de salida del segundo circuito para compensación digital de retardo y el puerto se salida al segundo puerto de entrada del circuito de control.

El circuito de enganche podrá estar configurado de tal modo que su puerto de salida proporciona una señal de enganche cuando la señal de reset pasa a estado inactivo, y las señales de los segundos puertos de salida del primer y segundo circuito para compensación digital de retardo se activan.

El segundo circuito para compensación digital de retardo podrá comprender una línea de retardo programable,...

Reivindicaciones:

1. Generador de números aleatorios, que comprende

un primer circuito para compensación digital de retardo (CCDR1), un segundo circuito para compensación digital de retardo (CCDR2), un primer flip-flop (DFF1), un segundo flip-flop (DFF2) y un tercer flip-flop (DFF3),

estando conectado el primer circuito para compensación digital de retardo (CCDR1) en un primer puerto de entrada (clk_en1) y el segundo circuito para compensación digital de retardo (CCDR2) en un primer puerto de entrada (clk_en2) a una señal de un oscilador (CLK_OSC),

el primer circuito para compensación digital de retardo (CCDR1) tiene como salida de su primer puerto de salida (clk_sal1) una primera señal de reloj (CLK), dicha primera señal de reloj (CLK) realimenta el primer circuito para compensación digital de retardo (CCDR1) en un segundo puerto de entrada (clk_ra1),

el segundo circuito para compensación digital de retardo (CCDR2) tiene como salida de su primer puerto de salida (clk_sal2) una segunda señal de reloj (clk_des), dicha segunda señal de reloj (clk_des) realimenta el segundo circuito para compensación digital de retardo (CCDR2) en un segundo puerto de entrada (clk_ra2),

el primer flip-flop (DFF1) tiene como señal de reloj la segunda señal de reloj (clk_des) y usa la señal de salida (dff1) de dicho primer flip-flop (DFF1) invertida como entrada del primer flip-flop (DFF1),

el segundo flip-flop (DFF2) tiene como señal de reloj la primera señal de reloj (CLK) y usa la señal de salida del primer flip-flop (dff1) como señal de entrada,

el tercer flip-flop (DFF3) tiene como señal de reloj la primera señal de reloj (CLK) y usa la señal de salida del segundo flip-flop (dff2) como señal de entrada, obteniendo como señal de salida (NA) del tercer flip-flop (DFF3) una señal aleatoria.

2. Generador de números aleatorios según la reivindicación 1, caracterizado por que el segundo circuito para compensación digital de retardo (CCDR2) adicionalmente comprende un tercer puerto de entrada (clk_des2), un cuarto puerto de entrada (hab_des2) y un quinto puerto de entrada (indec_des2).

3. Generador de números aleatorios según la reivindicación 2, caracterizado por que adicionalmente comprende un circuito de control (CONTROL) con un primer puerto de entrada (clk), un segundo puerto de entrada (enganc), un tercer puerto de entrada (dif), un cuarto puerto de entrada (fin_desc), y un primer puerto de salida (hab_desc), un segundo puerto de salida (incdec_desc) y un tercer puerto de salida (fin_inic),

estando conectado el primer puerto de salida (hab_desc) del circuito de control (CONTROL) con el cuarto puerto de entrada (hab_des2) del segundo circuito para compensación digital de retardo (CCDR2), el segundo puerto de salida (incdec_desc) del circuito de control (CONTROL) con el quinto puerto de entrada (indec_des2) del segundo circuito para compensación digital de retardo (CCDR2), el primer puerto de entrada (cik) del circuito de control (CONTROL) estando conectado con la primera señal de reloj (CLK).

4. Generador de números aleatorios según la reivindicación 3, caracterizado por que adicionalmente comprende un circuito de enganche (ENGANCHE) con un primer puerto de entrada (rst), un segundo puerto de entrada (engan1e), un tercer puerto de entrada (engan_dese) y un puerto de salida (engan),

siendo la entrada al primer puerto de entrada (rst) una señal de reset (RST), estando conectado el segundo puerto de entrada (engan1e) al segundo puerto de salida (engan_ccdr1) del primer circuito para compensación digital de retardo (CCDR1), el tercer puerto de entrada (engan_dese) al segundo puerto de salida (engan_ccdr2) del segundo circuito para compensación digital de retardo (CCDR2) y el primer puerto se salida (engan) al segundo puerto de entrada (enganc) del circuito de control (CONTROL).

5. Generador de números aleatorios según la reivindicación 4, caracterizado por que el puerto de salida (engan) del circuito de enganche (ENGANCHE) activa una señal de enganche (ENGAN) cuando la señal de reset (RST) pasa a estado inactivo, y las señales de los segundos puertos de salida (engan_ccdr1, engan_ccdr2) del primer circuito para compensación digital de retardo (CCDR1) y del segundo circuito para compensación digital de retardo (CCDR2) se activan.

6. Generador de números aleatorios según la reivindicación 1, caracterizado por que el primer circuito para compensación digital de retardo (CCDR1) comprende una línea de retardo programable (LRP) y una lógica de estado (LE),

la línea de retardo programable (LRP) comprende una pluralidad de puertas de retardo individuales, dicha línea de retardo programable (LRP) tiene como señal de entrada la señal del primer puerto de entrada (clk_en1) y como señal de salida la señal del primer puerto de salida (clk_sal1), dicha señal de salida realimenta la línea de retardo programable (LRP) en el segundo puerto de entrada (clk_ra1),

la lógica de estado (LE) transmite su señal de salida a través del segundo puerto de salida (engan_ccdr1).

7. Generador de números aleatorios según la reivindicación 1, caracterizado por que el segundo circuito para compensación digital de retardo (CCDR2) comprende una línea de retardo programable (LRP), un ajuste dinámico de desfase (ADD), y una lógica de estado (LE),

la línea de retardo programable (LRP) comprende una pluralidad de puertas de retardo individuales, dicha línea de retardo programable (LRP) tiene como señal de entrada la señal del primer puerto de entrada (clk_en2) y como señal de salida la señal del primer puerto de salida (clk_sal2), dicha señal de salida realimenta la línea de retardo programable (LRP) en el segundo puerto de entrada (clk_ra2),

el ajuste dinámico de desfase (ADD) cuenta como entradas la señal del tercer puerto de entrada (clk_des2), la señal del cuarto puerto de entrada (hab_des2) y la señal del quinto puerto de entrada (indec_des2), y como señal del salida la señal de un tercer puerto de salida (fin_des2),

la lógica de estado (LE) transmite su señal de salida a través del segundo puerto de salida (engan_ccdr2).

8. Generador de números aleatorios según la reivindicación 1, caracterizado por que la señal de salida del segundo flip-flop (dff2) y la señal de salida del tercer flip-flop (NA) son señales de entrada de una puerta XOR, siendo la señal de salida de dicha puerta XOR (xdif) la señal de entrada del tercer puerto de entrada (dif) del circuito de control (CONTROL).

9. Generador de números aleatorios según las reivindicaciones 3 u 8, caracterizado por que el circuito de control (CONTROL) comprende un primer contador configurado para determinar el número máximo de ciclos a evaluar la señal de salida de la puerta XOR (xdif), un segundo contador configurado para memorizar la situación de desfase actual, en base al número de solicitudes de incremento y decremento de fase, un registro configurado para memorizar la amplitud de una ventana (VM) y un comparador del valor del segundo contador y de un desfase definido dentro de dicha ventana (VM).

10. Procedimiento para generar números aleatorios a la salida de un tercer flip-flop (NA), dicho tercer flip-flop (DFF3) teniendo como señal de entrada la señal de salida de un segundo flip-flop (dff2), caracterizado por que comprende las siguientes etapas:

11. Procedimiento según la reivindicación 10, caracterizado por que el desfase de trabajo (Ft) es la semisuma del primer valor de desfase (F1) y del segundo valor de desfase (F2).

12. Procedimiento según cualquiera de las reivindicaciones 10-11, caracterizado por que una vez alcanzado el desfase de trabajo (Ft) se produce la activación de la señal del tercer puerto de salida (fin_inic) de un circuito de control (CONTROL) siendo la señal de salida del tercer flip-flop (NA) aleatoria a partir de dicha activación.

Patentes similares o relacionadas:

Procedimiento y equipo para generar números aleatorios utilizando la arquitectura de un doble oscilador y caos de tiempo continuo, del 19 de Julio de 2017, de TUBITAK: Generador de bits aleatorios que incluye una arquitectura de doble oscilador que comprende un oscilador rápido con frecuencia rápida f(fast) […]

Generación de números aleatorios usando caos de tiempo continuo, del 8 de Junio de 2016, de TUBITAK: Método para generar bits de datos aleatorios binarios a partir de una señal eléctrica caótica (v1) desde un oscilador caótico autónomo o no autónomo […]

Equipo y procedimiento para generar bits aleatorios, del 27 de Enero de 2016, de SIEMENS AKTIENGESELLSCHAFT: Equipo para generar bits aleatorios (ZB) que incluye:

varios equipos de representación (21 - 2m), estando preparado el equipo de representación […]

Equipo y procedimiento para generar bits aleatorios, del 27 de Enero de 2016, de SIEMENS AKTIENGESELLSCHAFT: Equipo para generar bits aleatorios (ZB) que incluye:

varios equipos de representación (21 - 2m), estando preparado el equipo de representación […]

Control de potencia automático para un sistema de comunicación de acceso múltiple por division de código (CDMA), del 2 de Octubre de 2013, de INTERDIGITAL TECHNOLOGY CORPORATION: Metodo para controlar niveles de potencia de transmisión de una unidad de abonado en un acceso múltiple pordivisión de código, CDMA, el metodo […]

ELEMENTO MULTIVIBRADOR RECONFIGURABLE BASADO EN CONTROL DE CAOS, del 10 de Mayo de 2013, de INSTITUTO POTOSINO DE INVESTIGACION CIENTIFICA Y TECNOLOGICA , AC: Un elemento reconfigurable basado en dinámica nolineal (caótico) es adaptado para implementar los tres diferentes configuraciones de multivibrador. […]

ELEMENTO MULTIVIBRADOR RECONFIGURABLE BASADO EN CONTROL DE CAOS, del 10 de Mayo de 2013, de INSTITUTO POTOSINO DE INVESTIGACION CIENTIFICA Y TECNOLOGICA , AC: Un elemento reconfigurable basado en dinámica nolineal (caótico) es adaptado para implementar los tres diferentes configuraciones de multivibrador. […]

Aparato y método para generar códigos de aleatorización en el sistema de UMTS de comunicaciones de móviles, del 9 de Mayo de 2012, de SAMSUNG ELECTRONICS CO., LTD.: Un generador de códigos de aleatorización, que comprende: un primer generador de secuencias m para generar una primera secuencia m utilizando […]

GENERADOR DE SECUENCIAS DE RUIDO PSEUDOALEATORIO DE ROTACION RAPIDA., del 16 de Octubre de 2005, de QUALCOMM INCORPORATED: Generador de secuencias de ruido pseudoaleatorio (PN) de rotación rápida que comprende: - un registro de desplazamiento con retroalimentación […]

DISPOSITIVO CON CIRCUITO(S) LOGICO(S) PARA LA GENERACION DE UNA SEÑAL ALEATORIA, del 1 de Marzo de 2009, de ETAT FRANCAIS REPRESENTE PAR LE DELEGUE GENERAL POUR L'ARMEMENT: Dispositivo para la generación de una señal aleatoria, caracterizado porque contiene un circuito electrónico en estado transitorio, así como […]

DISPOSITIVO CON CIRCUITO(S) LOGICO(S) PARA LA GENERACION DE UNA SEÑAL ALEATORIA, del 1 de Marzo de 2009, de ETAT FRANCAIS REPRESENTE PAR LE DELEGUE GENERAL POUR L'ARMEMENT: Dispositivo para la generación de una señal aleatoria, caracterizado porque contiene un circuito electrónico en estado transitorio, así como […]