ESTRUCTURA DE BUS ESCALABLE.

Un procedimiento de comunicación entre un componente emisor (102) y un componente receptor (104) por medio de un bus (106),

comprendiendo el bus canales primero (108, 108 a-d) y segundo (110, 110a-b), en el que cada uno de los canales primero y segundo comprende una pluralidad de subcanales (108a-d), comprendiendo el procedimiento: emitir desde el componente emisor por el primer canal información de dirección de primera lectura y escritura, señales de control de primera lectura y escritura, y datos de primera escritura, en el que el componente emisor emite una porción de la información de la primera dirección de escritura por un primero (108a) de los subcanales durante un primer periodo temporal (401) de manera concurrente con una porción de las señales de control de escritura por un segundo (108b) de los subcanales; emitiéndose una porción de los datos de primera escritura por un tercero (108c) de los subcanales durante el mismo primer periodo temporal; emitir, a continuación, desde el componente emisor por el primer canal información de dirección de segunda lectura y escritura, señales de control de segunda lectura y escritura, y datos de segunda escritura, en el que el componente emisor emite una porción de la información de la dirección de segunda escritura por un primero (108a) de los subcanales durante un segundo periodo temporal (405) de manera concurrente con una porción de las señales de control de segunda escritura por un segundo (108b) de los subcanales; y emite una porción de los datos de segunda escritura por el primero (108a) de los subcanales durante un tercer periodo temporal (407); transmitir una señal desde el componente emisor al componente receptor de tal modo que el componente receptor pueda distinguir entre la información de dirección de lectura y de escritura, las señales de control de lectura y escritura y la emisión de datos de escritura por el primer canal; almacenar la emisión de datos de escritura primera y segunda por el primer canal en el componente receptor en base a la información de la dirección de escritura primera y segunda y de las señales de control de escritura primera y segunda; recuperar datos de lectura primera y segunda del componente receptor en base a la información de dirección de lectura primera y segunda y a las señales de control de lectura primera y segunda; y emitir desde el componente receptor los datos recuperados de lectura primera y segunda por el segundo canal

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2005/003789.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 5775 MOREHOUSE DRIVE SAN DIEGO, CA 92121 ESTADOS UNIDOS DE AMERICA.

Inventor/es: HOFMANN,RICHARD GERARD, SCHAFFER,MARK MICHAEL.

Fecha de Publicación: .

Fecha Solicitud PCT: 3 de Febrero de 2005.

Fecha Concesión Europea: 11 de Agosto de 2010.

Clasificación PCT:

- G06F13/40 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 13/00 Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16). › Estructura del bus.

- G06F13/42 G06F 13/00 […] › Protocolo de transferencia para bus, p. ej. interbloqueo; Sincronización.

Clasificación antigua:

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania.

Fragmento de la descripción:

Estructura de bus escalable.

Campo

La presente revelación versa, en general, acerca de sistemas digitales y, más específicamente, acerca de una estructura de bus escalable.

Antecedentes

Los ordenadores han revolucionado la industria de la electrónica al permitir que se lleven a cabo con rapidez sofisticadas tareas de procesamiento. Estas sofisticadas tareas pueden llevarse a cabo con sistemas que contienen un elevado número de componentes complejos que se comunican entre sí de manera rápida y eficiente usando un bus. Un bus es un canal o una vía entre componentes en un ordenador, un subsistema informático, un sistema informático u otro sistema electrónico.

Muchos buses residentes en un ordenador se han implementado tradicionalmente como buses compartidos. Un bus compartido proporciona un medio para que cualquier número de componentes se comuniquen a través de una vía o de un canal común. En años recientes, la tecnología del bus compartido se ha visto complementada con las conexiones de conmutación punto a punto. Las conexiones de conmutación punto a punto proporcionan una conexión directa entre dos componentes del bus mientras se comunican entre sí. Pueden usarse múltiples enlaces directos para permitir que varios componentes se comuniquen a la vez.

Una configuración común para un ordenador incluye un microprocesador con memoria del sistema. Puede usarse un bus de sistema con una anchura de banda elevada para soportar comunicaciones entre ambos. Además, también puede haber un bus para periféricos que se usa para transferir datos a los periféricos. En algunos casos, también puede haber un bus de configuración, que se usa con el fin de programar recursos diversos. Pueden usarse puentes para transferir datos de manera eficiente entre los buses con anchura de banda mayor y menor, así como para proporcionar la necesaria traducción de protocolos. Cada uno de estos buses ha sido implementado con protocolos diferentes y pueden tener una amplia variación en los requisitos de rendimiento entre ellos.

El uso de estructuras de buses múltiples en un ordenador ha proporcionado durante muchos años una solución viable. Sin embargo, a medida que la superficie y la potencia se presentan como las consideraciones fundamentales del diseño de los circuitos integrados, se hace cada vez más deseable reducir la complejidad de la estructura del bus.

Resumen

Según la presente invención, se proporciona un procedimiento de comunicación entre un componente emisor y un componente receptor por un bus, según la reivindicación 1, y de un sistema de procesamiento según la reivindicación 12.

El procedimiento puede incluir, además, almacenar los datos de escritura emitidos por el primer canal en el componente receptor en base a la información de la dirección de escritura y de las señales de control de la escritura, recuperar los datos de lectura del componente receptor en base a la información de la dirección de lectura y de las señales de control de la lectura, y emitir desde el componente receptor los datos de lectura recuperados por el segundo canal.

Los medios de emisión pueden ser configurados para transmitir una señal al componente receptor, de modo que el componente receptor pueda distinguir entre la información de la dirección de lectura y escritura, las señales de control de lectura y escritura, y la emisión de los datos de escritura por el primer canal.

El sistema de procesamiento puede incluir in bus que tiene canales primero y segundo. El sistema de procesamiento puede incluir medios emisores para emitir por el primer canal información de la dirección de lectura y escritura, señales de control de lectura y escritura y datos de escritura. El sistema de procesamiento puede incluir, además, medios receptores para almacenar los datos de escritura emitidos por el primer canal en base a la información de la dirección de escritura y de las señales de control de escritura, recuperar datos de lectura en base a la información de la dirección de lectura y a las señales de control de lectura, y emitir los datos de lectura recuperados por el segundo canal al componente emisor. Los medios emisores pueden incluir, además, medios para transmitir una señal a los medios receptores, de manera que los medios receptores puedan distinguir entre la información de la dirección de lectura y escritura, las señales de control de lectura y escritura y los datos de escritura emitidos por el primer canal.

Se entiende que otras realizaciones de la presente invención se harán inmediatamente evidentes a las personas versadas en la técnica a partir de la siguiente descripción detallada, en la que se muestran y se describen diversas realizaciones de la invención a título de ilustración. Como se apreciará, la invención es susceptible de otras realizaciones diferentes, y sus varios detalles son susceptibles de modificación en diversos aspectos diferentes, todos sin apartarse del espíritu y el ámbito de la presente invención. En consecuencia, debe considerarse que los dibujos y la descripción detallada tienen naturaleza ilustrativa y no restrictiva.

Breve descripción de los dibujos

Los aspectos de la presente invención se ilustran a título de ejemplo y no a título de limitación en los dibujos adjuntos, en los que:

la Fig. 1 es un diagrama conceptual de bloques que ilustra un ejemplo de una conexión punto a punto en un bus de dos canales entre dos componentes en un sistema de procesamiento;

la Fig. 2 es un cronograma que muestra una operación de lectura y escritura entre dos componentes en un sistema de procesamiento que tiene una conexión punto a punto en un bus de dos canales;

la Fig. 3 es un diagrama conceptual de bloques que ilustra un ejemplo de una conexión punto a punto en un bus de dos canales de alto rendimiento entre dos componentes en un sistema de procesamiento;

la Fig. 4 es un diagrama conceptual de bloques que ilustra la naturaleza multiplexada por división de tiempo del bus de alto rendimiento de la Fig. 3;

la Fig. 5 es un diagrama conceptual de bloques que ilustra un ejemplo de una conexión punto a punto en un bus de dos canales de bajo ancho de banda entre dos componentes en un sistema de procesamiento;

la Fig. 6 es un diagrama conceptual de bloques que ilustra la naturaleza multiplexada por división de tiempo del bus de bajo ancho de banda de la Fig. 5; y

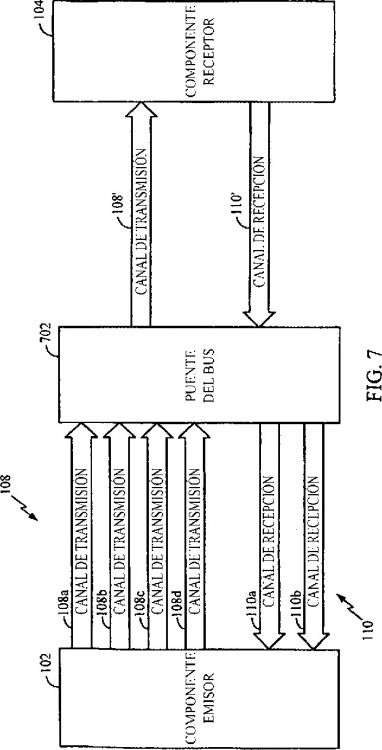

la Fig. 7 es un diagrama conceptual de bloques que ilustra un ejemplo de una conexión punto a punto entre un componente de alto rendimiento y un componente de bajo ancho de banda por medio de un puente.

Descripción detallada

La descripción detallada expuesta en lo que sigue en relación con los dibujos adjuntos se presenta como una descripción de diversas realizaciones de la presente invención, y no se contempla que represente las únicas realizaciones en las que puede ponerse en práctica la presente invención. La descripción detallada incluye detalles específicos con el fin de proporcionar una comprensión minuciosa de la presente invención. Sin embargo, resultará evidente para las personas expertas en la técnica que la presente invención puede ponerse en práctica sin estos detalles específicos. En algunos casos, se muestran en forma de diagrama de bloques estructuras y componentes muy conocidos para evitar impedir ver claramente los conceptos de la presente invención. Los acrónimos y otra terminología descriptiva pueden usarse simplemente por comodidad y claridad, y no se contempla que limiten el ámbito de la invención.

Diversos componentes en un sistema de procesamiento pueden comunicarse a través de un bus. El bus puede ser escalable, en términos de la anchura y de la frecuencia del reloj para soportar los requisitos de ancho de banda de los diversos componentes. El bus también puede usar una arquitectura y un protocolo de señalización comunes para todas las configuraciones escalables. Esto puede lograrse reduciendo el protocolo de señalización del bus únicamente a las señales necesarias ya sea para transmitir o para recibir información.

El bus puede estar configurado con un "canal de transmisión" que proporciona un medio genérico para emitir información desde un componente emisor a un componente receptor usando el mismo protocolo de señalización de manera multiplexada por división de tiempo. Un "canal de recepción" también puede usar el mismo protocolo de señalización para emitir información desde el...

Reivindicaciones:

1. Un procedimiento de comunicación entre un componente emisor (102) y un componente receptor (104) por medio de un bus (106), comprendiendo el bus canales primero (108, 108 a-d) y segundo (110, 110a-b), en el que cada uno de los canales primero y segundo comprende una pluralidad de subcanales (108a-d), comprendiendo el procedimiento:

emitir desde el componente emisor por el primer canal información de dirección de primera lectura y escritura, señales de control de primera lectura y escritura, y datos de primera escritura,

en el que el componente emisor emite una porción de la información de la primera dirección de escritura por un primero (108a) de los subcanales durante un primer periodo temporal (401) de manera concurrente con una porción de las señales de control de escritura por un segundo (108b) de los subcanales; emitiéndose una porción de los datos de primera escritura por un tercero (108c) de los subcanales durante el mismo primer periodo temporal;

emitir, a continuación, desde el componente emisor por el primer canal información de dirección de segunda lectura y escritura, señales de control de segunda lectura y escritura, y datos de segunda escritura,

en el que el componente emisor emite una porción de la información de la dirección de segunda escritura por un primero (108a) de los subcanales durante un segundo periodo temporal (405) de manera concurrente con una porción de las señales de control de segunda escritura por un segundo (108b) de los subcanales; y emite una porción de los datos de segunda escritura por el primero (108a) de los subcanales durante un tercer periodo temporal (407);

transmitir una señal desde el componente emisor al componente receptor de tal modo que el componente receptor pueda distinguir entre la información de dirección de lectura y de escritura, las señales de control de lectura y escritura y la emisión de datos de escritura por el primer canal;

almacenar la emisión de datos de escritura primera y segunda por el primer canal en el componente receptor en base a la información de la dirección de escritura primera y segunda y de las señales de control de escritura primera y segunda; recuperar datos de lectura primera y segunda del componente receptor en base a la información de dirección de lectura primera y segunda y a las señales de control de lectura primera y segunda; y

emitir desde el componente receptor los datos recuperados de lectura primera y segunda por el segundo canal.

2. El procedimiento de la reivindicación 1 en el que el primer periodo temporal es un ciclo de reloj, el tercer periodo temporal es un ciclo de reloj que sigue inmediatamente al segundo periodo temporal.

3. El procedimiento de la reivindicación 1 en el que el segundo (108b) de los subcanales es operable para que lleve una segunda porción de los datos de escritura segunda durante el tercer periodo temporal (407).

4. El procedimiento de la reivindicación 2 en el que las señales de lectura y escritura comprenden una pluralidad de calificadores de transferencia y de habilitadores del byte de escritura.

5. El procedimiento de la reivindicación 1 en el que los datos de escritura comprenden una pluralidad de cargas útiles y en el que el componente emisor (102) emite una porción de la información de dirección de lectura y escritura entre una porción primera y una segunda de una de las cargas útiles.

6. El procedimiento de la reivindicación 1 que comprende, además, la transmisión de una señal desde el componente receptor hasta el componente emisor para dar acuse de las emisiones por el primer canal (108, 108 a-d).

7. El procedimiento de la reivindicación 6 que comprende, además, la repetición de una emisión de la misma porción de la información de la dirección de lectura o escritura, de las señales de control de lectura o escritura, o de los datos de escritura en respuesta a la transmisión de señales desde el componente receptor (104) hasta el componente emisor (102).

8. El procedimiento de la reivindicación 7 en el que los datos de escritura comprenden una pluralidad de cargas útiles y en el que se emite reiteradamente la misma porción de la información de la dirección de lectura o las señales de control de lectura durante un periodo que sigue a la emisión de una porción de la información de la dirección de escritura asociada con una de las cargas útiles, pero antes de que dicha una de las cargas útiles sea emitida por completo al componente receptor (104), comprendiendo el procedimiento, además,

suspender la emisión reiterada al final del periodo temporal, completar la emisión de dicha una de las cargas útiles, y repetir la emisión de la misma porción de la información de la dirección de lectura o de las señales de control de lectura siguiendo la terminación de la emisión de dicha una de las cargas útiles.

9. El procedimiento de la reivindicación 1 que comprende, además, la transmisión de una señal desde el componente receptor (104) hasta el componente emisor (102) para indicar cuándo el componente receptor está emitiendo los datos de lectura.

10. El procedimiento de la reivindicación 9 que comprende, además, la emisión por el segundo canal (110, 110a-b) de instrucciones desde el componente receptor (104), y la transmisión de señales desde el componente receptor hasta el componente emisor (102), de tal manera que el componente emisor pueda distinguir entre los datos de lectura y las instrucciones.

11. El procedimiento de la reivindicación 10 en el que el segundo canal comprende una pluralidad de subcanales (110a-b), emitiendo un primero (110a) de los subcanales una porción de los datos de lectura durante un periodo temporal de forma concurrente con la emisión de una porción de las instrucciones por un segundo (110b) de los subcanales durante el mismo periodo temporal.

12. Un sistema (100) de procesamiento que comprende:

un bus (106) que tiene canales primero (108, 108 a-d) y segundo (110, 110a-b), en el que cada uno de los canales primero y segundo comprende una pluralidad de subcanales (108a-d);

medios de emisión para emitir por el primer canal información de dirección de primera y segunda lectura y escritura, señales de control de primera y segunda lectura y escritura, y datos de segunda escritura,

en el que los medios de emisión están configurados para emitir una porción de la información de la primera dirección de escritura por un primero (108a) de los subcanales durante un primer periodo temporal (401) de manera concurrente con una porción de las señales de control de escritura por un segundo (108b) de los subcanales; emitiéndose una porción de los datos de primera escritura por otro (108c) de los subcanales durante el mismo primer periodo temporal;

emitir una porción de la información de la dirección de segunda escritura por el primero (108a) de los subcanales durante un segundo periodo temporal (405) de manera concurrente con una porción de las señales de control de segunda escritura por el segundo (108b) de los subcanales; y emitir una porción de los datos de segunda escritura por el primero (108a) de los subcanales durante un tercer periodo temporal (407); y

medios de recepción para almacenar la emisión de datos de escritura primera y segunda por el primer canal en base a la información de la dirección de escritura primera y segunda y de las señales de control de escritura primera y segunda, recuperando datos de lectura primera y segunda en base a la información de dirección de lectura primera y segunda y a las señales de control de lectura primera y segunda; y emitir al medio emisor los datos recuperados de lectura primera y segunda por el segundo canal;

en el que los medios emisores comprenden, además, medios para transmitir una señal a los medios receptores, de tal manera que los medios receptores puedan distinguir entre la información de la dirección de lectura y escritura, las señales de control de lectura y escritura y los datos de escritura emitidos por el primer canal.

13. El sistema de procesamiento de la reivindicación 12 en el que el primer periodo temporal es un ciclo de reloj, el segundo periodo temporal es un ciclo de reloj que sigue inmediatamente al primer periodo temporal.

14. El sistema (100) de procesamiento de la reivindicación 12 en el que los medios (104) de emisión están configurados, además, para emitir una segunda porción de los datos de escritura por el segundo (108b) de los subcanales durante el segundo periodo temporal (407).

15. El sistema (100) de procesamiento de la reivindicación 12 en el que las señales de lectura y escritura comprenden una pluralidad de calificadores de transferencia y de habilitadores del byte de escritura.

16. El sistema (100) de procesamiento de la reivindicación 12 en el que los datos de escritura comprenden una pluralidad de cargas útiles y en el que los medios emisores (102) están configurados, además, para emitir una porción de la información de dirección de lectura y escritura entre una porción primera y una segunda de una de las cargas útiles.

17. El sistema (100) de procesamiento de la reivindicación 12 en el que los medios receptores (104) están configurados, además, para transmitir una señal a los medios emisores (102) para dar acuse de las emisiones por el primer canal (108, 108 a-d).

18. El sistema (100) de procesamiento de la reivindicación 17 en el que los medios emisores (102) están configurados, además, para repetir una emisión de la misma porción de la información de la dirección de lectura o escritura, de las señales de control de lectura o escritura, o de los datos de escritura si no se recibe acuse de tal emisión desde los medios receptores (104).

19. El sistema (100) de procesamiento de la reivindicación 17 en el que los medios emisores (102) comprenden, además, un mecanismo de retroceso de dirección.

20. El sistema (100) de procesamiento de la reivindicación 12 en el que los medios receptores (104) están configurados, además, para transmitir una señal a los medios emisores (102) para indicar cuándo los medios receptores están emitiendo los datos de lectura.

21. El sistema (100) de procesamiento de la reivindicación 20 en el que los medios receptores (104) están configurados, además, para emitir por el segundo canal instrucciones y para transmitir señales a los medios emisores (102), de tal manera que los medios emisores puedan distinguir entre los datos de lectura y las instrucciones.

22. El sistema (100) de procesamiento de la reivindicación 21 en el que el segundo canal (110, 110a-b) comprende una pluralidad de subcanales (100a-b), estando configurados los medios receptores (104), además, para emitir una porción de los datos de lectura por un primero (110a) de los subcanales durante un periodo temporal de forma concurrente con la emisión de una porción de las instrucciones por un segundo (110b) de los subcanales durante el mismo periodo temporal.

Patentes similares o relacionadas:

Método para implementar un bus industrial de banda ancha de campo de internet, del 17 de Junio de 2020, de Kyland Technology Co., Ltd: Un método para implementar un bus industrial de banda ancha de campo de internet, caracterizado por que, el método es aplicable a un sistema de arquitectura […]

Aparato para establecer la dirección de un módulo utilizando un reloj, del 17 de Junio de 2020, de LEXMARK INTERNATIONAL, INC.: Un circuito integrado específico de la aplicación (ASIC) que comprende: un pin de alimentación; un pin de masa; un pin de reloj I2C; un pin […]

Sistema de arquitectura de bus de banda ancha de campo de internet de la industria, del 3 de Junio de 2020, de Kyland Technology Co., Ltd: Un sistema de arquitectura de bus de banda ancha de campo de Internet de la industria, caracterizado por que, el sistema comprende un controlador de bus […]

Método para gestionar la configuración del bus de banda ancha del campo de internet industrial, del 3 de Junio de 2020, de Kyland Technology Co., Ltd: Un método para gestionar la configuración de un bus de banda ancha del campo de internet industrial, caracterizado por que, el método es aplicable a […]

Método para implementar un bus de campo en tiempo real de banda ancha de Internet industrial, del 29 de Abril de 2020, de Kyland Technology Co., Ltd: Un método para implementar un bus de campo en tiempo real de banda ancha de Internet industrial, en donde el método puede aplicarse a una red de transferencia […]

Procedimiento para hacer funcionar un sistema de transmisión de datos y sistema de transmisión de datos, del 29 de Abril de 2020, de Siemens Mobility GmbH: Procedimiento para hacer funcionar un sistema de transmisión de datos en el que - un primer equipo de transmisión de datos está conectado […]

Sistema de autenticación e información para instrumentos quirúrgicos reutilizables, del 8 de Abril de 2020, de Covidien LP (100.0%): Un método para comunicar datos a través de un bus, el método que comprende: autenticar un componente quirúrgico utilizando un microchip […]

Método y aparato para detectar contrapresión de mensajes, del 8 de Abril de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de detección de contrapresión de paquetes, en donde el método se aplica a un dispositivo que tiene un puerto de Interconexión de […]