ESQUEMA DE ARBITRAJE DE ACCESO A BUS.

Un sistema de procesamiento, que comprende:

un bus (110);

una pluralidad de procesadores (102) acoplados al bus;

y

un árbitro (108) de bus configurado para asignar una ponderación de segundo nivel a uno o más de los procesadores y para conceder de manera secuencial acceso al bus al uno o más procesadores que presentan una ponderación de segundo nivel durante una parte (204) inicial de un intervalo (202) de bus en base a las ponderaciones de segundo nivel asignadas, estando configurado además el árbitro de bus para conceder acceso al bus a uno cualquiera de los procesadores durante la parte inicial del intervalo de bus como respuesta a una solicitud de primer nivel de dicho uno cualquiera de los procesadores que presentan una ponderación de primer nivel donde, para cada procesador del uno o más de los procesadores a los que se les ha concedido acceso durante la parte inicial del intervalo de bus, la ponderación de nivel asociada con una solicitud de nivel correspondiente se reduce para cada ranura de tiempo en la parte inicial del intervalo de bus en la que a un procesador se le ha concedido acceso, caracterizado porque el árbitro de bus está configurado además para reinicializar la ponderación de primer nivel del uno o más procesadores al principio de un intervalo (402) de calidad de servicio donde la longitud del intervalo de calidad de servicio no es igual a la longitud del intervalo de bus

Tipo: Resumen de patente/invención. Número de Solicitud: W06007460US.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 5775 MOREHOUSE DRIVE,SAN DIEGO, CALIFORNIA 92121.

Inventor/es: HOFMANN,RICHARD GERARD, GANASAN,JAYA PRAKASH SUBRAMANIAM, LOHMAN,TERENCE,J.

Fecha de Publicación: .

Fecha Concesión Europea: 30 de Septiembre de 2009.

Clasificación Internacional de Patentes:

- G06F13/362 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 13/00 Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16). › con control centralizado de acceso.

Clasificación PCT:

- G06F13/362 G06F 13/00 […] › con control centralizado de acceso.

Fragmento de la descripción:

Esquema de arbitraje de acceso a bus.

Antecedentes

La presente invención se refiere en general a sistemas de procesamiento y, más específicamente, a un esquema de arbitraje de acceso a bus en un sistema de procesamiento.

Los ordenadores han revolucionado la industria electrónica permitiendo llevar a cabo tareas de procesamiento sofisticadas pulsando solamente algunas teclas. Estas tareas sofisticadas incluyen un número increíblemente elevado de componentes complejos que se comunican entre sí de una manera rápida y eficaz utilizando un bus. Un bus es un canal o trayectoria entre componentes de un ordenador o de otro dispositivo computacional.

Muchos buses se han implementado tradicionalmente como buses compartidos. Un bus compartido proporciona un medio para que cualquier número de componentes se comuniquen a través de una trayectoria o canal común. Recientemente, la tecnología de buses compartidos se ha sustituido en gran medida por conexiones de conmutación punto a punto. Las conexiones de conmutación punto a punto proporcionan una conexión directa entre dos componentes del bus cuando están comunicándose entre sí. Pueden utilizarse múltiples enlaces directos para permitir que varios componentes se comuniquen al mismo tiempo. Puede utilizarse un árbitro de bus para gestionar las comunicaciones a través del bus.

Un ordenador que implementa una arquitectura de bus puede incluir cualquier número de componentes de procesamiento conectados a uno o más recursos compartidos, tal como memoria. Uno o más procesadores (control maestro del bus) puede iniciar una transacción de bus solicitando acceso a partir del árbitro de bus. El árbitro de bus determina la secuencia en la que se concederá a los procesadores acceso al bus en base a un algoritmo predeterminado. En el pasado se han implementado varios esquemas de arbitraje de acceso a bus para gestionar estas transacciones. Un enfoque bastante común es un esquema de arbitraje mediante turnos rotativos el cual asigna ancho de banda de manera equitativa a todos los componentes de procesamiento, pero no tiene noción de requisitos de latencia. Otro enfoque común es un esquema de arbitraje de prioridad fija que tiene alguna noción de requisitos de latencia pero que degrada severamente a los procesadores de baja prioridad que pueden requerir un gran ancho de banda. La multiplexación por división de tiempo es probablemente una mejor solución que un esquema de arbitraje basado en prioridad fija o en turnos rotativos, pero es difícil predecir cuándo un procesador particular puede requerir acceso al bus. Por consiguiente, en la técnica existe la necesidad de un esquema de arbitraje de acceso a bus que proporcione la capacidad de asignar ancho de banda manteniendo al mismo tiempo requisitos de latencia para los procesadores en el bus. El documento US 2003/0074507 describe un procedimiento y aparato para planificar que un recurso cumpla con garantías de calidad de servicio.

En un aspecto de la presente invención, se proporciona un sistema de procesamiento, que comprende:

En un aspecto de la presente invención, se proporciona un procedimiento de arbitraje entre una pluralidad de procesadores que solicitan acceso a un bus, que comprende:

Breve descripción de los dibujos

La fig. 1 es un diagrama de bloques conceptual que ilustra un ejemplo de un sistema de procesamiento;

la fig. 2 es un diagrama conceptual que ilustra la distribución de tiempo de un esquema de arbitraje de acceso a bus que puede soportar requisitos de gran ancho de banda para varios procesadores;

la fig. 3 es un diagrama conceptual que ilustra el funcionamiento de un esquema de arbitraje de acceso a bus que puede soportar requisitos de gran ancho de banda para varios procesadores;

la fig. 4 es un diagrama conceptual que ilustra la distribución de tiempo de un esquema de arbitraje de acceso a bus que puede soportar requisitos de latencia y de gran ancho de banda para varios procesadores; y

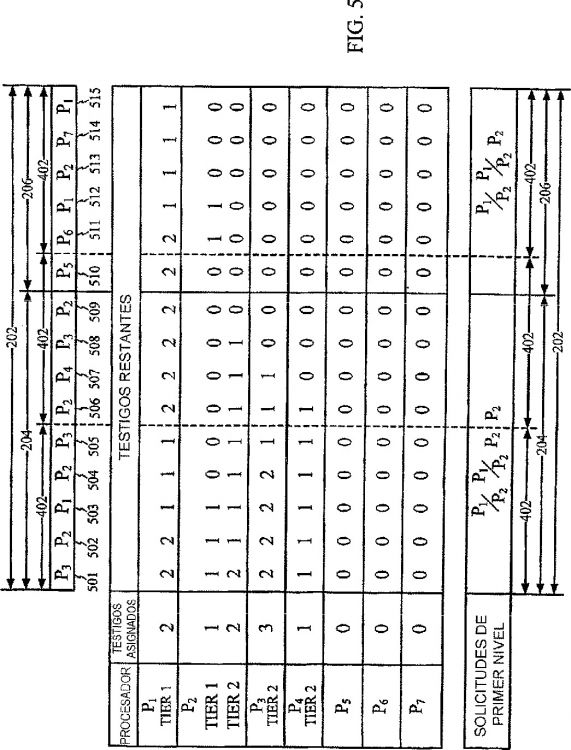

la fig. 5 es un diagrama conceptual que ilustra el funcionamiento de un esquema de arbitraje de acceso a bus que puede soportar requisitos de latencia y de gran ancho de banda para varios procesadores.

Descripción detallada

La fig. 1 es un diagrama de bloques conceptual que ilustra un ejemplo de un sistema de procesamiento. El sistema 100 de procesamiento puede ser un ordenador, o residir en un ordenador, o cualquier otro sistema capaz de procesar, recuperar y almacenar información. El sistema 100 de procesamiento puede ser un sistema independiente o, como alternativa, estar embebido en un dispositivo, tal como un teléfono inalámbrico, un asistente personal digital (PDA), un ordenador personal (PC), un ordenador portátil, etc.

El sistema 100 de procesamiento se muestra con varios procesadores 102a a 102c que pueden acceder a la memoria 104 a través de un bus 110, pero puede estar configurado con cualquier número de procesadores dependiendo de la aplicación particular y de las limitaciones globales de diseño. Cada procesador puede implementarse como cualquier tipo de componente de control maestro de bus incluyendo, a modo de ejemplo, un microprocesador, un procesador de señales digitales (DSP), un procesador gráfico de vídeo, un procesador de módem, o cualquier otro componente de procesamiento de información. La memoria 104 puede ser un controlador de memoria, una memoria caché, una memoria apilada o cualquier otro componente que pueda recuperar o almacenar información.

Un árbitro 108 de bus puede utilizarse para conceder a los procesadores 102a a 102c acceso al bus. El bus 110 puede implementarse con conexiones de conmutación punto a punto a través de una interconexión 106 de bus. En esta configuración, el árbitro 108 de bus configura la interconexión 106 de bus para proporcionar una conexión directa entre uno de los procesadores y la memoria 104. Múltiples enlaces directos de la interconexión 106 de bus pueden utilizarse para permitir que los demás procesadores se comuniquen con otros dispositivos esclavos...

Reivindicaciones:

1. Un sistema de procesamiento, que comprende:

2. El sistema de procesamiento según la reivindicación 1, en el que el árbitro (108) de bus está configurado además para conceder acceso al bus a dicho uno cualquiera de los procesadores (102) como respuesta a una solicitud del mismo durante la parte (206) restante del intervalo (202) de bus que sigue a la parte (204) inicial del intervalo de bus.

3. El sistema de procesamiento según la reivindicación 2, en el que el árbitro (108) de bus está configurado además para conceder acceso al bus a dicho uno cualquiera de los procesadores (102) durante la parte (206) restante del intervalo (202) de bus basándose en un esquema de turnos rotativos.

4. El sistema de procesamiento según la reivindicación 1, en el que el árbitro (108) de bus está configurado además para establecer la duración del intervalo (202) de bus.

5. El sistema de procesamiento según la reivindicación 1, en el que la parte (204) inicial del intervalo (202) de bus termina cuando la ponderación de segundo nivel de cada procesador del uno o más procesadores (102) se reduce a cero.

6. El sistema de procesamiento según la reivindicación 5, en el que el árbitro (108) de bus está configurado además para fijar la ponderación de segundo nivel para cada procesador del uno o más procesadores (102) al principio de cada uno de los intervalos (202) de bus.

7. El sistema de procesamiento según la reivindicación 1, en el que la ponderación de segundo nivel comprende el número de concesiones de acceso a bus requerido durante el intervalo (202) de bus por el procesador (102) al que está asignada la ponderación de segundo nivel.

8. El sistema de procesamiento según la reivindicación 1, en el que la ponderación de segundo nivel comprende el número de bits de datos requeridos durante el intervalo (202) de bus por el procesador (102) al que está asignada la ponderación de segundo nivel.

9. El sistema de procesamiento según la reivindicación 1, en el que el árbitro (108) de bus determina la duración del intervalo (402) de calidad de servicio.

10. El sistema de procesamiento según la reivindicación 1, en el que el árbitro (108) de bus está configurado además para establecer la duración del intervalo (402) de calidad de servicio.

11. El sistema de procesamiento según la reivindicación 1, en el que el árbitro (108) de bus está configurado además para arbitrar entre el uno o más de los procesadores (102) que solicitan acceso al bus (110) concediendo acceso al bus a un procesador del uno o más de los procesadores solicitantes mediante turnos rotativos si ninguno de los procesadores solicitantes tiene una ponderación de primer o de segundo nivel.

12. El sistema de procesamiento según la reivindicación 1, en el que uno o más de los procesadores (102) está tanto en el primer como en el segundo nivel.

13. Un procedimiento de arbitraje entre una pluralidad de procesadores (102) que solicitan acceso a un bus (110), que comprende:

14. El procedimiento según la reivindicación 13, que comprende además conceder acceso al bus a dicho uno cualquiera de los procesadores (102) como respuesta a una solicitud del mismo durante la parte (206) restante del intervalo (202) de bus que sigue a la parte (204) inicial del intervalo de bus.

15. El procedimiento según la reivindicación 14, en el que la concesión de acceso al bus a dicho uno cualquiera de los procesadores (102) durante la parte (206) restante del intervalo (202) de bus se basa en un esquema de turnos rotativos.

16. El procedimiento según la reivindicación 13, que comprende además establecer la duración del intervalo (202) de bus.

17. El procedimiento según la reivindicación 13, en el que se concede acceso al bus al procesador (102) del uno o más procesadores con la ponderación de segundo nivel más alta, comprendiendo además el procedimiento reducir la ponderación de segundo nivel de tal procesador después de haberle concedido acceso al bus.

18. El procedimiento según la reivindicación 17, en el que la parte (204) inicial del intervalo (202) de bus termina cuando la ponderación de segundo nivel de cada procesador del uno o más procesadores se reduce a cero.

19. El procedimiento según la reivindicación 13, en el que la ponderación de segundo nivel comprende el número de concesiones de acceso a bus requerido durante el intervalo (202) de bus por el procesador (102) al que está asignada la ponderación de segundo nivel.

20. El procedimiento según la reivindicación 13, en el que la ponderación de segundo nivel comprende el número de bits de datos requeridos durante el intervalo (202) de bus por el procesador (102) al que está asignada la ponderación de segundo nivel.

21. El procedimiento según la reivindicación 13, que comprende además establecer la duración del intervalo (402) de calidad de servicio.

22. El procedimiento según la reivindicación 13, en el que el arbitraje entre el uno o más de los procesadores (102) que solicitan acceso al bus se lleva a cabo mediante turnos rotativos si ninguno de los procesadores solicitantes tiene una ponderación de primer o de segundo nivel.

23. El procedimiento según la reivindicación 13, en el que la asignación de la ponderación de primer nivel a cada uno de los procesadores (102) en el primer nivel y la asignación de la ponderación de segundo nivel a cada uno de los procesadores en el segundo nivel comprende asignar un primera y una segunda ponderación al mismo de entre los procesadores.

Patentes similares o relacionadas:

Solución Ethernet universal, del 2 de Octubre de 2019, de SCHNEIDER ELECTRIC INDUSTRIES SAS: Un circuito integrado monolítico , que comprende: al menos un núcleo de procesador de aplicaciones utilizable para ejecutar una aplicación industrial y código de […]

Sistema de transmisión y recepción de datos, del 10 de Abril de 2019, de LSIS Co., Ltd: Un sistema de comunicación que comprende: módulos esclavos configurados para enviar una señal de respuesta correspondiente a una señal […]

Método para configurar automáticamente una ID en una comunicación en anillo UART, del 1 de Febrero de 2017, de LSIS Co., Ltd: Un método para configurar automáticamente ID en comunicación de anillo UART en la que se forma una maestra y se forma una pluralidad de esclavas […]

Arbitrador de espacio de datos, del 14 de Septiembre de 2016, de MICROCHIP TECHNOLOGY INCORPORATED: Un procesador digital, que comprende: un bus maestro (110; M0) por defecto que tiene una prioridad más alta en un modo por defecto; una pluralidad de buses maestros […]

Establecimiento de llamada de telecomunicación de medios mixtos, del 18 de Marzo de 2016, de 3G Licensing S.A: Estación móvil apta para videotelefonía en respuesta a una interrupción de una llamada en curso de telecomunicaciones de medios mixtos, comprendiendo […]

Establecimiento de llamada de telecomunicación de medios mixtos, del 18 de Marzo de 2016, de 3G Licensing S.A: Estación móvil apta para videotelefonía en respuesta a una interrupción de una llamada en curso de telecomunicaciones de medios mixtos, comprendiendo […]

Método de control de acceso a medios para un sistema de bus y un dispositivo de comunicaciones, del 10 de Junio de 2013, de ROBERT BOSCH GMBH: Método de control de acceso a medios, para el control de un acceso de una estación participante de unsistema de bus a un segundo canal […]

Procedimiento para la transmisión de datos entre estaciones de usuarios de un sistema de bus, del 10 de Mayo de 2013, de ROBERT BOSCH GMBH: Procedimiento para la transmisión de datos (b1) entre estaciones de usuarios de un sistema de bus através de un primer canal del sistema de bus […]

MÓDULO DE ENTRADAS Y SALIDAS PARA SISTEMAS DE MONITORIZACIÓN Y CONTROL DE VEHÍCULOS FERROVIARIOS, del 8 de Febrero de 2013, de CAF POWER & AUTOMATION, S.L.U: Módulo de entradas y salidas para sistemas de monitorización y control de vehículos ferroviarios, constituido por una placa de conexiones que presenta unas ranuras de […]

MÓDULO DE ENTRADAS Y SALIDAS PARA SISTEMAS DE MONITORIZACIÓN Y CONTROL DE VEHÍCULOS FERROVIARIOS, del 8 de Febrero de 2013, de CAF POWER & AUTOMATION, S.L.U: Módulo de entradas y salidas para sistemas de monitorización y control de vehículos ferroviarios, constituido por una placa de conexiones que presenta unas ranuras de […]