DISPOSIÓN DE CIRCUITOS CON CONEXIÓN BONDEADA.

Disposición de circuitos con un sustrato (2) que presenta circuitos impresos (22,

24, 26), por lo menos un primer componente semiconductor de potencia (4) y una conexión bondeada (5) asignada, presentando el primer componente semiconductor de potencia (4) una primera superficie de contacto de carga (40) y una segunda superficie de contacto de carga (42) de la misma polaridad, caracterizada porque la conexión bondeada (5) presenta un número impar N de hilos de bondeo (50, 52, 54), porque la primera mitad (50) de los N-1 hilos de bondeo alcanza desde un primer circuito impreso (22) del sustrato (2) la primera superficie de contacto de carga (40), porque la segunda mitad (52) de los N-1 hilos de bondeo alcanza desde este primer circuito impreso (22) la segunda superficie de contacto de carga (42), y el enésimo (54) hilo de bondeo, saliente del primer circuito impreso (22), presenta tanto en la primera superficie de contacto de carga (40) como en la segunda (42), por lo menos, una pata de bondeo (504, 524)

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E08021975.

Solicitante: SEMIKRON ELEKTRONIK GMBH & CO. KG.

Nacionalidad solicitante: Alemania.

Dirección: SIGMUNDSTRASSE 200 90431 NURNBERG ALEMANIA.

Inventor/es: LEDERER,MARCO, WALENTA,NICOLE.

Fecha de Publicación: .

Fecha Solicitud PCT: 18 de Diciembre de 2008.

Fecha Concesión Europea: 28 de Julio de 2010.

Clasificación Internacional de Patentes:

- H01L25/07N

- H01L25/18 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 25/00 Conjuntos consistentes en una pluralidad de dispositivos semiconductores o de otros dispositivos de estado sólido (dispositivos consistentes en una pluralidad de componentes de estado sólido formados en o sobre un sustrato común H01L 27/00; módulos fotovoltaicos o conjuntos de células fotovoltaicas H01L 31/042). › siendo los dispositivos de tipos previstos en varios subgrupos diferentes del mismo grupo principal de los grupos H01L 27/00 - H01L 51/00.

Clasificación PCT:

- H01L23/373 H01L […] › H01L 23/00 Detalles de dispositivos semiconductores o de otros dispositivos de estado sólido (H01L 25/00 tiene prioridad). › Refrigeración facilitada por el empleo de materiales particulares para el dispositivo.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Fragmento de la descripción:

La invención describe una disposición de circuitos con un sustrato, con circuitos impresos dispuestos encima, y por lo menos, un componente semiconductor de potencia dispuesto en por lo menos uno de dichos circuitos impresos. El componente semiconductor de potencia respectivo está conectado de forma electroconductora con un primer circuito impreso por medio de una conexión bondeada conocida, básicamente, desde hace mucho tiempo. Las disposiciones de circuitos de este tipo tienen aplicación preferente en módulos semiconductores de potencia.

Se conocen diferentes variantes de sustratos, preferentemente con un cuerpo básico aislante como, por ejemplo, como sustratos AMB (active metal braze), DCB (direct copper bonding) o IMS (insulated metal substrat). Encima de segundos circuitos impresos de estos sustratos están dispuestos los componentes semiconductores de potencia en unión, preferentemente, material y electroconductores.

Otros contactos eléctricos del componente semiconductor de potencia con otros circuitos impresos, por ejemplo con el primer circuito impreso se realizan, frecuentemente,

mediante conexiones bondeadas que para las conexiones de potencia presentan una pluralidad de hilos de bondeo individuales.Gracias al perfeccionamiento de los componentes semiconductores de potencia disminuye su dilatación lateral y, por lo tanto, su superficie con una intensidad de

corriente máxima admisible no cambiante. Se conocen, por

ejemplo, componentes semiconductores de potencia con dos superficies de contacto de carga de la misma polaridad, por ejemplo superficies de contacto emisoras de transistores de potencia. De este modo, para la solicitación del componente semiconductor de potencia es preferente si ambas superficies de contacto emisoras pueden ser alimentadas de corriente en forma homogénea.

La intensidad de corriente máxima admisible de la conexión eléctrica por medio de una conexión bondeada es determinada por el diámetro del hilo de bondeo individual y el número de hilos de bondeo. Por lo tanto, en una conexión bondeada puede ser necesario y apropiado disponer un número

impar de hilos de bondeo desde un circuito impreso del sustrato a las superficies de contacto de carga del transistor de potencia.En una pluralidad de aplicaciones, las superficies de contacto de carga de diodos de potencia están conectadas, adicionalmente, con las superficies de contacto de carga de los transistores de potencia por medio de la misma conexión bondeada. Con ello, el tamaño de la superficie de contacto de carga del diodo de potencia puede delimitar el número de hilos de bondeo por cada conexión bondeada.

El documento DE 10237561 da a conocer un diseño de circuitos impresos para módulos semiconductores de potencia que presentan componentes semiconductores de potencia y líneas de conexión sobre un sustrato aislado. Además, la descripción de la invención presenta conductores de conexión de corriente continua adyacentes y dispuestos paralelos y adyacentes estrechamente a la superficie del sustrato, y un

conductor de corriente alterna extendido igualmente paralelo a la superficie de sustrato.

La invención tiene el objetivo de indicar una disposición de circuitos que posibilita una alimentación homogénea de corriente de dos superficies de contacto de carga de la misma polaridad de un componente semiconductor de potencia con un número impar de hilos de bondeo en una conexión bondeada.

Dicho objetivo es conseguido de conformidad con la invención por medio de una disposición de circuitos con las características de la reivindicación 1. Las formas de realización preferentes se describen en las reivindicaciones secundarias.

El punto de partida de la disposición de circuitos de conformidad con la invención es un sustrato, preferentemente del tipo mencionado anteriormente. El mismo presenta una pluralidad de circuitos impresos, estando sobre un segundo de estos circuitos impresos dispuestos, por lo menos, un primer componente semiconductor de potencia. Éste, por lo menos, único componente semiconductor de potencia está conectado de forma electroconductora con un primer circuito impreso por medio de una conexión bondeada asignada.

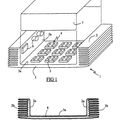

El primer componente semiconductor de potencia respectivo presenta una primera y una segunda superficie de contacto de carga de la misma polaridad. La conexión bondeada de la disposición de circuitos presenta un número impar N de hilos de bondeo, alcanzando la primera mitad de los hilos de bondeo N-1 de un primer circuito impreso del sustrato la primera superficie de contacto de carga. La

segunda mitad de los N-1 hilos de bondeo alcanza desde dicho

primer circuito impreso la segunda superficie de contacto de carga. De conformidad con la invención, el enésimo hilo de bondeo que parte del primer circuito impreso presenta tanto en la primera superficie de contacto de carga como en la segunda, por lo menos, una pata de bondeo.

Gracias a dicha configuración, se consigue una alimentación de corriente homogénea de ambas superficies de contacto de carga y, por lo tanto, de todo el componente semiconductor de potencia. Ello es necesario para conseguir la capacidad completa del componente semiconductor de potencia, también en el funcionamiento al límite de su capacidad. Los perfeccionamientos preferentes de dicha disposición de circuitos están mencionados en la descripción respectiva de los modelos de fabricación. Por lo demás, la solución de conformidad con la invención se explica en detalle en base a los modelos de fabricación de las figuras 1 a 3.

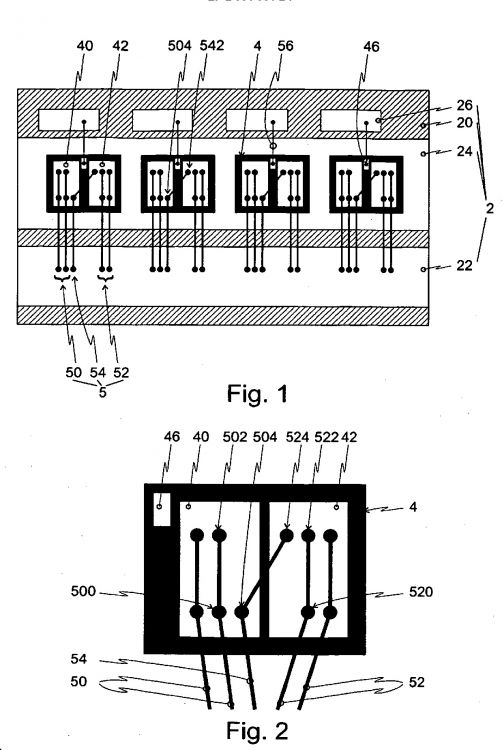

La figura 1 muestra una primera disposición de circuitos de conformidad con la invención.

La figura 2 muestra la disposición de los hilos de bondeo de una conexión bondeada de un componente semiconductor de potencia de una disposición de circuitos de conformidad con la invención.

La figura 3 muestra una segunda disposición de circuitos de conformidad con la invención.

La figura 1 muestra una primera disposición de circuitos de conformidad con la invención, configurada como conexión en paralelo de una pluralidad de interruptores de potencia, tal como es, por ejemplo, parte de un módulo semiconductor

de potencia. Aquí, la disposición de circuitos se compone,

por ejemplo, de un potencial de corriente alterna, un segundo potencial de corriente continua (24) de polaridad positiva y terceros circuitos impresos (26) conducen potencial de mando.

En el segundo circuito impreso (24) y conectados a éste de forma electroconductora están dispuestos primeros componentes semiconductores de potencia (4) conectados en paralelo, en este caso transistores de potencia de efecto de campo. Dichos transistores de potencia (4) presentan en su cara apartada respecto del sustrato (2) dos superficies de contacto de carga (40, 42) de la misma polaridad, y una superficie de contacto de mando (46). La superficie de contacto de mando (46) respectiva está conectada en forma electroconductora con un tercer circuito impreso (26) asignado del sustrato (2) por medio de una conexión por hilo de bondeo (56).

La conexión electroconductora entre el primer circuito impreso (22) del sustrato (2) y las superficies de contacto de carga (40, 42) del transistor de potencia (4) respectivo está conformada, del mismo modo, en cada caso por medio de una conexión bondeada (5). En este caso, debido a que ello es suficiente para la intensidad de corriente máxima admisible de la conexión, la conexión bondeada (5) presenta un número impar de hilos de bondeo (50, 52, 54). La primera mitad (52) de cuatro de estos cinco hilos de bondeo es suficiente para la primera superficie de contacto de carga

(40) del transistor de potencia (4) y presenta sobre la misma dos patas de bondeo (500, 502) por cada hilo de bondeo. La segunda mitad (52) de cuatro de estos cinco hilos

de bondeo es suficiente para la segunda superficie de

contacto de carga (42) del transistor de potencia (4) y presenta sobre la misma dos patas de bondeo (520, 522) por cada hilo de bondeo.

De conformidad con la invención, el quinto de hilo de bondeo (54) llega desde el primer circuito impreso (22) a la primera superficie de contacto de carga (40) del transistor de potencia (4) y presenta sobre la misma una pata de bondeo (504). Además, este quinto hilo de bondeo (54) llega hasta la segunda superficie de contacto...

Reivindicaciones:

1. Disposición de circuitos con un sustrato (2) que presenta circuitos impresos (22, 24, 26), por lo menos un primer componente semiconductor de potencia (4) y una conexión bondeada (5) asignada, presentando el primer componente semiconductor de potencia (4) una primera superficie de contacto de carga (40) y una segunda superficie de contacto de carga (42) de la misma polaridad, caracterizada porque la conexión bondeada (5) presenta un número impar N de hilos de bondeo (50, 52, 54), porque la primera mitad (50) de los N-1 hilos de bondeo alcanza desde un primer circuito impreso (22) del sustrato (2) la primera superficie de contacto de carga (40), porque la segunda mitad (52) de los N-1 hilos de bondeo alcanza desde este primer circuito impreso (22) la segunda superficie de contacto de carga (42), y el enésimo (54) hilo de bondeo, saliente del primer circuito impreso (22), presenta tanto en la primera superficie de contacto de carga (40) como en la segunda (42), por lo menos, una pata de bondeo (504, 524).

2. Disposición de circuitos según la reivindicación 1, en la que el primer componente semiconductor de potencia (4) es un transistor de potencia.

3. Disposición de circuitos según la reivindicación 1, en la que el sustrato (2) es un sustrato aislante con una pluralidad de circuitos impresos (22, 24, 26) dispuestos sobre una superficie y el, por lo menos, único componente semiconductor de potencia (4) está conectado en unión material y en forma electroconductora con un segundo circuito impreso (24).

4. Disposición de circuitos según la reivindicación 1, en la que la conexión bondeada (5) conecta, en cada caso, el

5. Disposición de circuitos según la reivindicación 4, en la que el segundo componente semiconductor de potencia primer circuito impreso (22) con el primer componente semiconductor de potencia (4) y un segundo componente semiconductor de potencia (7).5

(7) es un diodo de potencia.

Patentes similares o relacionadas:

Placa de circuito impreso, en particular para un módulo de electrónica de potencia, que comprende un sustrato eléctricamente conductor, del 12 de Junio de 2019, de A.B. Mikroelektronik Gesellschaft mit beschränkter Haftung: Placa de circuito impreso (1a, 1b, 1c), en particular para un módulo de electrónica de potencia , que comprende un sustrato eléctricamente conductor con un elemento […]

Procedimiento de interconexión eléctrica en tres dimensiones entre chips electrónicos encapsulados o entre un chip electrónico encapsulado y un circuito impreso, del 9 de Mayo de 2018, de 3D PLUS: Procedimiento de interconexión en tres dimensiones para al menos dos cápsulas plásticas de encapsulado conteniendo cada una al menos un chip electrónico , […]

MODULOS DE MEMORIA EN ESTADO SOLIDO Y DISPOSITIVOS DE MEMORIA QUE COMPRENDEN TALES MODULOS., del 16 de Mayo de 1995, de MATRA MARCONI SPACE FRANCE: MODULO DE MEMORIA QUE COMPRENDE SOBRE UN SUSTRATO DE INTERCONEXION, VARIAS PULGAS DE MEMORIA DE SEMICONDUCTORES DE FORMA ALARGADA CUYAS SALIDAS ESTAN LOCALIZADAS EN LOS EXTREMOS. […]

CAJA PARA CONVERTIDOR DE POTENCIA, del 16 de Octubre de 2008, de ALSTOM: Caja para convertidor de potencia, destinada especialmente a equipar una cadena de tracción de un vehículo ferroviario, que incluye módulos […]

CAJA PARA CONVERTIDOR DE POTENCIA, del 16 de Octubre de 2008, de ALSTOM: Caja para convertidor de potencia, destinada especialmente a equipar una cadena de tracción de un vehículo ferroviario, que incluye módulos […]

DISPOSITIVO ELECTRONICO DE POTENCIA, del 16 de Mayo de 2008, de ALSTOM HOLDINGS: Dispositivo electrónico de potencia que comprende: - una plantilla conductora , - una primera disposición plana de circuitos semi-conductores que descansan sobre la plantilla […]

DISPOSITIVO ELECTRONICO DE POTENCIA, del 16 de Mayo de 2008, de ALSTOM HOLDINGS: Dispositivo electrónico de potencia que comprende: - una plantilla conductora , - una primera disposición plana de circuitos semi-conductores que descansan sobre la plantilla […]

![]() MODULO SEMICONDUCTOR DE POTENCIA CON CONTACTO A PRESION, del 16 de Mayo de 2008, de SEMIKRON ELEKTRONIK GMBH, PATENTABTELUNG: Módulo de semiconductores de potencia, compuesto de una carcasa, un sustrato cerámico 2, áreas de contacto 3 configuradas y electroconductoras […]

MODULO SEMICONDUCTOR DE POTENCIA CON CONTACTO A PRESION, del 16 de Mayo de 2008, de SEMIKRON ELEKTRONIK GMBH, PATENTABTELUNG: Módulo de semiconductores de potencia, compuesto de una carcasa, un sustrato cerámico 2, áreas de contacto 3 configuradas y electroconductoras […]

MODULO ELECTRONICO DE POTENCIA Y PROCEDIMIENTO DE FABRICACION DEL MISMO, del 16 de Abril de 2008, de SAGEM SA: Módulo que comprende: un substrato metálico a base de aluminio; al menos una barra que constituye la conexión equipotential de material a base […]

MODULO ELECTRONICO DE POTENCIA Y PROCEDIMIENTO DE FABRICACION DEL MISMO, del 16 de Abril de 2008, de SAGEM SA: Módulo que comprende: un substrato metálico a base de aluminio; al menos una barra que constituye la conexión equipotential de material a base […]

![]() MODULO DE SEMICONDUCTORES DE POTENCIA MODULAR, del 16 de Agosto de 2007, de SEMIKRON ELEKTRONIK GMBH PATENTABTEILUNG: Módulo de semiconductores de potencia para ser montado en un cuerpo plano compuesto por un gran número de módulos de piezas , que a su vez están compuestos por […]

MODULO DE SEMICONDUCTORES DE POTENCIA MODULAR, del 16 de Agosto de 2007, de SEMIKRON ELEKTRONIK GMBH PATENTABTEILUNG: Módulo de semiconductores de potencia para ser montado en un cuerpo plano compuesto por un gran número de módulos de piezas , que a su vez están compuestos por […]