METODO Y DISPOSITIVO PARA EL MUESTREO DE DATOS DIGITALES EN UNA TRANSMISION SINCRONIZADA, CONSERVANDO LA INTEGRIDAD BINARIA.

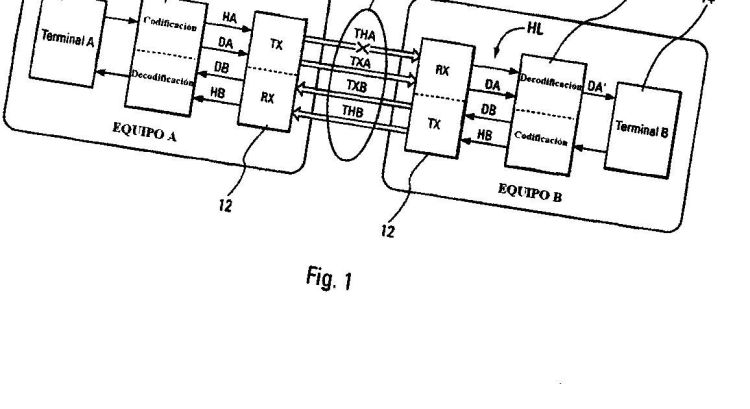

Procedimiento de muestreo, por medio de un reloj local HLS, de datos secuenciados por un reloj HA y transmitidos con el reloj HA,

desde un equipo A a un equipo B, con mantenimiento de la integridad binaria, que contiene al menos dos fases repetidas en alternancia - una fase (41) de funcionamiento libre durante la cual el equipo B muestrea los datos por medio del reloj local HLS, funcionando este reloj de manera autónoma, - una fase (42) de desincronización del reloj local HLS con respecto al reloj HA; durante la cual el reloj local HLS, que muestra los datos transmitidos, es sincronizado por el reloj HA que secuencia los datos siendo esta sincronización realizada, sin producir discontinuidad en el reloj local HLS, determinando si el frente ascendente del reloj local HLS está adelantado o atrasado con respecto al frente ascendente del reloj HA y - acortando la duración del reloj local HLS durante un ciclo de reloj si el frente ascendente del reloj local HLS está atrasado con respecto al frente del reloj HA, - alargando la duración del reloj local HLS durante un ciclo de reloj si el reloj local HLS está adelantado con respecto al reloj HA, de manera que los relojes HLS y HA sean sincronizados en el siguiente ciclo: siendo definida la frecuencia de ejecución de la etapa de sincronización de manera que garantice que, teniendo en cuenta precisiones de los relojes HA y HLS, el intervalo entre los frentes ascendentes de ambos relojes no sea superior a un semiperíodo del reloj HA.

Tipo: Resumen de patente/invención.

Solicitante: THALES.

Nacionalidad solicitante: Francia.

Dirección: 45, RUE DE VILLIERS,92200 NEUILLY SUR SEINE.

Inventor/es: COURANT,PIERRE THALES INTELLECTUAL PROPERTY, MARRON,CHRISTOPHE THALES INTELLECTUAL PROPERTY.

Fecha de Publicación: .

Fecha Solicitud PCT: 2 de Marzo de 2005.

Fecha Concesión Europea: 10 de Octubre de 2007.

Clasificación PCT:

- G06F1/12 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 1/00 Detalles no cubiertos en los grupos G06F 3/00 - G06F 13/00 y G06F 21/00 (arquitecturas de computadores con programas almacenados de propósito general G06F 15/76). › Sincronización de las diferentes señales de reloj.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Patentes similares o relacionadas:

Método y sistema para generación de señal multipunto con portadoras locales sincronizadas en fase, del 3 de Abril de 2019, de Blue Danube Systems, Inc: Un método para distribuir señales sinusoidales, que comprende: aplicar señales sinusoidales de primera y segunda entrada con frecuencia portadora f a las entradas […]

Aparato y método de compensación de desfase de reloj, del 19 de Febrero de 2014, de MOSAID TECHNOLOGIES INCORPORATED: Circuito de sincronización para resincronizar datos desde un reloj de entrada a un reloj de salida, estando caracterizado el circuito porque presenta: un primer circuito […]

Método de intercambio de información entre unidades digitales en un sistema distribuido, del 2 de Mayo de 2012, de IMA Industria Macchine Automatiche S.p.A: Método de intercambio de información entre unidades digitales en un sistema distribuido, comprendiendo dicho sistema distribuido una unidad maestra […]

Método de intercambio de información entre unidades digitales en un sistema distribuido, del 2 de Mayo de 2012, de IMA Industria Macchine Automatiche S.p.A: Método de intercambio de información entre unidades digitales en un sistema distribuido, comprendiendo dicho sistema distribuido una unidad maestra […]

ACTIVACIÓN SELECTIVA DE DISPOSITIVOS DE RF, del 9 de Junio de 2011, de INTELLEFLEX CORPORATION: Método que es para activar un dispositivo y comprende los pasos de: recibir un código de activación , teniendo el código de activación un campo de […]

RELOJ SIN INTERRUPCIONES, del 10 de Marzo de 2011, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): La unidad que comprende: una fuente de reloj (CLK1, CLK2) para generar una señal de fuente de reloj (CLK10, CLK20), un primer puerto (BD11, BD21) para comunicarse […]

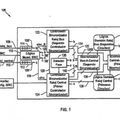

SISTEMA Y METODO PARA COMPENSAR UNA OBLICUIDAD ENTRE UNA PRIMERA SEÑAL DE RELOJ Y UNA SEGUNDA SEÑAL DE RELOJ, del 16 de Agosto de 2007, de HEWLETT-PACKARD DEVELOPMENT COMPANY, L.P.: Sistema y método para compensar la oblicuidad en un sincronizador programable de reloj para efectuar la transferencia de datos entre unos primeros circuitos dispuestos […]

SISTEMA Y METODO PARA COMPENSAR UNA OBLICUIDAD ENTRE UNA PRIMERA SEÑAL DE RELOJ Y UNA SEGUNDA SEÑAL DE RELOJ, del 16 de Agosto de 2007, de HEWLETT-PACKARD DEVELOPMENT COMPANY, L.P.: Sistema y método para compensar la oblicuidad en un sincronizador programable de reloj para efectuar la transferencia de datos entre unos primeros circuitos dispuestos […]

AJUSTE DE FASE DE RELOJ ENTRE CIRCUITOS DE RELOJ DUPLICADOS., del 16 de Octubre de 2000, de AT&T CORP.: SEÑALES DE DISPOSICION DE POTENCIA DE FUGA ENTRE DOS SUBSISTEMAS DE MEDICION DE TIEMPO PARA AJUSTAR LA RELACION DE FASE ENTRE LOS SUBSISTEMAS DE MEDICION […]

DISPOSICION DE CIRCUITO PARA LIBERACION DE PERTURBACION DE UNA SEÑAL DE MARCOS DE IMPULSOS, del 16 de Enero de 1998, de SIEMENS AG: LA SEÑAL DE MARCOS DE IMPULSO, QUE APARECE SEGUN UNA CANTIDAD PREVIAMENTE DADA DE IMPULSOS (CLK) DE INTERVALO, SE CEDE A PARTIR DE UN CONTADOR (CT), QUE SE CONECTA […]